# PIC16F152XX Family Product Brief

### Introduction

The PIC16F152XX microcontroller family is available in 8/14/16/20/28/40/44-pin packages for cost-sensitive sensor and real-time control applications. The PIC16F152XX family's simplified feature set includes a 10-bit Analog-to-Digital Converter (ADC), Peripheral Pin Select (PPS), digital communication peripherals, timers, and waveform generators. This microcontroller family also provides memory features, such as the Memory Access Partition (MAP) to support users in data protection and bootloader applications, and a Device Information Area (DIA), which stores Fixed Voltage Reference (FVR) offset values to help improve ADC accuracy.

## PIC16F152XX Family Types

Table 1. Devices included in this data sheet

| Device      | Program Flash Memory<br>(bytes) | Data SRAM<br>(bytes) | Memory Access Partition/<br>Device Information Area | I/O Pins <sup>(1</sup> )/<br>Peripheral Pin Select | 8-Bit Timers with HLT/<br>16-Bit Timers <sup>(2)</sup> | 10-Bit PWM/<br>CCP | 10-Bit ADC Channels<br>(External/Internal) | MSSP | EUSART | SMBus Compatible I/O Pads | External Interrupt Pins | Interrupt-on-Change Pins | Watchdog Timer |

|-------------|---------------------------------|----------------------|-----------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|--------------------|--------------------------------------------|------|--------|---------------------------|-------------------------|--------------------------|----------------|

| PIC16F15213 | 3.5k                            | 256                  | Y/Y                                                 | 6/Y                                                | 1/2                                                    | 2/2                | 5/2                                        | 1    | 1      | N                         | 1                       | 6                        | Y              |

| PIC16F15214 | 7k                              | 512                  | Y/Y                                                 | 6/Y                                                | 1/2                                                    | 2/2                | 5/2                                        | 1    | 1      | N                         | 1                       | 6                        | Υ              |

| PIC16F15223 | 3.5k                            | 256                  | Y/Y                                                 | 12/Y                                               | 1/2                                                    | 2/2                | 9/2                                        | 1    | 1      | Υ                         | 1                       | 12                       | Y              |

| PIC16F15224 | 7k                              | 512                  | Y/Y                                                 | 12/Y                                               | 1/2                                                    | 2/2                | 9/2                                        | 1    | 1      | Υ                         | 1                       | 12                       | Υ              |

| PIC16F15225 | 14k                             | 1024                 | Y/Y                                                 | 12/Y                                               | 1/2                                                    | 2/2                | 9/2                                        | 1    | 1      | Υ                         | 1                       | 12                       | Υ              |

| PIC16F15243 | 3.5k                            | 256                  | Y/Y                                                 | 18/Y                                               | 1/2                                                    | 2/2                | 12/2                                       | 1    | 1      | Υ                         | 1                       | 18                       | Υ              |

| PIC16F15244 | 7k                              | 512                  | Y/Y                                                 | 18/Y                                               | 1/2                                                    | 2/2                | 12/2                                       | 1    | 1      | Υ                         | 1                       | 18                       | Υ              |

| PIC16F15245 | 14k                             | 1024                 | Y/Y                                                 | 18/Y                                               | 1/2                                                    | 2/2                | 12/2                                       | 1    | 1      | Υ                         | 1                       | 18                       | Υ              |

| PIC16F15254 | 7k                              | 512                  | Y/Y                                                 | 25/Y                                               | 1/2                                                    | 2/2                | 17/2                                       | 1    | 1      | Υ                         | 1                       | 25                       | Y              |

| PIC16F15255 | 14k                             | 1024                 | Y/Y                                                 | 25/Y                                               | 1/2                                                    | 2/2                | 17/2                                       | 1    | 1      | Υ                         | 1                       | 25                       | Υ              |

| PIC16F15256 | 28k                             | 2048                 | Y/Y                                                 | 25/Y                                               | 1/2                                                    | 2/2                | 17/2                                       | 1    | 1      | Υ                         | 1                       | 25                       | Y              |

| PIC16F15274 | 7k                              | 512                  | Y/Y                                                 | 36/Y                                               | 1/2                                                    | 2/2                | 28/2                                       | 1    | 1      | Υ                         | 1                       | 36                       | Υ              |

| PIC16F15275 | 14k                             | 1024                 | Y/Y                                                 | 36/Y                                               | 1/2                                                    | 2/2                | 28/2                                       | 1    | 1      | Υ                         | 1                       | 36                       | Y              |

| PIC16F15276 | 28k                             | 2048                 | Y/Y                                                 | 36/Y                                               | 1/2                                                    | 2/2                | 28/2                                       | 1    | 1      | Υ                         | 1                       | 36                       | Υ              |

- 1. Total I/O count includes one pin (MCLR) that is input only.

- 2. Timer0 can be configured as either an 8 or 16-bit timer.

### **Core Features**

- · C Compiler Optimized RISC Architecture

- · Operating Speed:

- DC 32 MHz clock input

- 125 ns minimum instruction time

- 16-Level Deep Hardware Stack

- · Low-Current Power-on Reset (POR)

- · Configurable Power-up Timer (PWRT)

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

### Memory

- · Up to 28 KB of Program Flash Memory

- · Up to 2 KB of Data SRAM Memory

- · Memory Access Partition (MAP): The Program Flash Memory can be partitioned into:

- Application Block

- Boot Block

- Storage Area Flash (SAF) Block

- · Programmable Code Protection and Write Protection

- · Device Information Area (DIA) Stores:

- Fixed Voltage Reference (FVR) measurement data

- Microchip unique identifier

- Device Characteristics Area (DCI) Stores:

- Program/erase row sizes

- Pin count details

- · Direct, Indirect, and Relative Addressing Modes

# **Operating Characteristics**

- · Operating Voltage Range:

- 1.8V to 5.5V

- Temperature Range:

- Industrial: -40°C to 85°C

- Extended: -40°C to 125°C

# **Power-Saving Functionality**

- · Sleep:

- Reduce device power consumption

- Reduce system electrical noise while performing ADC conversions

- Low-Power Mode Features:

- Sleep:

- < 900nA typical @ 3V/25°C (WDT enabled)</li>

- < 600nA typical @ 3V/25°C (WDT disabled)</li>

- Operating Current:

- 48µA typical @ 32 kHz, 3V/25°C

- < 1mA typical @ 4 MHz, 5V/25°C</li>

### **Digital Peripherals**

- Two Capture/Compare/PWM (CCP) modules:

- 16-bit resolution for Capture/Compare modes

- 10-bit resolution for PWM mode

- · Two Pulse-Width Modulators (PWM):

- 10-bit resolution

- Independent pulse outputs

- One Configurable 8/16-Bit Timer (TMR0)

- · One 16-Bit Timer (TMR1) with Gate Control

- One 8-Bit Timer (TMR2) with Hardware Limit Timer (HLT)

- One Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART):

- RS-232, RS-485, LIN compatible

- Auto wake-up on Start

- · One Master Synchronous Serial Port (MSSP):

- Serial Peripheral Interface (SPI) mode

- · Slave Select Synchronization

- Inter-Integrated Circuit (I<sup>2</sup>C) mode

- 7/10-bit addressing modes

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

- Device I/O Port Features:

- Up to 35 I/O pins

- 1 input-only pin

- Individual I/O direction, open-drain, input threshold, slew rate, and weak pull-up control

- Interrupt-on-Change (IOC) on all pins

- One External Interrupt pin

# **Analog Peripherals**

- · Analog-to-Digital Converter (ADC):

- 10-bit resolution

- Up to 28 external input channels

- Two internal input channels

- Internal ADC oscillator (ADCRC)

- Operates in Sleep

- Selectable Auto-Conversion Trigger sources

- Fixed Voltage Reference (FVR):

- Selectable 1.024V, 2.048V, and 4.096V output levels

- Internally connected to ADC

# **Clocking Structure**

· High-Precision Internal Oscillator Block (HFINTOSC):

- Selectable frequencies up to 32 MHz

- ±2% at calibration

- Internal 31 kHz Oscillator (LFINTOSC)

- External High-Frequency Clock Input:

- Two External Clock (EC) power modes

# **Programming/Debug Features**

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with One Breakpoint via Two Pins

- Debug Integrated On-Chip

# 1. Packages

Table 1-1. Packages

| Device      | 8-Pin<br>SOIC | 8-Pin<br>DFN | 14-Pin<br>TSSOP | 14-Pin<br>SOIC | 16-Pin<br>VQFN<br>3x3x0.9 | 20-Pin<br>PDIP | 20-Pin<br>SSOP | 20-Pin<br>SOIC | 20-Pin<br>VQFN<br>3x3x0.9 | 28-Pin<br>SOIC | 28-Pin<br>SSOP | 28-Pin<br>VQFN<br>6x6x1 | 40-Pin<br>PDIP | 40-Pin<br>VQFN<br>5x5x0.9 | 44-Pin<br>TQFP<br>10x10x1 |

|-------------|---------------|--------------|-----------------|----------------|---------------------------|----------------|----------------|----------------|---------------------------|----------------|----------------|-------------------------|----------------|---------------------------|---------------------------|

| PIC16F15213 | •             | •            |                 |                |                           |                |                |                |                           |                |                |                         |                |                           |                           |

| PIC16F15214 | •             | •            |                 |                |                           |                |                |                |                           |                |                |                         |                |                           |                           |

| PIC16F15223 |               |              | •               | •              | •                         |                |                |                |                           |                |                |                         |                |                           |                           |

| PIC16F15224 |               |              | •               | •              | •                         |                |                |                |                           |                |                |                         |                |                           |                           |

| PIC16F15225 |               |              | •               | •              | •                         |                |                |                |                           |                |                |                         |                |                           |                           |

| PIC16F15243 |               |              |                 |                |                           | •              | •              | •              | •                         |                |                |                         |                |                           |                           |

| PIC16F15244 |               |              |                 |                |                           | •              | •              | •              | •                         |                |                |                         |                |                           |                           |

| PIC16F15245 |               |              |                 |                |                           | •              | •              | •              | •                         |                |                |                         |                |                           |                           |

| PIC16F15254 |               |              |                 |                |                           |                |                |                |                           | •              | •              | •                       |                |                           |                           |

| PIC16F15255 |               |              |                 |                |                           |                |                |                |                           | •              | •              | •                       |                |                           |                           |

| PIC16F15256 |               |              |                 |                |                           |                |                |                |                           | •              | •              | •                       |                |                           |                           |

| PIC16F15274 |               |              |                 |                |                           |                |                |                |                           |                |                |                         | •              | •                         | •                         |

| PIC16F15275 |               |              |                 |                |                           |                |                |                |                           |                |                |                         | •              | •                         | •                         |

| PIC16F15276 |               |              |                 |                |                           |                |                |                |                           |                |                |                         | •              | •                         | •                         |

# 2. Pin Diagrams

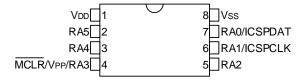

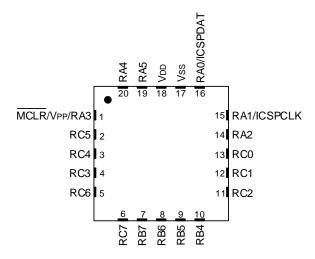

Figure 2-1. 8-Pin SOIC 8-Pin DFN

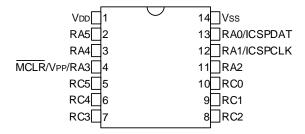

Figure 2-2. 14-Pin SOIC 14-Pin TSSOP

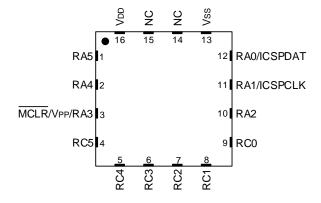

Figure 2-3. 16-Pin VQFN

**Note:** It is recommended that the exposed bottom pad be connected to  $V_{SS}$ , however it must not be the only  $V_{SS}$  connection to the device.

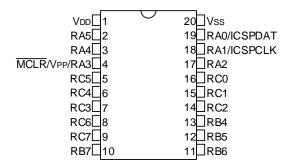

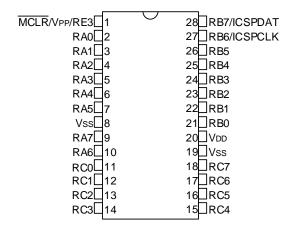

Figure 2-4. 20-Pin PDIP 20-Pin SOIC

20-Pin SSOP

Figure 2-5. 20-Pin VQFN

**Note:** It is recommended that the exposed bottom pad be connected to  $V_{SS}$ , however it must not be the only  $V_{SS}$  connection to the device.

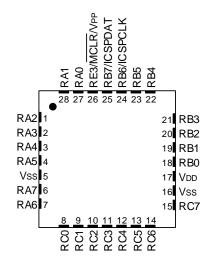

Figure 2-6. 28-Pin SSOP 28-Pin SOIC

Figure 2-7. 28-Pin VQFN

**Note:** It is recommended that the exposed bottom pad be connected to  $V_{SS}$ , however it must not be the only  $V_{SS}$  connection to the device.

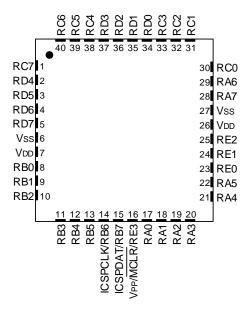

Figure 2-8. 40-Pin PDIP

| -            |      | <b>-</b>       |

|--------------|------|----------------|

| MCLR/Vpp/RE3 | 1 4  | 0□RB7/ICSPDAT  |

| RA0□         | 2 3  | 9□RB6/ICSPCLK  |

| RA1□         | 3 3  | 8 <b>□</b> RB5 |

| RA2□         | 4 3  | 7□RB4          |

| RA3          | 5 3  | 6 <b>□</b> RB3 |

| RA4□         | 6 3  | 5 <b>□</b> RB2 |

| RA5□         | 7 3  | 4□RB1          |

| RE0□         | 8 3  | 3 <b>□</b> RB0 |

| RE1□         | 9 3  | 2 Vdd          |

| RE2□         | 10 3 | 1□Vss          |

| VDD          | 11 3 | 0 <b>□</b> RD7 |

| Vss          | 12 2 | 9 <b>□</b> RD6 |

| RA7          | 13 2 | 8 <b>_</b> RD5 |

| RA6□         | 14 2 | 7□RD4          |

| RC0□         | 15 2 | 6□RC7          |

| RC1□         | 16 2 | 5□RC6          |

| RC2□         | 17 2 | 4□RC5          |

| RC3□         | 18 2 | 3□RC4          |

| RD0□         | 19 2 | 2☐RD3          |

| RD1□         | 20 2 | 1 RD2          |

|              |      |                |

Figure 2-9. 40-Pin VQFN

**Note:** It is recommended that the exposed bottom pad be connected to  $V_{SS}$ , however it must not be the only  $V_{SS}$  connection to the device.

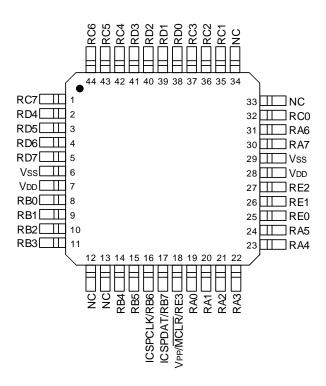

Figure 2-10. 44-Pin TQFP

**Pin Allocation Tables**

Table 3-1. 8-Pin Allocation Table

| I/O                | 8-Pin<br>SOIC<br>DFN | ADC                          | Reference   | Timers                                      | CCP                                        | 10-Bit<br>PWM | MSSP                                           | EUSART                                     | юс    | Interrupt          | Basic             |

|--------------------|----------------------|------------------------------|-------------|---------------------------------------------|--------------------------------------------|---------------|------------------------------------------------|--------------------------------------------|-------|--------------------|-------------------|

| RA0                | 7                    | ANA0                         | _           | _                                           | _                                          | _             | _                                              | RX1 <sup>(1)</sup><br>DT1 <sup>(1,3)</sup> | IOCA0 | _                  | ICSPDAT<br>ICDDAT |

| RA1                | 6                    | ANA1                         | VREF+ (ADC) | _                                           | _                                          | _             | SCL1 <sup>(1,3)</sup><br>SCK1 <sup>(1,3)</sup> | CK1 <sup>(1,3)</sup>                       | IOCA1 | _                  | ICSPCLK<br>ICDCLK |

| RA2                | 5                    | ANA2                         | _           | T0CKI <sup>(1)</sup>                        | _                                          | _             | SDA1 <sup>(1,3)</sup><br>SDI1 <sup>(1,3)</sup> | _                                          | IOCA2 | INT <sup>(1)</sup> | <del></del>       |

| RA3                | 4                    | _                            | _           | _                                           | _                                          | _             | SS1(1)                                         | _                                          | IOCA3 | _                  | MCLR<br>VPP       |

| RA4                | 3                    | ANA4                         | _           | T1G <sup>(1)</sup>                          | _                                          | _             | _                                              | _                                          | IOCA4 | _                  | CLKOUT            |

| RA5                | 2                    | ANA5<br>ADACT <sup>(1)</sup> | _           | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> | CCP1 <sup>(1)</sup><br>CCP2 <sup>(1)</sup> | _             | _                                              | _                                          | IOCA5 | _                  | CLKIN             |

| V <sub>DD</sub>    | 1                    | _                            | _           | _                                           | _                                          | _             | _                                              | _                                          | _     | _                  | V <sub>DD</sub>   |

| Vss                | 8                    | _                            | _           | _                                           | _                                          | _             | _                                              | _                                          | _     | _                  | Vss               |

| OUT <sup>(2)</sup> | _                    | _                            | _           | TMR0                                        | CCP1<br>CCP2                               | PWM3<br>PWM4  | SCL1<br>SCK1<br>SDA1<br>SDO1                   | TX1<br>DT1<br>CK1                          | _     | _                  | _                 |

#### Note:

- 1. This is a PPS remappable input signal. The input function may be moved from the default location shown to any PORTx pin.

- 2. All output signals shown in this row are PPS remappable.

- 3. This is a bidirectional signal. For normal operation, user software must map this signal to the same pin via the PPS input and PPS output registers.

Table 3-2. 14/16-Pin Allocation Table

| 1/0                | 14-Pin<br>SOIC<br>TSSOP | 16-Pin<br>VQFN | ADC                          | Reference   | Timers                                      | ССР                 | 10-Bit<br>PWM | MSSP                                               | EUSART                                     | юс    | Interrupt          | Basic                   |

|--------------------|-------------------------|----------------|------------------------------|-------------|---------------------------------------------|---------------------|---------------|----------------------------------------------------|--------------------------------------------|-------|--------------------|-------------------------|

| RA0                | 13                      | 12             | ANA0                         | _           | _                                           | _                   | _             | _                                                  | _                                          | IOCA0 | _                  | ICSPDAT<br>ICDDAT       |

| RA1                | 12                      | 11             | ANA1                         | VREF+ (ADC) | _                                           | _                   | _             | _                                                  | _                                          | IOCA1 | _                  | ICSPCLK<br>ICDCLK       |

| RA2                | 11                      | 10             | ANA2                         | _           | T0CKI <sup>(1)</sup>                        | _                   | _             | _                                                  | _                                          | IOCA2 | INT <sup>(1)</sup> | _                       |

| RA3                | 4                       | 3              | _                            | _           | _                                           | _                   | _             | _                                                  | _                                          | IOCA3 | _                  | MCLR<br>V <sub>PP</sub> |

| RA4                | 3                       | 2              | ANA4                         | _           | T1G <sup>(1)</sup>                          | _                   | _             | _                                                  | _                                          | IOCA4 | _                  | CLKOUT                  |

| RA5                | 2                       | 1              | ANA5                         | _           | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> | _                   | _             | _                                                  | _                                          | IOCA5 | _                  | CLKIN                   |

| RC0                | 10                      | 9              | _                            | _           | _                                           | _                   | _             | SCL1 <sup>(1,3,4)</sup><br>SCK1 <sup>(1,3,4)</sup> |                                            | IOCC0 |                    | _                       |

| RC1                | 9                       | 8              | _                            | _           | _                                           | _                   | _             | SDA1 <sup>(1,3,4)</sup><br>SDI1 <sup>(1,3,4)</sup> | _                                          | IOCC1 | _                  | _                       |

| RC2                | 8                       | 7              | ANC2<br>ADACT <sup>(1)</sup> | _           | _                                           | _                   | _             | _                                                  | _                                          | IOCC2 | _                  | _                       |

| RC3                | 7                       | 6              | ANC3                         | _           | _                                           | CCP2 <sup>(1)</sup> | _             | <del>SS1</del> (1)                                 | _                                          | IOCC3 | _                  | _                       |

| RC4                | 6                       | 5              | ANC4                         | _           | _                                           | _                   | _             | _                                                  | CK1 <sup>(1,3)</sup>                       | IOCC4 | _                  | _                       |

| RC5                | 5                       | 4              | ANC5                         | _           | _                                           | CCP1 <sup>(1)</sup> | _             | _                                                  | RX1 <sup>(1)</sup><br>DT1 <sup>(1,3)</sup> | IOCC5 | _                  | _                       |

| V <sub>DD</sub>    | 1                       | 16             | _                            | _           | _                                           | _                   | _             | _                                                  | _                                          | _     | _                  | V <sub>DD</sub>         |

| Vss                | 14                      | 13             | _                            | _           | _                                           | _                   | _             | _                                                  | _                                          | _     | _                  | Vss                     |

| OUT <sup>(2)</sup> | _                       | _              | _                            | _           | TMR0                                        | CCP1<br>CCP2        | PWM3<br>PWM4  | SCL1<br>SCK1<br>SDA1<br>SDO1                       | TX1<br>DT1<br>CK1                          | _     | _                  | _                       |

- 1. This is a PPS remappable input signal. The input function may be moved from the default location shown to any PORTx pin.

- 2. All output signals shown in this row are PPS remappable.

- 3. This is a bidirectional signal. For normal operation, user software must map this signal to the same pin via the PPS input and PPS output registers.

- 4. These pins can be configured for I<sup>2</sup>C or SMBus logic levels via the Rxyl2C registers. The SCL1/SDA1 signals may be assigned to these pins for expected operation. PPS assignments of these signals to other pins will operate; however, the logic levels will be standard TTL/ST as selected by the INLVL register.

Table 3-3. 20-Pin Allocation Table

| I/O | 20-Pin<br>PDIP<br>SSOP<br>SOIC | 20-Pin<br>VQFN | ADC  | Reference   | Timers               | CCP | 10-Bit<br>PWM | MSSP | EUSART | IOC   | Interrupt          | Basic                   |

|-----|--------------------------------|----------------|------|-------------|----------------------|-----|---------------|------|--------|-------|--------------------|-------------------------|

| RA0 | 19                             | 16             | ANA0 | _           | _                    | _   | _             | _    | _      | IOCA0 | _                  | ICSPDAT<br>ICDDAT       |

| RA1 | 18                             | 15             | ANA1 | VREF+ (ADC) | _                    | _   | _             | _    | _      | IOCA1 | _                  | ICSPCLK<br>ICDCLK       |

| RA2 | 17                             | 14             | ANA2 | _           | T0CKI <sup>(1)</sup> | _   | _             | _    | _      | IOCA2 | INT <sup>(1)</sup> | _                       |

| RA3 | 4                              | 1              | _    | _           | _                    | _   | _             | _    | _      | IOCA3 | _                  | MCLR<br>V <sub>PP</sub> |

| RA4 | 3                              | 20             | ANA4 | _           | T1G <sup>(1)</sup>   | _   | _             | _    | _      | IOCA4 | _                  | CLKOUT                  |

| con                | tinued                         |                |                              |           |                                             |                     |               |                                                    |                                            |       |           |                 |

|--------------------|--------------------------------|----------------|------------------------------|-----------|---------------------------------------------|---------------------|---------------|----------------------------------------------------|--------------------------------------------|-------|-----------|-----------------|

| I/O                | 20-Pin<br>PDIP<br>SSOP<br>SOIC | 20-Pin<br>VQFN | ADC                          | Reference | Timers                                      | CCP                 | 10-Bit<br>PWM | MSSP                                               | EUSART                                     | IOC   | Interrupt | Basic           |

| RA5                | 2                              | 19             | ANA5                         | _         | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> | _                   | _             | _                                                  | _                                          | IOCA5 | _         | CLKIN           |

| RB4                | 13                             | 10             | _                            | _         | _                                           | _                   | _             | SDA1 <sup>(1,3,4)</sup><br>SDI1 <sup>(1,3,4)</sup> | _                                          | IOCB4 | _         | _               |

| RB5                | 12                             | 9              | ANB5                         | _         | _                                           | _                   | _             | _                                                  | RX1 <sup>(1)</sup><br>DT1 <sup>(1,3)</sup> | IOCB5 | _         | _               |

| RB6                | 11                             | 8              | ANB6                         | _         | _                                           | _                   | _             | SCL1 <sup>(1,3,4)</sup><br>SCK1 <sup>(1,3,4)</sup> | _                                          | IOCB6 | _         | _               |

| RB7                | 10                             | 7              | ANB7                         | _         | _                                           | _                   | _             | _                                                  | CK1 <sup>(1,3)</sup>                       | IOCB7 | _         | _               |

| RC0                | 16                             | 13             | _                            | _         | _                                           | _                   | _             | _                                                  | _                                          | IOCC0 | _         | _               |

| RC1                | 15                             | 12             | _                            | _         | _                                           | _                   | _             | _                                                  | _                                          | IOCC1 | _         | _               |

| RC2                | 14                             | 11             | ANC2<br>ADACT <sup>(1)</sup> | _         | _                                           | _                   | _             | _                                                  | _                                          | IOCC2 | _         | _               |

| RC3                | 7                              | 4              | ANC3                         | _         | _                                           | CCP2 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC3 | _         | _               |

| RC4                | 6                              | 3              | ANC4                         | _         | _                                           | _                   | _             | _                                                  | _                                          | IOCC4 | _         | _               |

| RC5                | 5                              | 2              | ANC5                         | _         | _                                           | CCP1 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC5 | _         | _               |

| RC6                | 8                              | 5              | _                            | _         | _                                           | _                   | _             | SS1 <sup>(1)</sup>                                 | _                                          | IOCC6 | _         | _               |

| RC7                | 9                              | 6              | _                            | _         | _                                           | _                   | _             | _                                                  | _                                          | IOCC7 | _         | _               |

| V <sub>DD</sub>    | 1                              | 18             | _                            | _         | _                                           | _                   | _             | _                                                  | _                                          | _     | _         | V <sub>DD</sub> |

| Vss                | 20                             | 17             | _                            | _         | _                                           | _                   | _             | _                                                  | _                                          | _     | _         | Vss             |

| OUT <sup>(2)</sup> | _                              | _              | _                            | _         | TMR0                                        | CCP1<br>CCP2        | PWM3<br>PWM4  | SCL1<br>SCK1<br>SDA1<br>SDO1                       | TX1<br>DT1<br>CK1                          | _     | _         | _               |

- 1. This is a PPS remappable input signal. The input function may be moved from the default location shown to any PORTx pin.

- 2. All output signals shown in this row are PPS remappable.

- 3. This is a bidirectional signal. For normal operation, user software must map this signal to the same pin via the PPS input and PPS output registers.

- 4. These pins can be configured for I<sup>2</sup>C or SMBus logic levels via the Rxyl2C registers. The SCL1/SDA1 signals may be assigned to these pins for expected operation. PPS assignments of these signals to other pins will operate; however, the logic levels will be standard TTL/ST as selected by the INLVL register.

Table 3-4. 28-Pin Allocation Table

| I/O | 28-Pin<br>SOIC<br>SSOP | 28-Pin<br>VQFN | ADC  | Reference                | Timers               | CCP | 10-Bit<br>PWM | MSSP               | EUSART | IOC   | Interrupt | Basic  |

|-----|------------------------|----------------|------|--------------------------|----------------------|-----|---------------|--------------------|--------|-------|-----------|--------|

| RA0 | 2                      | 27             | ANA0 | _                        | _                    | _   | _             | _                  | _      | IOCA0 | _         | _      |

| RA1 | 3                      | 28             | ANA1 | _                        | _                    | _   | _             | _                  | _      | IOCA1 | _         | _      |

| RA2 | 4                      | 1              | ANA2 | _                        | _                    | _   | _             | _                  | _      | IOCA2 | _         | _      |

| RA3 | 5                      | 2              | ANA3 | V <sub>REF</sub> + (ADC) | _                    | _   | _             | _                  | _      | IOCA3 | _         | _      |

| RA4 | 6                      | 3              | _    | _                        | T0CKI <sup>(1)</sup> | _   | _             | _                  | _      | IOCA4 | _         | _      |

| RA5 | 7                      | 4              | ANA5 | _                        | _                    | _   | _             | SS1 <sup>(1)</sup> | _      | IOCA5 | _         | _      |

| RA6 | 10                     | 7              | _    | _                        | _                    | _   | _             | _                  | _      | IOCA6 | _         | CLKOUT |

| RA7 | 9                      | 6              | _    | _                        | _                    | _   | _             | _                  | _      | IOCA7 | _         | CLKIN  |

| con                | ntinued                |                |                              |           |                      |                     |               |                                                    |                                            |       |                    |                         |

|--------------------|------------------------|----------------|------------------------------|-----------|----------------------|---------------------|---------------|----------------------------------------------------|--------------------------------------------|-------|--------------------|-------------------------|

| I/O                | 28-Pin<br>SOIC<br>SSOP | 28-Pin<br>VQFN | ADC                          | Reference | Timers               | ССР                 | 10-Bit<br>PWM | MSSP                                               | EUSART                                     | ЮС    | Interrupt          | Basic                   |

| RB0                | 21                     | 18             | ANB0                         | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB0 | INT <sup>(1)</sup> | _                       |

| RB1                | 22                     | 19             | ANB1                         | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB1 | _                  | _                       |

| RB2                | 23                     | 20             | ANB2                         | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB2 | _                  | _                       |

| RB3                | 24                     | 21             | ANB3                         | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB3 | _                  | _                       |

| RB4                | 25                     | 22             | ANB4<br>ADACT <sup>(1)</sup> | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB4 | _                  | _                       |

| RB5                | 26                     | 23             | ANB5                         | _         | T1G <sup>(1)</sup>   | _                   | _             | _                                                  | _                                          | IOCB5 | _                  | _                       |

| RB6                | 27                     | 24             | _                            | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB6 | _                  | ICSPCLK<br>ICDCLK       |

| RB7                | 28                     | 25             | _                            | _         | _                    | _                   | _             | _                                                  | _                                          | IOCB7 | _                  | ICSPDAT<br>ICDDAT       |

| RC0                | 11                     | 8              | _                            | _         | T1CKI <sup>(1)</sup> | _                   | _             | _                                                  | _                                          | IOCC0 | _                  | _                       |

| RC1                | 12                     | 9              | _                            | _         | _                    | CCP2 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC1 | _                  | _                       |

| RC2                | 13                     | 10             | ANC2                         | _         | _                    | CCP1 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC2 | _                  | _                       |

| RC3                | 14                     | 11             | ANC3                         | _         | T2IN <sup>(1)</sup>  | _                   | _             | SCL1(1,3,4)<br>SCK1(1,3,4)                         | _                                          | IOCC3 | _                  | _                       |

| RC4                | 15                     | 12             | ANC4                         | _         | _                    | _                   | _             | SDA1 <sup>(1,3,4)</sup><br>SDI1 <sup>(1,3,4)</sup> | _                                          | IOCC4 | _                  | _                       |

| RC5                | 16                     | 13             | ANC5                         | _         | _                    | _                   | _             | _                                                  | _                                          | IOCC5 | _                  | _                       |

| RC6                | 17                     | 14             | ANC6                         | _         | _                    | _                   | _             | _                                                  | CK1 <sup>(1,3)</sup>                       | IOCC6 | _                  | _                       |

| RC7                | 18                     | 15             | ANC7                         | _         | _                    | _                   | _             | _                                                  | RX1 <sup>(1)</sup><br>DT1 <sup>(1,3)</sup> | IOCC7 | _                  | _                       |

| RE3                | 1                      | 26             | _                            | _         | _                    | _                   | _             | _                                                  | _                                          | IOCE3 | _                  | MCLR<br>V <sub>PP</sub> |

| V <sub>DD</sub>    | 20                     | 17             | _                            | _         | _                    | _                   | _             | _                                                  | _                                          | _     | _                  | V <sub>DD</sub>         |

| V <sub>SS</sub>    | 8<br>19                | 5<br>16        | _                            | _         | _                    | _                   | _             | _                                                  | _                                          | _     | _                  | V <sub>SS</sub>         |

| OUT <sup>(2)</sup> | _                      | _              | _                            | _         | TMR0                 | CCP1<br>CCP2        | PWM3<br>PWM4  | SCL1<br>SCK1<br>SDA1<br>SDO1                       | TX1<br>DT1<br>CK1                          | _     | _                  | _                       |

- 1. This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to the PPS input table in the device data sheet for details on which PORT pins may be used for this signal.

- 2. All output signals shown in this row are PPS remappable.

- 3. This is a bidirectional signal. For normal operation, user software must map this signal to the same pin via the PPS input and PPS output registers.

- 4. These pins can be configured for I<sup>2</sup>C or SMBus logic levels via the Rxyl2C registers. The SCL1/SDA1 signals may be assigned to these pins for expected operation. PPS assignments of these signals to other pins will operate; however, the logic levels will be standard TTL/ST as selected by the INLVL register.

#### Table 3-5. 40/44-Pin Allocation Table

| I/O | 40-Pin<br>PDIP | 40-Pin<br>VQFN | 44-Pin<br>TQFP | ADC  | Reference | Timers | ССР | 10-Bit<br>PWM | MSSP | EUSART | IOC   | Interrupt | Basic |

|-----|----------------|----------------|----------------|------|-----------|--------|-----|---------------|------|--------|-------|-----------|-------|

| RA0 | 2              | 17             | 19             | ANA0 | _         | _      | _   | _             | _    | _      | IOCA0 | _         | _     |

| RA1 | 3              | 18             | 20             | ANA1 | _         | _      | _   | _             | _    | _      | IOCA1 | _         | _     |

| RA2 | 4              | 19             | 21             | ANA2 | _         | _      | _   | _             | _    | _      | IOCA2 | _         | _     |

| co              | ntinued        |                |                |                              |             |                      |                     |               |                                                    |                                            |       |                    |                   |

|-----------------|----------------|----------------|----------------|------------------------------|-------------|----------------------|---------------------|---------------|----------------------------------------------------|--------------------------------------------|-------|--------------------|-------------------|

| I/O             | 40-Pin<br>PDIP | 40-Pin<br>VQFN | 44-Pin<br>TQFP | ADC                          | Reference   | Timers               | ССР                 | 10-Bit<br>PWM | MSSP                                               | EUSART                                     | IOC   | Interrupt          | Basic             |

| RA3             | 5              | 20             | 22             | ANA3                         | VREF+ (ADC) | _                    | _                   | _             | _                                                  | _                                          | IOCA3 | _                  | _                 |

| RA4             | 6              | 21             | 23             | _                            | _           | T0CKI <sup>(1)</sup> | _                   | _             | _                                                  | _                                          | IOCA4 | _                  | _                 |

| RA5             | 7              | 22             | 24             | ANA5                         | _           | _                    | _                   | _             | SS1 <sup>(1)</sup>                                 | _                                          | IOCA5 | _                  | _                 |

| RA6             | 14             | 29             | 31             | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | IOCA6 | _                  | CLKOUT            |

| RA7             | 13             | 28             | 30             | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | IOCA7 | _                  | CLKIN             |

| RB0             | 33             | 8              | 8              | ANB0                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB0 | INT <sup>(1)</sup> | _                 |

| RB1             | 34             | 9              | 9              | ANB1                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB1 | _                  | _                 |

| RB2             | 35             | 10             | 10             | ANB2                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB2 | _                  | _                 |

| RB3             | 36             | 11             | 11             | ANB3                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB3 | _                  | _                 |

| RB4             | 37             | 12             | 14             | ANB4<br>ADACT <sup>(1)</sup> | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB4 | _                  | _                 |

| RB5             | 38             | 13             | 15             | ANB5                         | _           | T1G <sup>(1)</sup>   | _                   | _             | _                                                  | _                                          | IOCB5 | _                  | _                 |

| RB6             | 39             | 14             | 16             | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB6 | _                  | ICSPCLK<br>ICDCLK |

| RB7             | 40             | 15             | 17             | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | IOCB7 | _                  | ICSPDAT<br>ICDDAT |

| RC0             | 15             | 30             | 32             | _                            | _           | T1CKI <sup>(1)</sup> | _                   | _             | _                                                  | _                                          | IOCC0 | _                  | _                 |

| RC1             | 16             | 31             | 35             | _                            | _           | _                    | CCP2 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC1 | _                  | _                 |

| RC2             | 17             | 32             | 36             | ANC2                         | _           | _                    | CCP1 <sup>(1)</sup> | _             | _                                                  | _                                          | IOCC2 | _                  | _                 |

| RC3             | 18             | 33             | 37             | ANC3                         | _           | T2IN <sup>(1)</sup>  | _                   | _             | SCL1 <sup>(1,3,4)</sup><br>SCK1 <sup>(1,3,4)</sup> | _                                          | IOCC3 | _                  | _                 |

| RC4             | 23             | 38             | 42             | ANC4                         | _           | _                    | _                   | _             | SDA1 <sup>(1,3,4)</sup><br>SDI1 <sup>(1,3,4)</sup> | _                                          | IOCC4 | _                  | _                 |

| RC5             | 24             | 39             | 43             | ANC5                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCC5 | _                  | _                 |

| RC6             | 25             | 40             | 44             | ANC6                         | _           | _                    | _                   | _             | _                                                  | CK1 <sup>(1,3)</sup>                       | IOCC6 | _                  | _                 |

| RC7             | 26             | 1              | 1              | ANC7                         | _           | _                    | _                   | _             | _                                                  | RX1 <sup>(1)</sup><br>DT1 <sup>(1,3)</sup> | IOCC7 | _                  | _                 |

| RD0             | 19             | 34             | 38             | AND0                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD0 | _                  | _                 |

| RD1             | 20             | 35             | 39             | AND1                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD1 | _                  | _                 |

| RD2             | 21             | 36             | 40             | AND2                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD2 | _                  | _                 |

| RD3             | 22             | 37             | 41             | AND3                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD3 | _                  | _                 |

| RD4             | 27             | 2              | 2              | AND4                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD4 | _                  | _                 |

| RD5             | 28             | 3              | 3              | AND5                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD5 | _                  | _                 |

| RD6             | 29             | 4              | 4              | AND6                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCD6 | _                  | _                 |

| RD7             | 30             | 5              | 5              | AND7                         | -           | _                    | _                   | _             | _                                                  | _                                          | IOCD7 | _                  | _                 |

| RE0             | 8              | 23             | 25             | ANE0                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCE0 | _                  | _                 |

| RE1             | 9              | 24             | 26             | ANE1                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCE1 | _                  | _                 |

| RE2             | 10             | 25             | 27             | ANE2                         | _           | _                    | _                   | _             | _                                                  | _                                          | IOCE2 | _                  | _                 |

| RE3             | 1              | 16             | 18             | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | IOCE3 | _                  | MCLR<br>VPP       |

| V <sub>DD</sub> | 11<br>32       | 7<br>26        | 7<br>28        | _                            | _           | _                    | _                   | _             | _                                                  | _                                          | _     | _                  | V <sub>DD</sub>   |

| cor                | ntinued        |                |                |     |           |        |              |               |                              |                   |     |           |       |

|--------------------|----------------|----------------|----------------|-----|-----------|--------|--------------|---------------|------------------------------|-------------------|-----|-----------|-------|

| I/O                | 40-Pin<br>PDIP | 40-Pin<br>VQFN | 44-Pin<br>TQFP | ADC | Reference | Timers | ССР          | 10-Bit<br>PWM | MSSP                         | EUSART            | IOC | Interrupt | Basic |

| VSS                | 12<br>31       | 6<br>27        | 6<br>29        | _   | _         | _      | _            | _             | _                            | _                 | _   | _         | VSS   |

| OUT <sup>(2)</sup> | _              |                | _              | _   | _         | TMR0   | CCP1<br>CCP2 | PWM3<br>PWM4  | SCL1<br>SCK1<br>SDA1<br>SDO1 | TX1<br>DT1<br>CK1 | _   | _         | _     |

- 1. This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to the PPS input table in the device data sheet for details on which PORT pins may be used for this signal.

- 2. All output signals shown in this row are PPS remappable.

- 3. This is a bidirectional signal. For normal operation, user software must map this signal to the same pin via the PPS input and PPS output registers.

- 4. These pins can be configured for I<sup>2</sup>C or SMBus logic levels via the Rxyl2C registers. The SCL1/SDA1 signals may be assigned to these pins for expected operation. PPS assignments of these signals to other pins will operate; however, the logic levels will be standard TTL/ST as selected by the INLVL register.

## The Microchip Website

Microchip provides online support via our website at <a href="http://www.microchip.com/">http://www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to http://www.microchip.com/pcn and follow the registration instructions.

### **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: http://www.microchip.com/support

# **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these

methods, to our knowledge, require using the Microchip products in a manner outside the operating

specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of

intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

# **Legal Notice**

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-5304-8

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit http://www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                         | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|----------------------------------|-----------------------|-------------------------|-----------------------|

| Corporate Office                 | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.         | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199          | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200                | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277                | China - Chengdu       | India - Pune            | Tel: 45-4450-2828     |

| Technical Support:               | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| http://www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| Web Address:                     | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| http://www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| Atlanta                          | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                       | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614                | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455                | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                       | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370                | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                           | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA                  | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087                | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088                | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                          | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                       | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071                | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075                | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| Dallas                           | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX                      | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423                | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924                | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| Detroit                          | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                         | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000                | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX                      | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983                | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis                     | China - Xiamen        |                         | Tel: 31-416-690399    |

| Noblesville, IN                  | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323                | China - Zhuhai        |                         | Norway - Trondheim    |

| Fax: 317-773-5453                | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| Tel: 317-536-2380                |                       |                         | Poland - Warsaw       |

| Los Angeles                      |                       |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA                |                       |                         | Romania - Bucharest   |

| Tel: 949-462-9523                |                       |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608                |                       |                         | Spain - Madrid        |

| Tel: 951-273-7800                |                       |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC                      |                       |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510                |                       |                         | Sweden - Gothenberg   |

| New York, NY                     |                       |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000                |                       |                         | Sweden - Stockholm    |

| San Jose, CA                     |                       |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110                |                       |                         | UK - Wokingham        |

| Tel: 408-436-4270                |                       |                         | Tel: 44-118-921-5800  |

| Canada - Toronto                 |                       |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980                |                       |                         |                       |

| Fax: 905-695-2078                |                       |                         |                       |