# ■ VERY LOW POWER 1.8V 16K/8K/4K x 16 DUAL-PORT STATIC RAM

### IDT70P264/254/244L DATASHEET

#### **Features**

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High-speed access

- Industrial: 40/55ns (max.)

- Low-power operation

IDT70P264/254/244L Active: 27mW (typ.)

Standby: 3.6µW (typ.)

- On-chip port interrupt logic which supports level shift output

- Fully asynchronous operation from either port

- Power supply isolation functionality to aid system power management

- Separate upper-byte and lower-byte control for multiplexed bus compatibility

- Left port is selectable 3.0V, 2.5V or 1.8V

- Right port is 1.8V I/O

- LVTTL-compatible, single 1.8V (±100mV) power supply

- Available in 81 Ball 0.5mm-pitch BGA

- Industrial temperature range (-40°C to +85°C)

- Green parts available, see ordering information

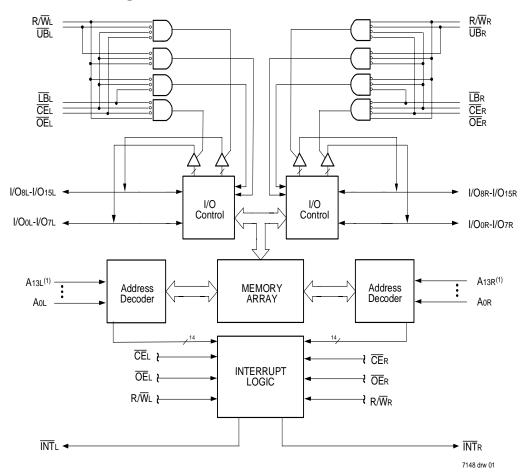

# Functional Block Diagram

#### NOTE:

1. A13x is a NC for IDT70P254. A13x and A12x are NC for IDT70P244.

FEBRUARY 2009

©2008 Integrated Device Technology, Inc.

DSC-7148/2

### Description

The IDT70P264/254/244 is a very low power 16K/8K/4K x 16 Dual-Port Static RAM. The IDT70P264/254/244 is designed to be used as a stand-alone 256/128/64K-bit Dual-Port SRAM.

This device provides two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power down

feature controlled by  $\overline{\text{CE}}$  permits the on-chip circuitry of each port to enter a very low standby power mode.

Fabricated using IDT's CMOS high-performance technology, these devices typically operate on only 27mW of power.

The IDT70P264/254/244 is packaged in a 81 ball 0.5mm-pitch Ball Grid Array. The package is a 1mm thick and designed to fit in wireless handset applications.

# **Pin Configurations**

## 70P264/254/244BY BY-81

# 81-Ball 0.5mm Pitch BGA Top View

|   | 1               | 2               | 3                | 4                               | 5                               | 6                  | 7                  | 8                  | 9                  |           |

|---|-----------------|-----------------|------------------|---------------------------------|---------------------------------|--------------------|--------------------|--------------------|--------------------|-----------|

| Α | A <sub>2R</sub> | A <sub>5R</sub> | A <sub>11R</sub> | CER                             | V <sub>SS</sub>                 | I/O <sub>14R</sub> | I/O <sub>12R</sub> | I/O <sub>10R</sub> | I/O <sub>8R</sub>  | Α         |

| В | A <sub>1R</sub> | A <sub>7R</sub> | A <sub>9R</sub>  | A <sub>12R</sub> <sup>(1)</sup> | A <sub>13R</sub> <sup>(1)</sup> | I/O <sub>13R</sub> | I/O <sub>11R</sub> | V <sub>SS</sub>    | I/O <sub>7R</sub>  | В         |

| С | A <sub>OR</sub> | A <sub>6R</sub> | A <sub>8R</sub>  | A <sub>10R</sub>                | R/W <sub>R</sub>                | I/O <sub>15R</sub> | V <sub>DD</sub>    | I/O <sub>9R</sub>  | I/O <sub>6R</sub>  | С         |

| D | ŪB <sub>R</sub> | A <sub>3R</sub> | A <sub>4R</sub>  | ĪNT <sub>R</sub>                | ŌĒ <sub>R</sub>                 | I/O <sub>5R</sub>  | I/O <sub>2R</sub>  | I/O <sub>4R</sub>  | I/O <sub>3R</sub>  | D         |

| Е | V <sub>SS</sub> | ŪB∟             | INTL             | LB <sub>R</sub>                 | $V_{DD}$                        | I/O <sub>13L</sub> | I/O <sub>15L</sub> | I/O <sub>0R</sub>  | I/O <sub>1R</sub>  | Е         |

| F | ŪB∟             | A <sub>4L</sub> | A <sub>2L</sub>  | A <sub>3L</sub>                 | I/O <sub>3L</sub>               | I/O <sub>5L</sub>  | I/O <sub>12L</sub> | V <sub>DDQL</sub>  | I/O <sub>14L</sub> | F         |

| G | A <sub>0L</sub> | A <sub>1L</sub> | A <sub>11L</sub> | A <sub>12</sub> L               | ŌĒL                             | I/O <sub>4L</sub>  | I/O <sub>9L</sub>  | I/O <sub>11L</sub> | I/O <sub>10L</sub> | G         |

| Н | A <sub>6L</sub> | A <sub>8L</sub> | A <sub>9L</sub>  | A <sub>13L</sub> <sup>(1)</sup> | CEL                             | I/O <sub>oL</sub>  | I/O <sub>2L</sub>  | V <sub>SS</sub>    | I/O <sub>8L</sub>  | Н         |

| J | A <sub>5L</sub> | A <sub>7L</sub> | A <sub>10L</sub> | R/W <sub>L</sub>                | V <sub>SS</sub>                 | I/O <sub>1L</sub>  | $V_{DDQL}$         | I/O <sub>6L</sub>  | I/O <sub>7L</sub>  | J         |

|   | 1               | 2               | 3                | 4                               | 5                               | 6                  | 7                  | 8                  | 9                  | 48 drw 02 |

<sup>1.</sup> A13x is a NC for IDT70P254. A13x and A12x are NC for IDT70P244.

### Pin Names

| Left Port                 | Right Port                | Names                                                     |

|---------------------------|---------------------------|-----------------------------------------------------------|

| CEL                       | CER                       | Chip Enable (Input)                                       |

| R/WL                      | R/W̄R                     | Read/Write Enable (Input)                                 |

| ŌĒL                       | ŌĒR                       | Output Enable (Input)                                     |

| Aol - A13L <sup>(1)</sup> | Aor - A13R <sup>(1)</sup> | Address (Input)                                           |

| I/O0L - I/O15L            | I/Oor - I/O15R            | Data Input/Output                                         |

| UBL                       | ŪBR                       | Upper Byte Select (Input)                                 |

| <u>∐B</u> L               | <u>∏</u> R                | Lower Byte Select (Input)                                 |

| ĪNTL                      | ĪNTR                      | Interrupt Flag (Output)                                   |

| V                         | DD                        | Power for Core + Right Port I/O (1.8V) (Input)            |

| VD                        | DQL                       | Left Port I/O Supply Voltage (1.8V, 2.5V or 3.0V) (Input) |

| V                         | SS                        | Ground (0V) (Input)                                       |

#### NOTE:

1. A13x is a NC for IDT70P254. A13x and A12x are NC for IDT70P244.

7148 tbl 01

Truth Table I: Non-Contention Read/Write Control

|    |     | Inputs |    |    | Outputs         |                    |                                         |

|----|-----|--------|----|----|-----------------|--------------------|-----------------------------------------|

| CE | R/W | ŌĒ     | ŪB | ĪВ | I/O8-15         | I/O <sub>0-7</sub> | Mode                                    |

| Н  | Х   | Х      | Х  | Х  | High-Z          | High-Z             | Deselected: Power Down                  |

| Х  | Х   | Х      | Н  | Н  | High-Z          | High-Z             | Both Bytes Deselected                   |

| L  | L   | Х      | L  | Н  | DATAIN          | High-Z             | Write to Upper Byte Only <sup>(1)</sup> |

| L  | L   | Х      | Н  | L  | High-Z          | DATAIN             | Write to Lower Byte Only <sup>(1)</sup> |

| L  | L   | Х      | L  | L  | DATAIN          | DATAIN             | Write to Both Bytes <sup>(1)</sup>      |

| L  | Н   | L      | L  | Н  | <b>DATA</b> out | High-Z             | Read Upper Byte Only                    |

| L  | Н   | L      | Н  | L  | High-Z          | <b>DATA</b> out    | Read Lower Byte Only                    |

| L  | Н   | L      | L  | L  | <b>DATA</b> out | <b>DATA</b> out    | Read Both Bytes                         |

| Х  | Х   | Н      | Х  | Х  | High-Z          | High-Z             | Outputs Disabled                        |

7148 tbl 02

NOTE:

1. AOL — A13L  $\neq$  AOR — A13R

## Absolute Maximum Ratings(1)

| Symbol                  | Rating                                      | Rating Industrial                           |    |  |

|-------------------------|---------------------------------------------|---------------------------------------------|----|--|

| VTERM                   | Supply Voltage on VDD with Respect to GND   | -0.5 to +2.9                                | V  |  |

| VTERM                   | Supply Voltage on VDDQL with Respect to GND | -0.5 to +3.6                                | V  |  |

| VTERM <sup>(2)</sup>    | Terminal Voltage with Respect to GND        | -0.5 to V <sub>DD</sub> +0.3 <sup>(4)</sup> | V  |  |

| TBIAS <sup>(3)</sup>    | Temperature Under Bias                      | -55 to +125                                 | °C |  |

| Tstg                    | Storage Temperature                         | -65 to +150                                 | °C |  |

| NLT                     | Junction Temperature                        | +150                                        | °C |  |

| IOUT (for VDDQL = 3.0V) | DC Output Current                           | 20                                          | mA |  |

| IOUT (for VDDQL = 2.5V) | DC Output Current                           | 20                                          | mA |  |

7148 tbl 03

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VTERM must not exceed VDD + 0.3V for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period over VTERM = VDD + 0.3V.

- 3. Ambient Temperature under DC Bias. No AC Conditions. Chip Deselected.

- 4. VDDQL + 0.3V for left port.

# Capacitance

$(TA = +25^{\circ}C, f = 1.0MHz)$

| Symbol | Parameter          | Conditions <sup>(2)</sup> | Max. | Unit |

|--------|--------------------|---------------------------|------|------|

| CIN    | Input Capacitance  | VIN = 3dV                 | 9    | pF   |

| Соит   | Output Capacitance | Vout = 3dV                | 10   | pF   |

7148 tbl 07

#### NOTES:

- This parameter is determined by device characterization but is not production tested.

- 3dV references the interpolated capacitance when the input and output signals switch from 0V to 3V or from 3V to 0V.

# $\label{eq:maximumOperatingTemperature} \mbox{ Maximum Operating Temperature and Supply Voltage}^{(1)}$

| Grade      | Ambient<br>Temperature | GND | <b>V</b> DD         |

|------------|------------------------|-----|---------------------|

| Industrial | -40°C to +85°C         | 0V  | 1.8V <u>+</u> 100mV |

#### NOTE:

7148 tbl 04

1. This is the parameter Ta. This is the "instant on" case temperature.

Recommended DC Operating Conditions (VDDQL = 3.0V±300mV)

| Symbol | Parameter                         | Min. | Тур. | Max.        | Unit |

|--------|-----------------------------------|------|------|-------------|------|

| Vdd    | Supply Voltage                    | 1.7  | 1.8  | 1.9         | V    |

| VDDQL  | Left Port Supply Voltage          | 2.7  | 3.0  | 3.3         | V    |

| Vss    | Ground                            | 0    | 0    | 0           | V    |

| VIHL   | Input High Voltage (VDDQL = 3.0V) | 2.0  |      | VDDQL + 0.2 | V    |

| VILL   | Input Low Voltage (VDDQL = 3.0V)  | -0.2 | _    | 0.7         | V    |

| VIHR   | Input High Voltage                | 1.2  |      | VDD + 0.2   | V    |

| VILR   | Input Low Voltage                 | -0.2 | _    | 0.4         | V    |

7148 tbl 05

Recommended DC Operating Conditions (VDDQL = 2.5V±100mV)

| Symbol | Parameter                         | Min. | Тур. | Max.        | Unit |

|--------|-----------------------------------|------|------|-------------|------|

| VDD    | Supply Voltage                    | 1.7  | 1.8  | 1.9         | V    |

| VDDQL  | Left Port Supply Voltage          | 2.4  | 2.5  | 2.6         | V    |

| Vss    | Ground                            | 0    | 0    | 0           | ٧    |

| VIHL   | Input High Voltage (VDDQL = 2.5V) | 1.7  | _    | VDDQL + 0.3 | ٧    |

| VILL   | Input Low Voltage (VDDQL = 2.5V)  | -0.3 |      | 0.6         | ٧    |

| VIHR   | Input High Voltage                | 1.2  |      | VDD + 0.2   | V    |

| VILR   | Input Low Voltage                 | -0.2 |      | 0.4         | V    |

7148 tbl 06

Recommended DC Operating Conditions (VDDQL = 1.8V±100mV)

| Symbol | Parameter                         | Min. | Тур. | Max.        | Unit |

|--------|-----------------------------------|------|------|-------------|------|

| VDD    | Supply Voltage                    | 1.7  | 1.8  | 1.9         | V    |

| VDDQL  | Left Port Supply Voltage          | 1.7  | 1.8  | 1.9         | ٧    |

| Vss    | Ground                            | 0    | 0    | 0           | ٧    |

| VIHL   | Input High Voltage (VDDQL = 1.8V) | 1.2  |      | VDDQL + 0.2 | ٧    |

| VILL   | Input Low Voltage (VDDQL = 1.8V)  | -0.2 |      | 0.4         | V    |

| VIHR   | Input High Voltage                | 1.2  |      | VDD + 0.2   | V    |

| VILR   | Input Low Voltage                 | -0.2 | _    | 0.4         | V    |

7148 tbl 06\_5

- 1.  $VIL \ge -1.5V$  for pulse width less than 10ns.

- 2. VTERM must not exceed VDD + 0.3V.

# DC Electrical Characteristics Over the Operating

Temperature and Supply Voltage Range (VDD = 1.8V ± 100mV)

| Symbol                  | Parameter                          | Test Conditions                             | Min.         | Max. | Unit |

|-------------------------|------------------------------------|---------------------------------------------|--------------|------|------|

| lu                      | Input Leakage Current              | $V_{DD} = 1.8V$ , $V_{IN} = 0V$ to $V_{DD}$ | -1           | 1    | μΑ   |

| ILO                     | Output Leakage Current             | $\overline{CE}$ = VIH, VOUT = 0V to VDD     | -1           | 1    | μΑ   |

| Voll                    | Output Low Voltage (VDDQL = 3.0V)  | IOLL = +2mA                                 | _            | 0.4  | V    |

| Vohl                    | Output High Voltage (VDDQL = 3.0V) | IOHL = -2mA                                 | 2.1          |      | V    |

| Voll                    | Output Low Voltage (VDDQL = 2.5V)  | IOLL = +2mA                                 | _            | 0.4  | V    |

| Vohl                    | Output High Voltage (VDDQL = 2.5V) | IOHL = -2mA                                 | 2.0          |      | V    |

| Voll                    | Output Low Voltage (VDDQL = 1.8V)  | IOLL = +0.1mA                               | _            | 0.2  | V    |

| Vohl                    | Output High Voltage (VDDQL = 1.8V) | IOHL = -0.1mA                               | VDDQL - 0.2V |      | V    |

| Volr                    | Output Low Voltage                 | lolr = +0.1mA                               | _            | 0.2  | V    |

| Vohr                    | Output High Voltage                | IOHR = -0.1mA                               | VDD - 0.2V   |      | V    |

| VOLINT <sup>(1,2)</sup> | Output Low Voltage Interrupt       | lol = +2mA                                  | _            | 0.4  | V    |

#### NOTES:

7148 tbl 08

2.  $VDDINTR \ge VDD$ ,  $VDDINTL \ge VDDQL$

# DC Electrical Characteristics Over the Operating

Temperature and Supply Voltage Range (VDD = 1.8V ±100mV)

|        |                                                                                |                                                                                                                                                                                          |        |    |                     | 70P264/<br>Ind'l |                     |      |      |

|--------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|---------------------|------------------|---------------------|------|------|

|        |                                                                                |                                                                                                                                                                                          |        |    | 40                  | ns               | 55                  | ns   |      |

| Symbol | Parameter                                                                      | Test Condition                                                                                                                                                                           | Versio | on | Typ. <sup>(1)</sup> | Max.             | Typ. <sup>(1)</sup> | Max. | Unit |

| loo    | Dynamic Operating Current (Both Ports Active)                                  | $\overline{CE}R$ and $\overline{CE}L = VIL$ , Outputs Open $f = f_{MAX}^{(2)}$                                                                                                           | IND'L  | L  | 25                  | 40               | 15                  | 25   | mA   |

| ISB1   | Standby Current (Both Ports Inactive)                                          | $\overline{\text{CE}}_{\text{R}} = \text{V}_{\text{DD}} - 0.2 \text{V} \text{ and } \overline{\text{CE}}_{\text{L}} = \text{V}_{\text{DDOL}} - 0.2 \text{V},$ $f = f_{\text{MAX}}^{(2)}$ | IND'L  | L  | 2                   | 6                | 2                   | 6    | μΑ   |

| ISB2   | Standby Current (One Port Inactive, One Port Active)                           | $\overline{CE}$ "A" = VL and $\overline{CE}$ "B" = VH $^{(3)}$ , Active Port Outputs Open f = fMAX $^{(2)}$                                                                              | IND'L  | L  | 8.5                 | 18               | 8.5                 | 14   | mA   |

| ISB3   | Full Standby Current (Both<br>Ports Inactive - CMOS Level<br>Inputs)           | $\overline{\text{CE}}_L \geq \text{VDDOL}$ - 0.2V and $\overline{\text{CE}}_R \geq \text{VDD}$ - 0.2V, $f = 0$                                                                           | IND'L  | L  | 2                   | 6                | 2                   | 6    | μΑ   |

| ISB4   | Standby Current (One Port<br>Inactive, One Port Active -<br>CMOS Level Inputs) | $\overline{\text{CE}}$ -A° $\leq$ 0.2V and $\overline{\text{CE}}$ -B° $\geq$ VDDQ - 0.2V <sup>(3)</sup> , Active Port Outputs Open f = fMaX <sup>(2)</sup>                               | IND'L  | L  | 8.5                 | 18               | 8.5                 | 14   | mA   |

#### NOTES:

7148 tbl 09

- 1. VDD = 1.8V, TA = +25°C, and are not production tested. IDD = 15mA (typ.)

- 2. At f = fmax, address and control lines are cycling at the maximum frequency read cycle of 1/trc, and using "AC Test Conditions".

- 3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

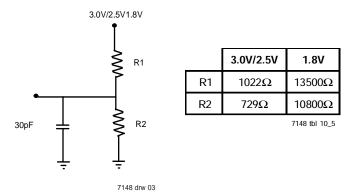

<sup>1.</sup> Interrupt can be level shifted to a higher voltage by tieing a resistor (R3) to an external power supply (VDDINTx). The value of R3 is a trade off between tinx and power.

### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V/GND to 2.5V/GND to 1.8V |  |  |  |  |

|-------------------------------|-------------------------------------|--|--|--|--|

| Input Rise/Fall Times         | 3ns Max.                            |  |  |  |  |

| Input Timing Reference Levels | 1.5V/1.25V/0.9V                     |  |  |  |  |

| Output Reference Levels       | 1.5V/1.25V/0.9V                     |  |  |  |  |

| Output Load                   | Figure 1A                           |  |  |  |  |

7148 tbl 10

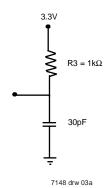

Figure 1A. AC Output Test Load (5pF for tLz, tHz, twz, tow)

Figure 1B. AC Output Test Load for Interrupt

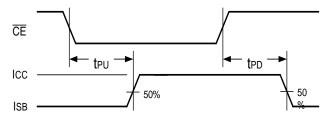

# Timing of Power-Up Power-Down

7148 drw 04

AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(2)</sup>

|            |                                                | 70P264/254/244<br>Ind'l Only |      |      |      |      |  |  |  |

|------------|------------------------------------------------|------------------------------|------|------|------|------|--|--|--|

|            |                                                | 40ns 55ns                    |      |      | ins  |      |  |  |  |

| Symbol     | Parameter                                      | Min.                         | Max. | Min. | Max. | Unit |  |  |  |

| READ CYCLE |                                                |                              |      |      |      |      |  |  |  |

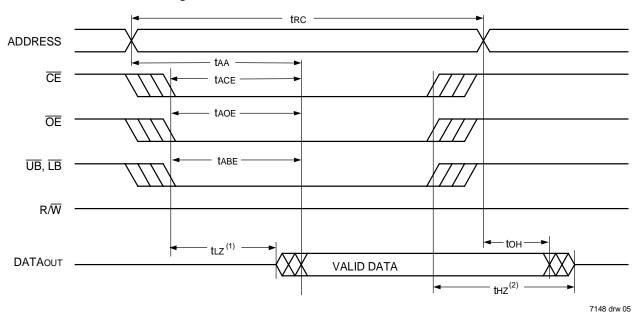

| trc        | Read Cycle Time                                | 40                           |      | 55   | _    | ns   |  |  |  |

| taa        | Address Access Time                            |                              | 40   | _    | 55   | ns   |  |  |  |

| tace       | Chip Enable Access Time                        |                              | 40   | _    | 55   | ns   |  |  |  |

| tabe       | Byte Enable Access Time                        | _                            | 40   | _    | 55   | ns   |  |  |  |

| taoe       | Output Enable Access Time                      | -                            | 25   | _    | 30   | ns   |  |  |  |

| tон        | Output Hold from Address Change                | 5                            | _    | 5    | _    | ns   |  |  |  |

| t.z        | Output Low-Z Time <sup>(1,3)</sup>             | 5                            | _    | 5    | _    | ns   |  |  |  |

| tHZ        | Output High-Z Time <sup>(1,3)</sup>            |                              | 10   | _    | 25   | ns   |  |  |  |

| tru        | Chip Enable to Power Up Time <sup>(1)</sup>    | 0                            | _    | 0    | _    | ns   |  |  |  |

| tPD        | Chip Disable to Power Down Time <sup>(1)</sup> |                              | 40   | _    | 55   | ns   |  |  |  |

#### NOTES:

7148 tbl 11

- 1. This parameter is guaranteed by device characterization, but is not production tested.

- 2. The specification for toH must be met by the device supplying write data to the SRAM under all operating conditions. Although toH and tow values will vary over voltage and temperature, the actual toH will always be smaller than the actual tow.

- 3. At any given temperature and voltage condition, thz is less than tLz for any given device.

# Waveform of Read Cycles

- Timing depends on which signal is asserted last, OE, CE, IB, or UB.

Timing depends on which signal is de-asserted first CE, OE, LB, or UB.

AC Electrical Characteristics Over the Operating Temperature and Supply Voltage<sup>(3)</sup>

|             |                                                  | 40ns |      | 55ns |      |      |

|-------------|--------------------------------------------------|------|------|------|------|------|

| Symbol      | Parameter                                        | Min. | Max. | Min. | Max. | Unit |

| WRITE CYCLE |                                                  |      |      |      |      |      |

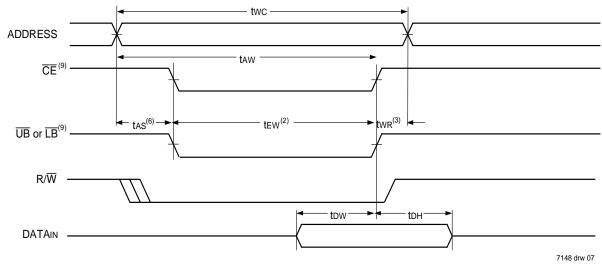

| twc         | Write Cycle Time                                 | 40   | _    | 55   | _    | ns   |

| tew         | Chip Enable to End-of-Write <sup>(2)</sup>       | 30   | _    | 45   | _    | ns   |

| taw         | Address Valid to End-of-Write                    | 30   | _    | 45   | _    | ns   |

| tas         | Address Set-up Time <sup>(2)</sup>               | 0    | _    | 0    | _    | ns   |

| twp         | Write Pulse Width                                | 25   | _    | 40   | _    | ns   |

| twr         | Write Recovery Time                              | 0    | _    | 0    | _    | ns   |

| tow         | Data Valid to End-of-Write                       | 20   |      | 30   |      | ns   |

| tон         | Data Hold Time <sup>(3)</sup>                    | 0    |      | 0    | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1)</sup>  | _    | 15   | _    | 25   | ns   |

| tow         | Output Active from End-of-Write <sup>(1,3)</sup> | 0    |      | 0    |      | ns   |

#### NOTES:

This parameter is guaranteed by device characterization, but is not production tested.

To access SRAM, CE = VIL, UB or LB = VIL.

<sup>3.</sup> The specification for ton must be met by the device supplying write data to the SRAM under all operating conditions. Although ton and tow values will vary over voltage and temperature, the actual toH will always be smaller than the actual tow.

# Timing Waveform of Write Cycle No. 1, R/W Controlled Timing (1,5,8)

# Timing Waveform of Write Cycle No. 2, **CE**, **UB**, **LB** Controlled Timing<sup>(1,5)</sup>

- 1. R/ $\overline{W}$  or  $\overline{CE}$  or  $\overline{UB}$  &  $\overline{LB}$  must be high during all address transitions.

- 2. A write occurs during the overlap ( $tew\underline{\ or\ twp}$ ) of a low  $\overline{\ UB}$  or  $\overline{\ LB}$  and a LOW  $\overline{\ CE}$  and a LOW  $R\overline{\ W}$  for memory array writing cycle.

- 3. two is measured from the earlier of  $\overline{CE}$  or  $R/\overline{W}$  going HIGH to the end of write cycle.

- 4. During this period, the I/O pins are in the output state and input signals must not be applied.

- 5. If the CE LOW transition occurs simultaneously with or after the RIW LOW transition, the outputs remain in the high-impedance state.

- 6. Timing depends on which enable signal is asserted last,  $\overline{CE}$ ,  $R/\overline{W}$  or byte control.

- 7. This parameter is guaranteed by device characterization, but is not production tested.

- 8. If  $\overline{OE}$  is LOW during  $R\overline{W}$  controlled write cycle, the write pulse width must be the larger of two or (twz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during an  $R\overline{W}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified two.

- 9. To access SRAM,  $\overline{CE} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ .

### AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range

|                  |                      | 70P264/254/244<br>Ind'l Only |      |      |      |      |  |  |  |

|------------------|----------------------|------------------------------|------|------|------|------|--|--|--|

|                  |                      | 40ns                         |      |      | ns   |      |  |  |  |

| Symbol           | Parameter            | Min.                         | Max. | Min. | Max. | Unit |  |  |  |

| INTERRUPT TIMING |                      |                              |      |      |      |      |  |  |  |

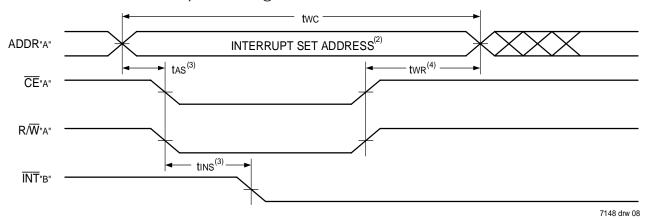

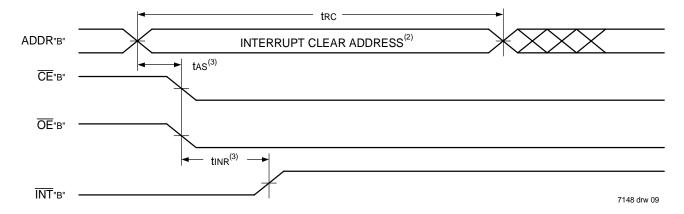

| tas              | Address Set-up Time  | 0                            | 1    | 0    | -    | ns   |  |  |  |

| twr              | Write Recovery Time  | 0                            | 1    | 0    | _    | ns   |  |  |  |

| tins             | Interrupt Set Time   | _                            | 35   |      | 45   | ns   |  |  |  |

| tinr             | Interrupt Reset Time | _                            | 45   | _    | 45   | ns   |  |  |  |

7148 tbl 13

# Waveform of Interrupt Timing<sup>(1)</sup>

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from "A".

- 2. See Interrupt Truth Table II.

- Timing depends on which enable signal (CE or RW) is asserted last.

Timing depends on which enable signal (CE or RW) is de-asserted first.

Truth Table II — Interrupt Flag<sup>(1)</sup>

| TIGUI |     |                 | 1110110                 | .   0 |            |     |                 |                         |               |                       |

|-------|-----|-----------------|-------------------------|-------|------------|-----|-----------------|-------------------------|---------------|-----------------------|

|       |     | Left Port       |                         |       | Right Port |     |                 |                         |               |                       |

| R/₩L  | CEL | <del>OE</del> L | A13L-A0L <sup>(1)</sup> | ΪΝΤι  | R/W̄R      | CER | <del>OE</del> R | A13R-A0R <sup>(1)</sup> | Ī <b>NT</b> R | Function              |

| L     | L   | Х               | 3FFF                    | Х     | Х          | Х   | Х               | Х                       | L             | Set Right INTR Flag   |

| Х     | Х   | Х               | Х                       | Х     | Х          | L   | L               | 3FFF                    | Н             | Reset Right INTR Flag |

| Х     | Х   | Х               | Х                       | L     | L          | L   | Х               | 3FFE                    | Х             | Set Left INTL Flag    |

| Х     | L   | L               | 3FFE                    | Н     | Х          | Х   | Х               | Х                       | Х             | Reset Left INTL Flag  |

#### NOTES:

7148 tbl 14

1. A13x is a NC for IDT70P254. A13x and A12x are NC for IDT70P244. Interrupt Addresses are 1FFF and 1FFE for IDT70P254 and FFF and FFE for IDT70P254.

### **Functional Description**

The IDT70P264/254/244 provides two ports with separate control, address and I/O pins that permit independent access to any location in memory. The IDT70P264/254/244 has an automatic power down feature controlled by  $\overline{\text{CE}}$ . The  $\overline{\text{CE}}$  controls on-chip power down circuitry that permits the respective port to go into a standby mode when not selected ( $\overline{\text{CE}}$  HIGH). When a port is enabled, access to the entire memory array is permitted.

### Power Supply

Each port can operate on independent I/O voltages. This is determined by what is connected to the VDDIOL and VDD pins. The supported I/O standards are 1.8V/2.5V LVCMOS and 3.0V LVTTL.

The IDT70P264/254/244 includes power supply isolation functionality which aids system power management. VDD and VDDIOL can be independently powered up/down which allows the left port or the right port and core to be powered down when not in use. If VDDIOL is powered down, but VDD remains powered up all inputs to the core from the left port will be forced to deasserted states at full swing DC values to minimize leakage current and active power consumption. If VDD is powered down but VDDIOL remain powered up, all outputs for the left port will remain in the state they were in prior to power down.

### Interrupts

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag ( $\overline{\text{INTL}}$ ) is asserted when the right port writes to memory location 3FFE (HEX) (1FFE for IDT70P254, FFE for IDT70P244), where a write is defined as the  $\overline{\text{CE}}=R/\overline{\text{W}}=\text{VIL}$  per Truth Table II. The left port clears the interrupt by accessing address location 3FFE (1FFE for IDT70P254, FFE for IDT70P244) when  $\overline{\text{CE}}_R=\overline{\text{OE}}_R=\text{VIL}$ ,  $R/\overline{\text{W}}$  is a "don't care". Likewise, the right port interrupt flag ( $\overline{\text{INTR}}$ ) is asserted when the left port writes to memory location 3FFF (HEX) (1FFF for IDT70P254, FFF for IDT70P244) and to clear the interrupt flag ( $\overline{\text{INTR}}$ ), the right port must read the memory location 3FFF. The message (16 bits) at 3FFE or 3FFF is user-defined, since it is an addressable SRAMlocation. If the interrupt function is not used, address locations 3FFE and 3FFF are not used as mail boxes, but as part of the random access memory. Refer to Truth Table II for the interrupt operation.

The interrupt outputs of the IDT70P264/254/244 should be connected to an interrupt power supply (VDDINTx) through an external pull-up resistor. As long as VDDINTR  $\geq$  VDD and VDDINTL  $\geq$  VDDQL, there will be no current flowing between VDDINTx and VDD/VDDQL.

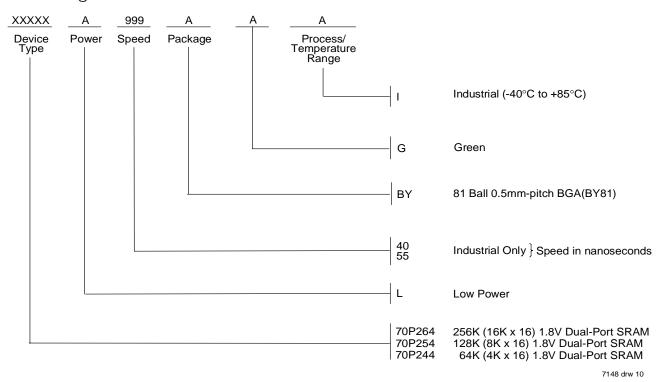

### Ordering Information

# Datasheet Document History

09/26/08: Initial Datasheet

02/20/09: Removed Preliminary status from entire datasheet

Page 14 Removed "IDT" from orderable part number

CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road

6024 Silver Creek Valley Road San Jose, CA 95138 for SALES:

800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com

for Tech Support: 408-284-2794 DualPortHelp@idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.