# TT Type < for Stratum 3 >

# 7.0 x 5.0 mm SMD Voltage Controlled Temperature Compensated Crystal Oscillator

#### **FEATURE**

- Typical  $7.0 \times 5.0 \times 1.9$  mm ceramic SMD package.

- Stratum 3 (Overall ±4.6ppm including 20 years aging.)

- CMOS and Clipped Sine wave (without DC-cut capacitor) output optional.

## **TYPICAL APPLICATION**

- Stratum 3

- Femtocell, Base Stations

**RoHS Compliant**

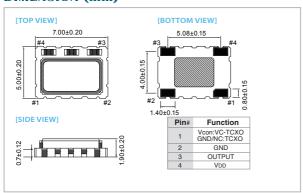

### **DIMENSION (mm)**

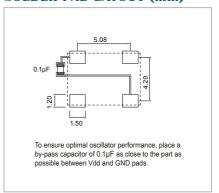

### **SOLDER PAD LAYOUT (mm)**

#### **ELECTRICAL SPECIFICATION**

| Parameter                                                  | 2.5V                               |                                        | 3.3V               |                                        | Unit    |

|------------------------------------------------------------|------------------------------------|----------------------------------------|--------------------|----------------------------------------|---------|

|                                                            | Min.                               | Max.                                   | Min.               | Max.                                   | Offic   |

| Supply Voltage Variation (VDD)                             | VDD-5%                             | VDD+5%                                 | VDD-5%             | VDD+5%                                 | V       |

| Frequency Range                                            | 5                                  | 52                                     | 5                  | 52                                     | MHz     |

| Standard Frequency                                         | 10, 12.8, 16.384, 19.2, 20, 25, 26 |                                        |                    |                                        | IVII IZ |

| Operating Temp. Range                                      | -20 ~ 70<br>-40 ~ 85               |                                        |                    | °C                                     |         |

| Frequency Stability (Overall, 20 Years)*                   | -                                  | ±4.6                                   | -                  | ±4.6                                   | ppm     |

| Frequency Stability Vs Temp. Range (Ref. to (FMAX+Fmin)/2) | -                                  | ±0.14 (-20~+70°C)<br>±0.28 (-40~+85°C) | -                  | ±0.14 (-20~+70°C)<br>±0.28 (-40~+85°C) | ppm     |

| Holdover Stability +                                       | -                                  | ±0.32                                  | _                  | ±0.32                                  | ppm     |

| Supply Current (CMOS output)                               | _                                  | 8                                      | -                  | 8                                      | mA      |

| Supply Current (Clipped Sine Wave)                         | _                                  | 5                                      | -                  | 5                                      |         |

| Output Level (CMOS) Output High (Logic "1")                | 90%VDD                             | _                                      | 90%V <sub>DD</sub> | -                                      | V       |

| Output Low (Logic "0")                                     | _                                  | 10%VDD                                 | _                  | 10%VDD                                 | •       |

| Duty                                                       | 45                                 | 55                                     | 45                 | 55                                     | %       |

| Output Level (Clipped Sine Wave)                           | 0.8                                | -                                      | 0.8                | _                                      | Vp-p    |

| Load (CMOS)                                                | 15pF 15pF                          |                                        |                    |                                        |         |

| Load (Clipped Sine Wave)                                   | 10 KΩ // 10pF                      |                                        | 10 KΩ // 10pF      |                                        |         |

| Control Voltage Range (VCTCXO)                             | 0.5                                | 2.5                                    | 0.5                | 2.5                                    | V       |

| Pulling Range (VCTCXO)                                     | ±5.0                               | -                                      | ±5.0               | _                                      | ppm     |

| Vc Input Impedance (VCTCXO)                                | 100                                | -                                      | 100                | _                                      | kΩ      |

| Phase Noise @ 10 MHz 100 Hz                                | -130                               |                                        |                    |                                        | dBc/Hz  |

| 1 kHz                                                      | -145                               |                                        |                    |                                        |         |

| 10 kHz                                                     | -154                               |                                        |                    |                                        |         |

| Start time                                                 | _                                  | 5                                      | _                  | 5                                      | mSec    |

| Storage Temp. Range                                        | -55                                | 125                                    | -55                | 125                                    | °C      |

Standard frequencies are frequencies which the crystal has been designed and does not imply a stock position.

Note: not all combination of options are available. Other specifications may be available upon request.

<sup>\*</sup> Including calibration @ 25°C, supply voltage VDD±5%, load ±10%, reflow soldering, 20 years aging and frequency stability over temperature.

<sup>+</sup> Including 24hours aging , supply voltage VDD±5% and frequency stability over temperature.