## **IF Digitizing Subsystem**

AD9874\*

**FEATURES**

10 MHz to 300 MHz Input Frequency

7.2 kHz to 270 kHz Output Signal Bandwidth

8.1 dB SSB NF

0 dBm IIP3

AGC Free Range up to -34 dBm

12 dB Continuous AGC Range

16 dB Front End Attenuator

Baseband I/Q 16-Bit (or 24-Bit) Serial Digital Output

LO and Sampling Clock Synthesizers

Programmable Decimation Factor, Output Format,

AGC, and Synthesizer Settings

370 Ω Input Impedance

2.7 V to 3.6 V Supply Voltage

Low Current Consumption: 20 mA

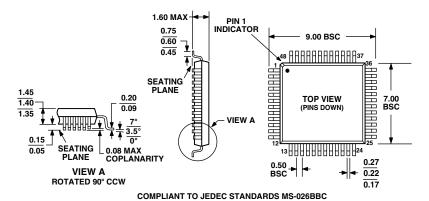

48-Lead LQFP Package (1.4 mm Thick)

### **APPLICATIONS**

Multimode Narrow-Band Radio Products

Analog/Digital UHF/VHF FDMA Receivers

TETRA, APCO25, GSM/EDGE

Portable and Mobile Radio Products

Base Station Applications

SATCOM Terminals

#### **GENERAL DESCRIPTION**

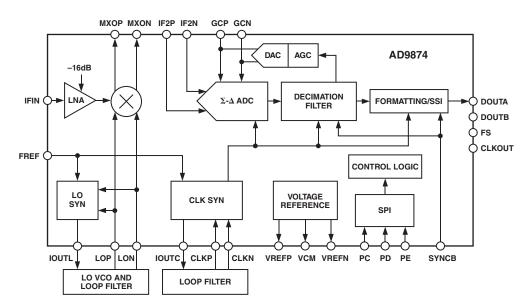

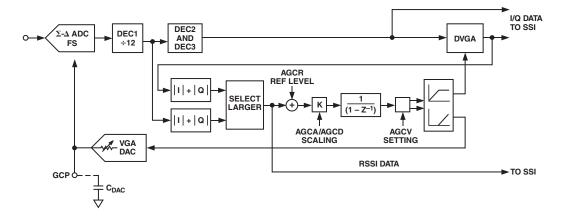

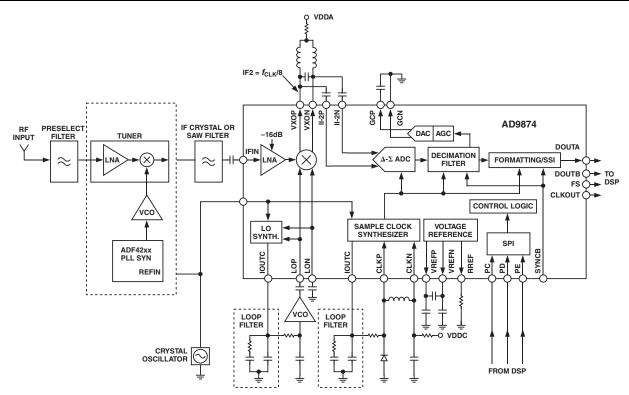

The AD9874 is a general-purpose IF subsystem that digitizes a low level 10 MHz to 300 MHz IF input with a signal bandwidth ranging from 6.8 kHz to 270 kHz. The signal chain of the AD9874 consists of a low noise amplifier, a mixer, a band-pass sigma-delta analog-to-digital converter, and a decimation filter with programmable decimation factor. An automatic gain control (AGC) circuit gives the AD9874 12 dB of continuous gain adjustment. Auxiliary blocks include both clock and LO synthesizers.

The AD9874's high dynamic range and inherent antialiasing provided by the band-pass sigma-delta converter allow the AD9874 to cope with blocking signals up to 95 dB stronger than the desired signal. This attribute can often reduce the cost of a radio by reducing its IF filtering requirements. Also, it enables multimode radios of varying channel bandwidths, allowing the IF filter to be specified for the largest channel bandwidth.

The SPI port programs numerous parameters of the AD9874, thus allowing the device to be optimized for any given application. Programmable parameters include synthesizer divide ratios, AGC attenuation and attack/decay time, received signal strength level, decimation factor, output data format, 16 dB attenuator, and the selected bias currents. The bias currents of the LNA and mixer can be further reduced at the expense of degraded performance for battery-powered applications.

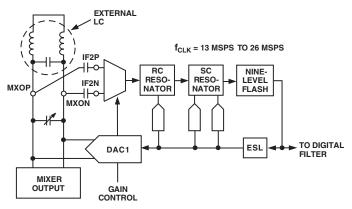

### **FUNCTIONAL BLOCK DIAGRAM**

\*Protected by U.S. Patent No. 5,969,657;

## REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

## TABLE OF CONTENTS

| AD9874—SPECIFICATIONS 3                          |

|--------------------------------------------------|

| ABSOLUTE MAXIMUM RATINGS 5                       |

| PIN CONFIGURATION/DESCRIPTION 6                  |

| DEFINITION OF SPECIFICATIONS/                    |

| TEST METHODS 7                                   |

| TYPICAL PERFORMANCE CHARACTERISTICS 8            |

| SERIAL PERIPHERAL INTERFACE (SPI)                |

| SYNCHRONOUS SERIAL INTERFACE (SSI) 16            |

| Synchronization Using SYNCB                      |

| Interfacing to DSPs                              |

| POWER CONTROL 19                                 |

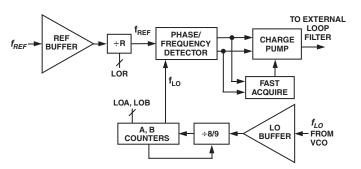

| LO SYNTHESIZER 19                                |

| Fast Acquire Mode                                |

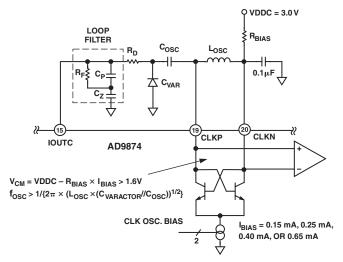

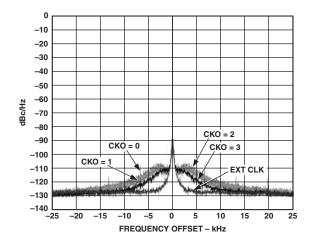

| CLOCK SYNTHESIZER 21                             |

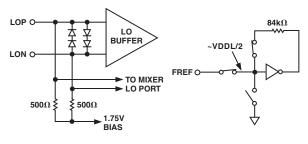

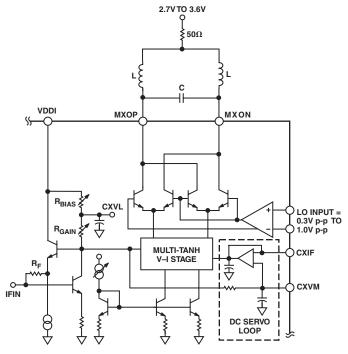

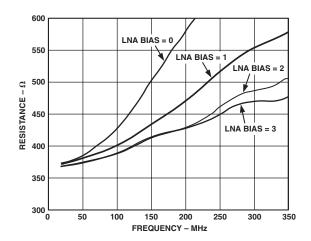

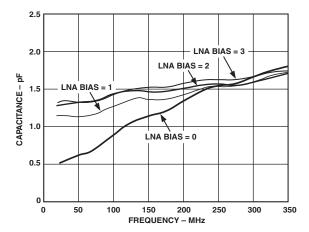

| IF LNA/MIXER 22                                  |

| BAND-PASS SIGMA DELTA $(\Sigma - \Delta)$ ADC 24 |

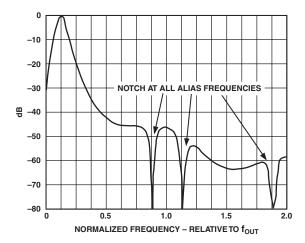

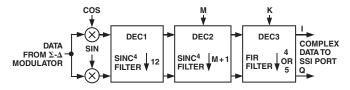

| DECIMATION FILTER 26                             |

| VARIABLE GAIN AMPLIFIER WITH AGC 28              |

| Variable Gain Control                            |

| Automatic Gain Control                           |

| System NF vs. VGA Control                        |

| APPLICATION CONSIDERATIONS 32                    |

| Frequency Planning 32                            |

| Spurious Responses                               |

| EXTERNAL PASSIVE COMPONENT                       |

| REQUIREMENTS 34                                  |

| APPLICATIONS 34                                  |

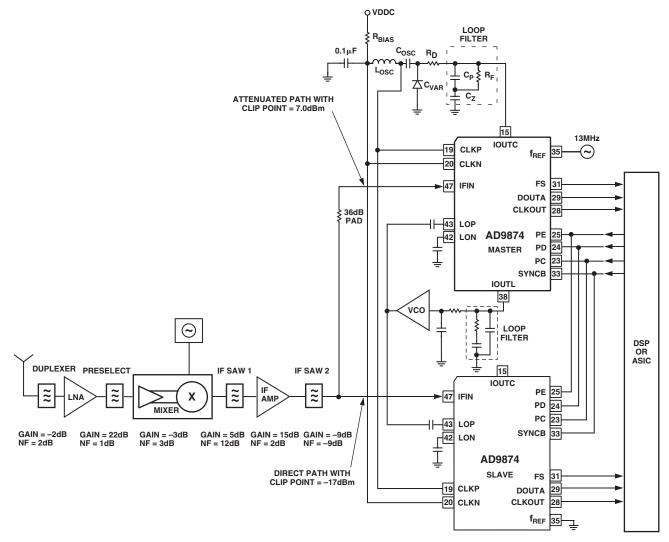

| Superheterodyne Receiver 34                      |

| Synchronization of Multiple AD9874s              |

| Split Path Rx Architecture                       |

| Hung Mixer Mode                                  |

| LAYOUT EXAMPLE                                   |

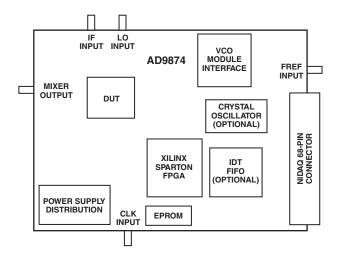

| EVALUATION BOARD AND SOFTWARE 38                 |

| OUTLINE DIMENSIONS                               |

| REVISION HISTORY 40                              |

|                                                  |

-2- REV. A

# $\begin{array}{l} \textbf{AD9874-SPECIFICATIONS} \text{ (VDDI = VDDF = VDDA = VDDC = VDDL = VDDD = VDDH = 2.7 V to 3.6 V,} \\ \textbf{VDDQ = VDDP = 2.7 V to 5.5 V, } \textbf{f}_{\text{CLK}} = 18 \text{ MSPS, } \textbf{f}_{\text{IF}} = 109.65 \text{ MHz, } \textbf{f}_{\text{LD}} = 107.4 \text{ MHz, } \textbf{f}_{\text{REF}} = 16.8 \text{ MHz, unless otherwise noted.})^1 \\ \end{array}$

| Parameter                                                                                                                                                                                                                                                                                                                                        | Temp                                    | Test Level                       | Min                                                           | Тур                                       | Max                                                | Unit                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| SYSTEM DYNAMIC PERFORMANCE <sup>2</sup> SSB Noise Figure @ Min VGA Attenuation <sup>3, 4</sup> @ Max VGA Attenuation <sup>3, 4</sup> Dynamic Range with AGC Enabled <sup>3, 4</sup> IF Input Clip Point @ Max VGA Attenuation <sup>3</sup> @ Min VGA Attenuation <sup>3</sup> Input Third Order Intercept (IIP3) Gain Variation over Temperature | Full Full Full Full Full Full Full Full | IV<br>IV<br>IV<br>IV<br>IV<br>IV | 91<br>-20<br>-32<br>-5                                        | 8.1<br>13<br>95<br>-19<br>-31<br>0<br>0.7 | 9.5                                                | dB<br>dB<br>dBm<br>dBm<br>dBm<br>dBm<br>dB            |

| LNA + MIXER  Maximum RF and LO Frequency Range  LNA Input Impedance  Mixer LO Input Resistance                                                                                                                                                                                                                                                   | Full<br>25°C<br>25°C                    | IV<br>V<br>V                     | 300                                                           | 500<br>370//1.4<br>1                      |                                                    | MHz<br>Ω//pF<br>kΩ                                    |

| LO SYNTHESIZER  LO Input Frequency LO Input Amplitude FREF Frequency (for Sinusoidal Input ONLY) FREF Input Amplitude FREF Slew Rate Minimum Charge Pump Current @ 5 V <sup>5</sup> Maximum Charge Pump Current @ 5 V <sup>5</sup> Charge Pump Output Compliance <sup>6</sup> Synthesizer Resolution                                             | Full Full Full Full Full Full Full Full | IV IV IV IV IV VI VI VI VI VI    | 7.75<br>0.3<br>8<br>0.3<br>7.5<br>0.48<br>3.87<br>0.4<br>6.25 | 0.67<br>5.3                               | 300<br>2.0<br>25<br>3<br>0.78<br>6.2<br>VDDP - 0.4 | MHz<br>V p-p<br>MHz<br>V p-p<br>V/µs<br>mA<br>MA<br>V |

| CLOCK SYNTHESIZER CLK Input Frequency CLK Input Amplitude Minimum Charge Pump Output Current <sup>5</sup> Maximum Charge Pump Output Current <sup>5</sup> Charge Pump Output Compliance <sup>6</sup> Synthesizer Resolution                                                                                                                      | Full Full Full Full Full Full Full      | IV<br>IV<br>VI<br>VI<br>VI<br>IV | 13<br>0.3<br>0.48<br>3.87<br>0.4<br>2.2                       | 0.67<br>5.3                               | 26<br>VDDC<br>0.78<br>6.2<br>VDDQ – 0.4            | MHz<br>V p-p<br>mA<br>mA<br>V<br>kHz                  |

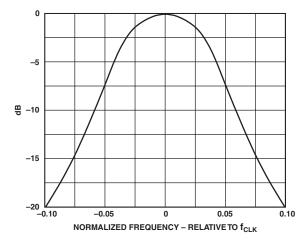

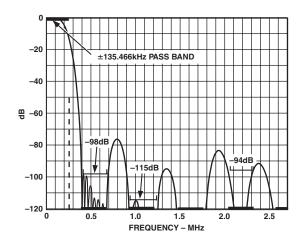

| SIGMA-DELTA ADC Resolution Clock Frequency (f <sub>CLK</sub> ) Center Frequency Pass-Band Gain Variation Alias Attenuation                                                                                                                                                                                                                       | Full<br>Full<br>Full<br>Full<br>Full    | IV<br>IV<br>V<br>IV<br>IV        | 16<br>13                                                      | f <sub>CLK</sub> /8                       | 24<br>26<br>1.0                                    | Bits<br>MHz<br>MHz<br>dB<br>dB                        |

| GAIN CONTROL Programmable Gain Step AGC Gain Range (Continuous) GCP Output Resistance                                                                                                                                                                                                                                                            | Full<br>Full<br>Full                    | V<br>V<br>IV                     | 50                                                            | 16<br>12<br>72.5                          | 95                                                 | dB<br>dB<br>kΩ                                        |

| OVERALL Analog Supply Voltage (VDDA, VDDF, VDDI) Digital Supply Voltage                                                                                                                                                                                                                                                                          | Full                                    | VI                               | 2.7                                                           | 3.0                                       | 3.6                                                | V                                                     |

| (VDDD, VDDC, VDDL) Interface Supply Voltage <sup>7</sup> (VDDH) Charge Pump Supply Voltage                                                                                                                                                                                                                                                       | Full<br>Full                            | VI<br>VI                         | 1.8                                                           | 3.0                                       | 3.6                                                | V<br>V                                                |

| (VDDP, VDDQ) Total Current High Performance Setting <sup>8</sup> Low Power Mode <sup>8</sup>                                                                                                                                                                                                                                                     | Full<br>Full<br>Full                    | VI<br>VI<br>VI                   | 2.7                                                           | 5.0<br>20<br>17                           | 5.5<br>26.5<br>22                                  | V<br>mA<br>mA                                         |

| Standby  OPERATING TEMPERATURE RANGE                                                                                                                                                                                                                                                                                                             | Full                                    | VI                               | -40                                                           | 0.01                                      | 0.1<br>+85                                         | mA<br>°C                                              |

## NOTES

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Standard operating mode: LNA/Mixer @ high bias setting, VGA @ Min ATTEN setting, synthesizers in normal (not fast acquire) mode, f<sub>CLK</sub> = 18 MHz, decimation factor = 900, 16-bit digital output, and 10 pF load on SSI output pins.

<sup>&</sup>lt;sup>2</sup>This includes 0.9 dB loss of matching network.

<sup>&</sup>lt;sup>3</sup>AGC with DVGA enabled.

<sup>&</sup>lt;sup>4</sup>Measured in 10 kHz bandwidth.

<sup>&</sup>lt;sup>5</sup>Programmable in 0.67 mA steps.

<sup>&</sup>lt;sup>6</sup>Voltage span in which LO (or CLK) charge pump output current is maintained within 5% of nominal value of VDDP/2 (or VDDQ/2).

<sup>&</sup>lt;sup>7</sup>VDDH must be less than VDDD + 0.5 V.

$<sup>^{8}</sup>$  Clock VCO off, add additional 0.7 mA with VGA @ Max ATTEN setting.

| Parameter                                               | Temp  | Test Level | Min       | Typ        | Max  | Unit     |

|---------------------------------------------------------|-------|------------|-----------|------------|------|----------|

| DECIMATOR                                               |       |            |           |            |      |          |

| Decimation Factor <sup>2</sup>                          | Full  | IV         | 48        |            | 960  |          |

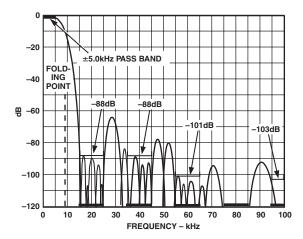

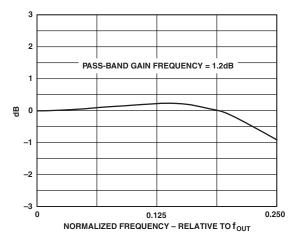

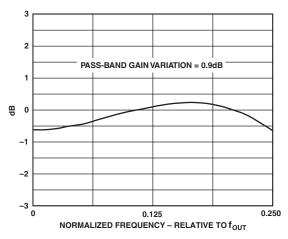

| Pass-Band Width                                         | Full  | V          |           | 50%        |      | fclkout  |

| Pass-Band Gain Variation                                | Full  | IV         |           |            | 1.2  | dB       |

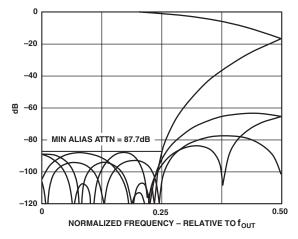

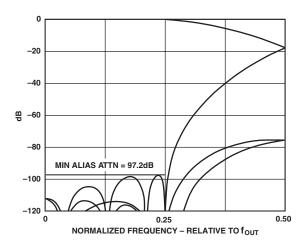

| Alias Attenuation                                       | Full  | IV         | 88        |            |      | dB       |

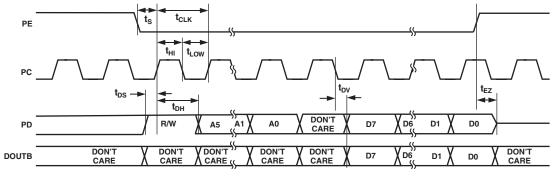

| SPI-READ OPERATION (See Figure 1a)                      |       |            |           |            |      |          |

| PC Clock Frequency                                      | Full  | IV         |           |            | 10   | MHz      |

| PC Clock Period (t <sub>CLK</sub> )                     | Full  | IV         | 100       |            |      | ns       |

| PC Clock HI (t <sub>HI</sub> )                          | Full  | IV         | 45        |            |      | ns       |

| PC Clock LOW (t <sub>LOW</sub> )                        | Full  | IV         | 45        |            |      | ns       |

| PC to PD Setup Time (t <sub>DS</sub> )                  | Full  | IV         | 2         |            |      | ns       |

| PC to PD Hold Time (t <sub>DH</sub> )                   | Full  | IV         | 2         |            |      | ns       |

| $\overline{PE}$ to PC Setup Time ( $t_S$ )              | Full  | IV         | 5         |            |      | ns       |

| PC to $\overline{PE}$ Hold Time (t <sub>H</sub> )       | Full  | IV         | 5         |            |      | ns       |

| SPI-WRITE OPERATION <sup>3</sup> (See Figure 1b)        |       |            |           |            |      |          |

| PC Clock Frequency                                      | Full  | IV         |           |            | 10   | MHz      |

| PC Clock Period (t <sub>CLK</sub> )                     | Full  | IV         | 100       |            |      | ns       |

| PC Clock HI (t <sub>HI</sub> )                          | Full  | IV         | 45        |            |      | ns       |

| PC Clock LOW (t <sub>LOW</sub> )                        | Full  | IV         | 45        |            |      | ns       |

| PC to PD Setup Time (t <sub>DS</sub> )                  | Full  | IV         | 2         |            |      | ns       |

| PC to PD Hold Time (t <sub>DH</sub> )                   | Full  | IV         | 2         |            |      | ns       |

| PC to PD (or DOUBT) Data Valid Time (t <sub>DV</sub> )  | Full  | IV         | 3         |            |      | ns       |

| PE to PD Output Valid to Hi-Z (t <sub>EZ</sub> )        | Full  | IV         |           | 8          |      | ns       |

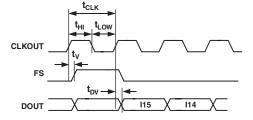

| SSI <sup>3</sup> (see Figure 2b)                        |       |            |           |            |      |          |

| CLKOUT Frequency                                        | Full  | IV         | 0.867     |            | 26   | MHz      |

| CLKOUT Period (t <sub>CLK</sub> )                       | Full  | IV         | 38.4      |            | 1153 | ns       |

| CLKOUT Duty Cycle (t <sub>HI</sub> , t <sub>LOW</sub> ) | Full  | IV         | 33        | 50         | 67   | ns       |

| CLKOUT to FS Valid Time (t <sub>V</sub> )               | Full  | IV         | -1        |            | +1   | ns       |

| CLKOUT to DOUT Data Valid Time (t <sub>DV</sub> )       | Full  | IV         | -1        |            | +1   | ns       |

| CMOS LOGIC INPUTS <sup>4</sup>                          |       |            |           |            |      |          |

| Logic "1" Voltage (V <sub>IH</sub> )                    | Full  | IV         | VDDH – 0. | 2          |      | V        |

| Logic "0" Voltage (V <sub>IL</sub> )                    | Full  | IV         | -==== 0.  |            | 0.5  | v        |

| Logic "1" Current (V <sub>IH</sub> )                    | Full  | IV         |           | 10         | 0.3  | μA       |

| Logic "0" Current $(V_{II})$                            | Full  | IV         |           | 10         |      | μΑ       |

| Input Capacitance                                       | Full  | IV         |           | 3          |      | pF       |

| CMOS LOGIC OUTPUTS <sup>3, 4, 5</sup>                   |       |            |           |            |      |          |

| Logic "1" Voltage (V <sub>IH</sub> )                    | Full  | IV         |           | VDDH - 0.2 |      | V        |

| Logic "0" Voltage (V <sub>IL</sub> )                    | Full  | IV         |           | . 2211 0.2 | 0.2  | v        |

| Logic o voitage (vil.)                                  | 1 uii | " "        | l         |            | 0.2  | <u> </u> |

#### NOTES

Specifications subject to change without notice.

-4- REV. A

$<sup>^{1}</sup>$ Standard operating mode: high IIP3 setting, synthesizers in normal (not fast acquire) mode,  $f_{CLK}$  = 18 MHz, decimation factor = 300, 10 pF load on SSI output pins: VDDx = 3.0 V.

<sup>&</sup>lt;sup>2</sup>Programmable in steps of 48 or 60.

$<sup>^{3}</sup>$ CMOS output mode with  $C_{LOAD} = 10$  pF and Drive Strength = 7.

$<sup>^4</sup>$ Absolute Max and Min input/output levels are VDDH +0.3 V and -0.3 V.

<sup>&</sup>lt;sup>5</sup>I<sub>OL</sub> = 1 mA; specification is also dependent on Drive Strength setting.

### **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                                                  | With Respect to                                            | Min  | Max        | Unit |

|------------------------------------------------------------|------------------------------------------------------------|------|------------|------|

| VDDF, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                   | GNDF, GNDA, GNDC, GNDD, GNDH, GNDL, GNDI, GNDS             | -0.3 | +4.0       | V    |

| VDDF, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                   | VDDR, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                   | -4.0 | +4.0       | V    |

| VDDP, VDDQ                                                 | GNDP, GNDQ                                                 | -0.3 | +6.0       | V    |

| GNDF, GNDA, GNDC, GNDD, GNDH, GNDL, GNDI, GNDQ, GNDP, GNDS | GNDF, GNDA, GNDC, GNDD, GNDH, GNDL, GNDI, GNDQ, GNDP, GNDS | -0.3 | +0.3       | V    |

| MXOP, MXON, LOP, LON, IFIN, CXIF, CXVL, CXVM               | GNDI                                                       | -0.3 | VDDI + 0.3 | V    |

| PC, PD, PE, CLKOUT, DOUTA, DOUTB, FS, SYNCB                | GNDH                                                       | -0.3 | VDDH + 0.3 | V    |

| IF2N, IF2P, GCP, GCN                                       | GNDF                                                       | -0.3 | VDDF + 0.3 | V    |

| VREFP, VREFN, RREF                                         | GNDA                                                       | -0.3 | VDDA + 0.3 | V    |

| IOUTC                                                      | GNDQ                                                       | -0.3 | VDDQ + 0.3 | V    |

| IOUTL                                                      | GNDP                                                       | -0.3 | VDDP + 0.3 | V    |

| CLKP, CLKN                                                 | GNDC                                                       | -0.3 | VDDC + 0.3 | V    |

| FREF                                                       | GNDL                                                       | -0.3 | VDDL + 0.3 | V    |

| Junction Temperature                                       |                                                            |      | 150        | °C   |

| Storage Temperature                                        |                                                            | -65  | +150       | °C   |

| Lead Temperature (10 sec)                                  |                                                            |      | 300        | °C   |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## THERMAL CHARACTERISTICS

### Thermal Resistance

48-Lead LQFP  $\theta_{JA} = 76.2$ °C/W  $\theta_{IC} = 17$ °C/W

## EXPLANATION OF TEST LEVELS TEST LEVEL

- I. 100% production tested.

- II. 100% production tested at 25°C and sample tested at specified temperatures. AC testing done on sample basis.

- III. Sample tested only.

- IV. Parameter is guaranteed by design and/or characterization testing.

- V. Parameter is a typical value only.

- VI. All devices are 100% production tested at 25°C; min and max guaranteed by design and characterization for industrial temperature range.

### **ORDERING GUIDE**

| Model                  | Temperature Range | Package Description                                           | Package Option |

|------------------------|-------------------|---------------------------------------------------------------|----------------|

| AD9874ABST<br>AD9874EB | −40°C to +85°C    | 48-Lead Thin Plastic Quad Flatpack (LQFP)<br>Evaluation Board | ST-48          |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9874 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -5-

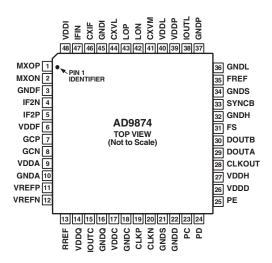

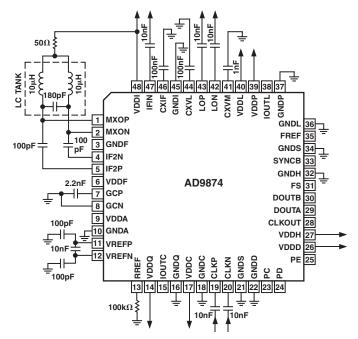

## PIN CONFIGURATION

## PIN FUNCTION DESCRIPTIONS

| Pin | Mnemonic | Description                                          | Pin | Mnemonic | Description                                            |

|-----|----------|------------------------------------------------------|-----|----------|--------------------------------------------------------|

| 1   | MXOP     | Mixer Output, Positive.                              | 27  | VDDH     | Positive Power Supply for Digital Interface.           |

| 2   | MXON     | Mixer Output, Negative.                              | 28  | CLKOUT   | Clock Output for SSI Port.                             |

| 3   | GNDF     | Ground for Front End of ADC.                         | 29  | DOUTA    | Data Output for SSI Port.                              |

| 4   | IF2N     | Second IF Input (to ADC), Negative.                  | 30  | DOUTB    | Data Output for SSI Port (Inverted) or                 |

| 5   | IF2P     | Second IF Input (to ADC), Positive.                  |     |          | SPI Port.                                              |

| 6   | VDDF     | Positive Power Supply for Front End of ADC.          | 31  | FS       | Frame Sync for SSI Port.                               |

| 7   | GCP      | Filter Capacitor for ADC Full-Scale Control.         | 32  | GNDH     | Ground for Digital Interface.                          |

| 8   | GCN      | Full-Scale Control Ground.                           | 33  | SYNCB    | Resets SSI and Decimator Counters;<br>Active Low.      |

| 9   | VDDA     | Positive Power Supply for ADC Back End.              | 34  | GNDS     | Substrate Ground.                                      |

| 10  | GNDA     | Ground for ADC Back End.                             | 35  | FREF     | Reference Frequency Input for Both                     |

| 11  | VREFP    | Voltage Reference, Positive.                         |     |          | Synthesizers.                                          |

| 12  | VREFN    | Voltage Reference, Negative.                         | 36  | GNDL     | Ground for LO Synthesizer.                             |

| 13  | RREF     | Reference Resistor: Requires 100 k $\Omega$ to       | 37  | GNDP     | Ground for LO Synthesizer Charge Pump.                 |

| 14  | VDDQ     | GNDA. Positive Power Supply for Clock Synthesizer.   | 38  | IOUTL    | LO Synthesizer Charge Pump Output Current Charge Pump. |

| 15  | IOUTC    | Clock Synthesizer Charge Pump Output Current.        | 39  | VDDP     | Positive Power Supply for LO Synthesizer Charge Pump.  |

| 16  | GNDQ     | Ground for Clock Synthesizer Charge                  | 40  | VDDL     | Positive Power Supply for LO Synthesizer.              |

|     |          | Pump.                                                | 41  | CXVM     | External Filter Capacitor; DC Output of                |

| 17  | VDDC     | Positive Power Supply for Clock Synthesizer.         |     |          | LNA.                                                   |

| 18  | GNDC     | Ground for Clock Synthesizer.                        | 42  | LON      | LO Input to Mixer and LO Synthesizer,<br>Negative.     |

| 19  | CLKP     | Sampling Clock Input/Clock VCO Tank, Positive.       | 43  | LOP      | LO Input to Mixer and LO Synthesizer, Positive.        |

| 20  | CLKN     | Sampling Clock Input/Clock VCO Tank, Negative.       | 44  | CXVL     | External Bypass Capacitor for LNA Power Supply.        |

| 21  | GNDS     | Substrate Ground.                                    | 45  | GNDI     | Ground for Mixer and LNA.                              |

| 22  | GNDD     | Ground for Digital Functions.                        | 46  | CXIF     | External Capacitor for Mixer V-I Con-                  |

| 23  | PC       | Clock Input for SPI Port.                            |     |          | verter Bias.                                           |

| 24  | PD       | Data I/O for SPI Port.                               | 47  | IFIN     | First IF Input (to LNA).                               |

| 25  | PE       | Enable Input for SPI Port.                           | 48  | VDDI     | Positive Power Supply for LNA and Mixer.               |

| 26  | VDDD     | Positive Power Supply for Internal Digital Function. |     | •        |                                                        |

-6-

REV. A

### **DEFINITION OF SPECIFICATIONS/TEST METHODS**

## Single-Sideband Noise Figure (SSB NF)

Noise figure (NF) is defined as the degradation in SNR performance (in dB) of an IF input signal after it passes through a component or system. It can be expressed with the equation

Noise Figure =

$$10 \times \log(SNR_{IN}/SNR_{OUT})$$

The term SSB is applicable for heterodyne systems containing a mixer. It indicates that the desired signal spectrum resides on only one side of the LO frequency (i.e., single sideband); thus a "noiseless" mixer has a noise figure of 3 dB.

The AD9874's SSB noise figure is determined by the equation

$$SSB NF = P_{IN} - \left\{10 \times \log(BW)\right\} - 174 dBm/Hz - SNR$$

where  $P_{IN}$  is the input power of an unmodulated carrier, BW is the noise measurement bandwidth,  $-174 \, dBm/Hz$  is the thermal noise floor at 293 K, and SNR is the measured signal-to-noise ratio in dB of the AD9874.

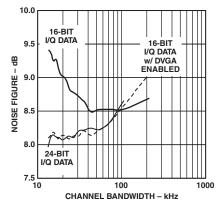

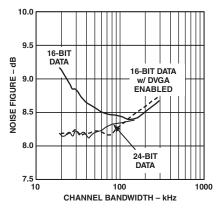

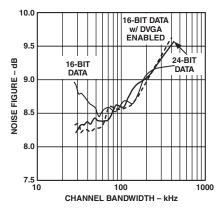

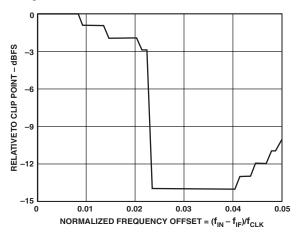

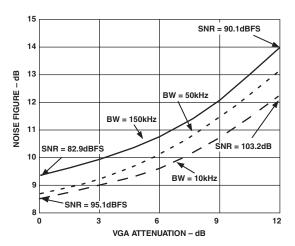

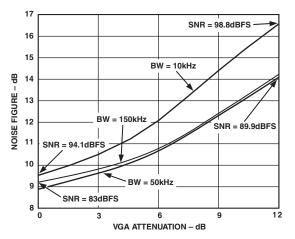

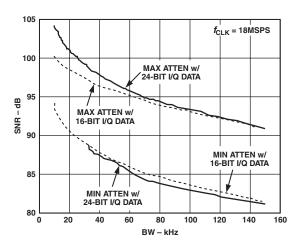

Note that  $P_{\rm IN}$  is set to –85 dBm to minimize any degradation in measured SNR due to phase noise from the RF and LO signal generators. The IF frequency, CLK frequency, and decimation factors are selected to minimize any spurious components falling within the measurement bandwidth. Note also that a bandwidth of 10 kHz is used for the data sheet specification. Refer to Figures 22a and 22b for an indication of how NF varies with BW. Also, refer to the TPCs to see how NF is affected by different operating conditions. All references to noise figures within this data sheet imply single-sideband noise figure.

### Input Third Order Intercept (IIP3)

IIP3 is a figure of merit used to determine a component's or system's susceptibility to intermodulation distortion (IMD) from its third order nonlinearities. Two unmodulated carriers at a specified frequency relationship  $(f_1 \text{ and } f_2)$  are injected into a nonlinear system exhibiting third order nonlinearities producing IMD components at  $2f_1 - f_2$  and  $2f_2 - f_1$ . IIP3 graphically represents the extrapolated intersection of the carrier's input power with the third order IMD component when plotted in dB. The difference in power (D in dBc) between the two carriers and the resulting third order IMD components can be determined from the equation

$$D = 2 \times (IIP3 - P_{IN})$$

## Dynamic Range (DR)

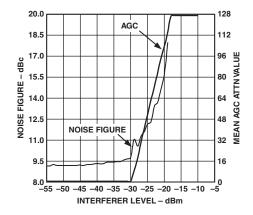

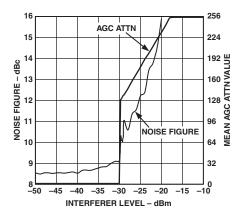

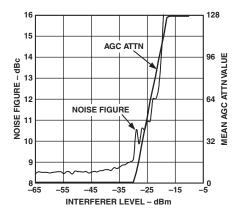

Dynamic range is the measure of a small target input signal  $(P_{TARGET})$  in the presence of a large unwanted interferer signal  $(P_{INTER})$ . Typically, the large signal will cause some unwanted characteristic of the component or system to degrade, thus making it unable to detect the smaller target signal correctly. In the case of the AD9874, it is often a degradation in noise figure at increased VGA attenuation settings that limits its dynamic range (refer to TPCs 15a, 15b, and 15c).

The test method for the AD9874 is as follows. The small target signal (an unmodulated carrier) is input at the center of the IF frequency, and its power level ( $P_{TARGET}$ ) is adjusted to achieve an  $SNR_{TARGET}$  of 6 dB. The power of the signal is then increased by 3 dB prior to injecting the interferer signal. The offset frequency of the interferer signal is selected so that aliases produced by the decimation filter's response as well as phase noise from the LO (due to reciprocal mixing) do not fall back within the measurement bandwidth. For this reason, an offset of 110 kHz was selected. The interferer signal (also an unmodulated carrier) is then injected into the input and its power level is increased to the point ( $P_{INTER}$ ) where the target signal SNR is reduced to 6 dB. The dynamic range is determined with the equation:

$$DR = P_{INTER} - P_{TARGET} + SNR_{TARGET}$$

Note that the AD9874's AGC is enabled for this test.

#### **IF Input Clip Point**

The IF input clip point is defined as 2 dB below the input power level ( $P_{\rm IN}$ ), resulting in the clipping of the AD9874's ADC. Unlike other linear components that typically exhibit a soft compression (characterized by its 1 dB compression point), an ADC exhibits a hard compression once its input signal exceeds its rated maximum input signal range. In the case of the AD9874, which contains a  $\Sigma$ - $\Delta$  ADC, hard compression should be avoided because it causes severe SNR degradation.

REV. A -7-

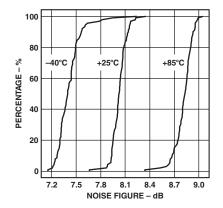

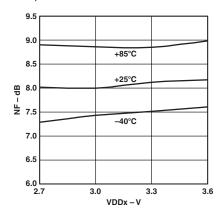

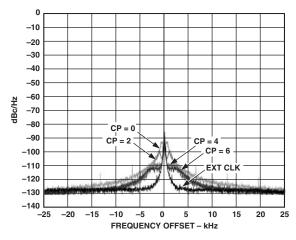

## **AD9874—Typical Performance Characteristics**

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDH = VDDH = VDDX, VDDQ = VDDP = 5.0 V,  $f_{CLK}$  = 18 MSPS,  $f_{IF}$  = 109.56 MHz,  $f_{LO}$  = 107.4 MHz,  $T_A$  = 25°C, L0 = -5 dBm, L0 and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)<sup>1</sup>

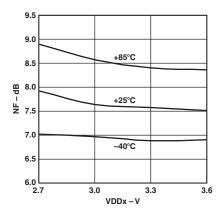

TPC 1a. CDF of SSB Noise Figure  $(VDDx = 3.0 V, High Bias^2)$

TPC 1b. SSB Noise Figure vs. Supply (High Bias<sup>2</sup>)

TPC 1c. SSB Noise Figure vs. Supply (Low Bias<sup>3</sup>)

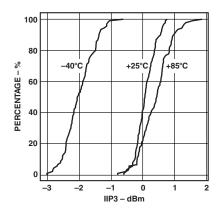

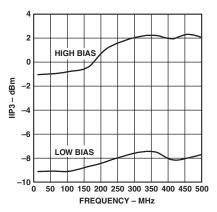

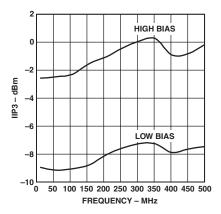

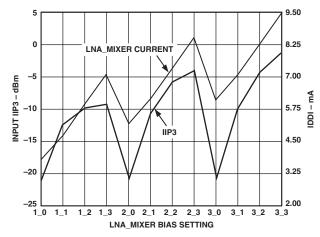

TPC 2a. CDF of IIP3 (VDDx = 3.0 V, High Bias<sup>2</sup>)

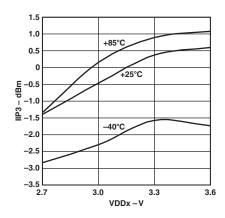

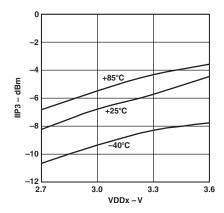

TPC 2b. IIP3 vs. Supply (High Bias<sup>2</sup>)

TPC 2c. IIP3 vs. Supply (Low Bias<sup>3</sup>)

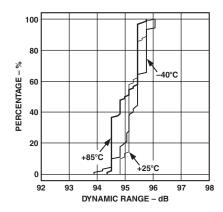

TPC 3a. CDF of Dynamic Range  $(VDDx = 3.0 V, High Bias^2)$

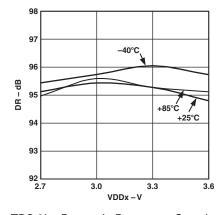

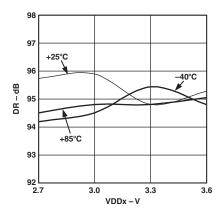

TPC 3b. Dynamic Range vs. Supply (High Bias<sup>2</sup>)

TPC 3c. Dynamic Range vs. Supply (Low Bias<sup>3</sup>)

-8- REV. A

<sup>&</sup>lt;sup>1</sup>Data taken with Toko FSLM series 10 μH inductors.

<sup>&</sup>lt;sup>2</sup>High Bias corresponds to LNA\_Mixer Setting of 33 in SPI Register 0x01.

<sup>&</sup>lt;sup>3</sup>Low Bias corresponds to LNA\_Mixer Setting of 12 in SPI Register 0x01.

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDH = VDDH = VDDX, VDDQ = VDDP = 5.0 V,  $f_{CLK}$  = 18 MSPS,  $f_{IF}$  = 109.56 MHz,  $f_{LO}$  = 107.4 MHz,  $f_{LO}$  = 25°C, LO = -5 dBm, LO and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)<sup>1</sup>

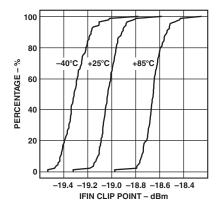

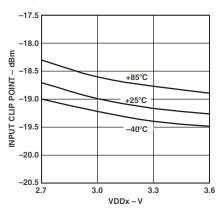

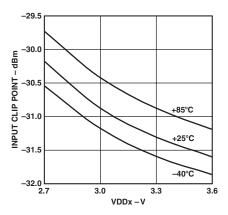

TPC 4a. CDF of Maximum VGA Attenuation Clip Point (VDDx = 3.0 V, High Bias<sup>2</sup>)

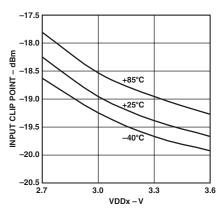

TPC 4b. Maximum VGA Attenuation Clip Point vs. Supply (High Bias<sup>2</sup>)

TPC 4c. Maximum VGA Attenuation Clip Point vs. Supply (Low Bias<sup>3</sup>)

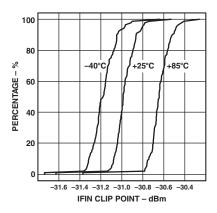

TPC 5a. CDF of Minimum VGA Attenuation Clip Point (VDDx = 3.0 V, High Bias<sup>2</sup>)

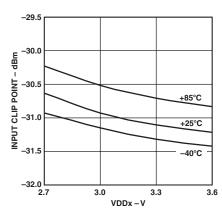

TPC 5b. Minimium VGA Attenuation Clip Point vs. Supply (High Bias²)

TPC 5c. Minimium VGA Attenuation Clip Point vs. Supply (Low Bias<sup>3</sup>)

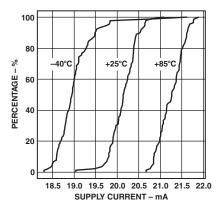

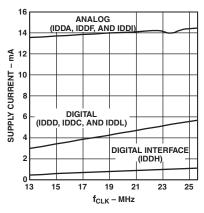

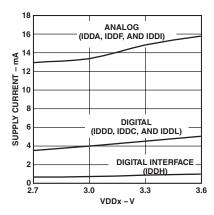

TPC 6a. CDF of Supply Current  $(VDDx = 3.0 \text{ V}, \text{High Bias}^2)$

TPC 6b. Supply Current vs.  $f_{CLK}$  (VDDx = 3.0 V, High Bias<sup>2</sup>)

TPC 6c. Supply Current vs. Supply (High Bias<sup>2</sup>)

REV. A -9-

$<sup>^{1}\</sup>text{Data}$  taken with Toko FSLM series 10  $\mu\text{H}$  inductors.

<sup>&</sup>lt;sup>2</sup>High Bias corresponds to LNA\_Mixer Setting of 33 in SPI Register 0x01.

$<sup>^3</sup> Low\ Bias\ corresponds\ to\ LNA\_Mixer\ Setting\ of\ 12$  in SPI Register 0x01.

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDD = VDDH = VDDX, VDDQ = VDDP = 5.0 V,  $f_{CLK}$  = 18 MSPS,  $f_{IF}$  = 109.56 MHz,  $f_{LO}$  = 107.4 MHz,  $T_A$  = 25°C, L0 = -5 dBm, L0 and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)<sup>1</sup>

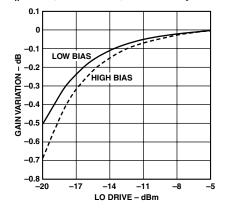

TPC 7a. Normalized Gain Variation vs. LO Drive (VDDx = 3.0 V)

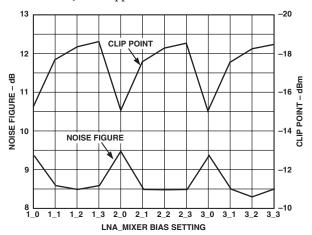

TPC 7b. Noise Figure and IMD vs. LO Drive (VDDx = 3.0 V)

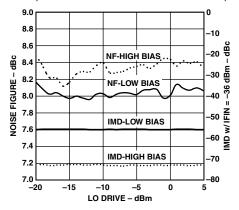

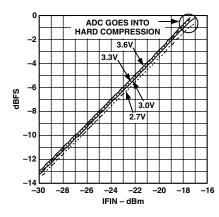

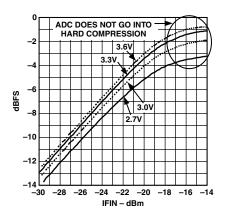

TPC 7c. Gain Compression vs. IFIN with 16 dB LNA Attenuator Enabled

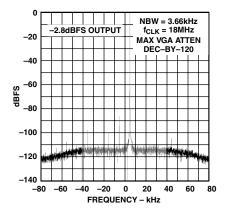

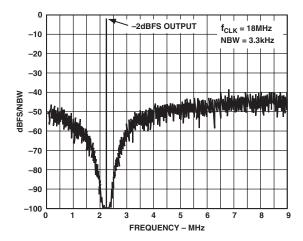

TPC 8a. Complex FFT of Baseband I/Q for Single-Tone (High Bias)

TPC 8b. Gain Compression vs. IFIN (High Bias<sup>2</sup>)

TPC 8c. Gain Compression vs. IFIN (Low Bias<sup>3</sup>)

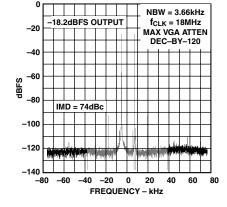

TPC 9a. Complex FFT of Baseband I/Q for Dual Tone IMD (High Bias with Each IFIN Tone @ -35 dBm)

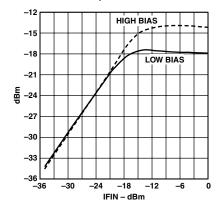

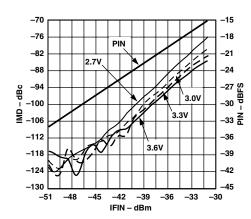

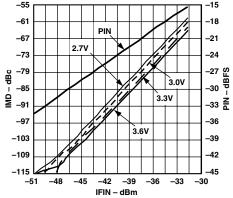

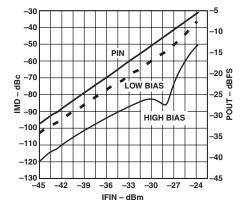

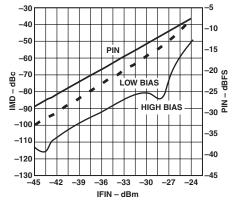

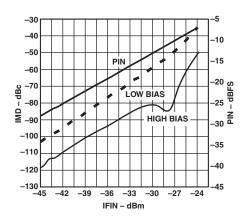

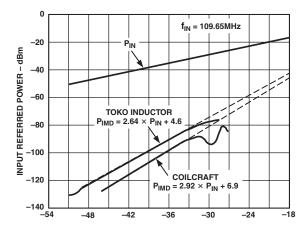

TPC 9b. IMD vs. IFIN (High Bias<sup>2</sup>)

TPC 9c. IMD vs. IFIN (Low Bias<sup>3</sup>)

–10– REV. A

<sup>&</sup>lt;sup>1</sup>Data taken with Toko FSLM series 10 μH inductors.

<sup>&</sup>lt;sup>2</sup>High Bias corresponds to LNA\_Mixer Setting of 33 in SPI Register 0x01.

<sup>&</sup>lt;sup>3</sup>Low Bias corresponds to LNA\_Mixer Setting of 12 in SPI Register 0x01.

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDH = VDDH = VDDX, VDDQ = VDDP = 5.0 V,  $f_{CLK}$  = 18 MSPS,  $f_{IF}$  = 109.56 MHz,  $f_{L0}$  = 107.4 MHz,  $f_{L0}$  = 25°C, L0 = -5 dBm, L0 and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)<sup>1</sup>

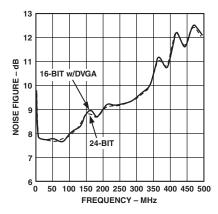

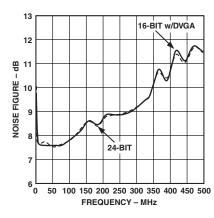

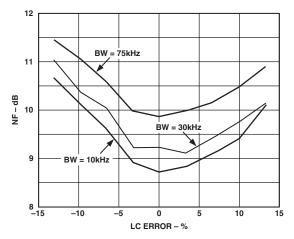

TPC 10a. Noise Figure vs. BW (Minimum Attenuation,  $f_{CLK} = 13$  MSPS)

TPC 10b. Noise Figure vs. BW (Minimum Attenuation,  $f_{CLK} = 18 \text{ MSPS}$ )

TPC 10c. Noise Figure vs. BW (Minimum Attenuation,  $f_{CLK} = 26$  MSPS)

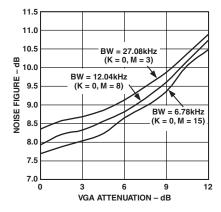

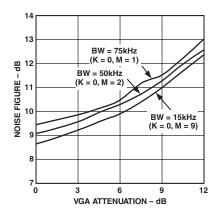

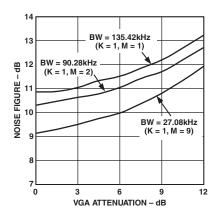

TPC 11a. Noise Figure vs. VGA Attenuation ( $f_{CLK} = 13 \text{ MSPS}$ )

TPC 11b. Noise Figure vs. VGA Attenuation ( $f_{CLK} = 18 \text{ MSPS}$ )

TPC 11c. Noise Figure vs. VGA Attenuation ( $f_{CLK} = 26 \text{ MSPS}$ )

TPC 12a. IMD vs. IFIN  $(f_{CLK} = 13 \text{ MSPS})$

TPC 12b. IMD vs. IFIN  $(f_{CLK} = 18 \text{ MSPS})$

TPC 12c. IMD vs. IFIN  $(f_{CLK} = 26 \text{ MSPS})$

REV. A -11-

$<sup>^{1}\</sup>text{Data}$  taken with Toko FSLM series 10  $\mu\text{H}$  inductors.

<sup>&</sup>lt;sup>2</sup>High Bias corresponds to LNA\_Mixer Setting of 33 in SPI Register 0x01.

$<sup>^3</sup> Low\ Bias\ corresponds\ to\ LNA\_Mixer\ Setting\ of\ 12$  in SPI Register 0x01.

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDH = VDDH = VDDX, VDDQ = VDDP = 5.0 V,  $f_{CLK}$  = 18 MSPS,  $f_{IF}$  = 109.56 MHz,  $f_{LO}$  = 107.4 MHz,  $T_A$  = 25°C, L0 = -5 dBm, L0 and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)<sup>1</sup>

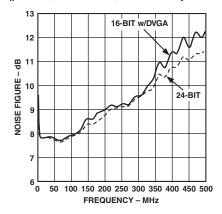

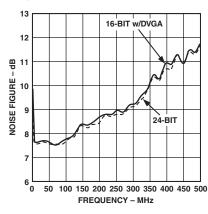

TPC 13a. Noise Figure vs. Frequency (Minimum Attenuation, f<sub>CLK</sub> = 18 MSPS, BW = 10 kHz, High Bias)

TPC 13b. Noise Figure vs. Frequency (Minimum Attenuation,  $f_{CLK} = 18$  MSPS, BW = 10 kHz, Low Bias)

TPC 13c. Input IP3 vs. Frequency  $(f_{CLK} = 18 \text{ MSPS})$

TPC 14a. Noise Figure vs. Frequency (Minimum Attenuation, f<sub>CLK</sub> = 26 MSPS, BW = 24 kHz, High Bias)

TPC 14b. Noise Figure vs. Frequency (Minimum Attenuation, f<sub>CLK</sub> = 26 MSPS, BW = 24 kHz, Low Bias)

TPC 14c. Input IP3 vs. Frequency  $(f_{CLK} = 26 \text{ MSPS})$

TPC 15a. Noise Figure vs. Interferer Level (16-Bit Data, BW = 12.5 kHz, AGCR = 1,  $f_{\text{INTERFERER}} = f_{\text{IF}} + 110 \text{ kHz}$ )

TPC 15b. Noise Figure vs. Interferer Level (16-Bit Data with DVGA, BW = 12.5 kHz, AGCR = 1,  $f_{INTERFERER}$  =  $f_{IF}$  + 110 kHz)

-12-

TPC 15c. Noise Figure vs. Interferer Level (24-Bit Data, BW = 12.5 kHz, AGCR = 1,  $f_{INTERFERER} = f_{IF} + 110$  kHz)

$<sup>^{1}\</sup>text{Data}$  taken with Toko FSLM series 10  $\mu\text{H}$  inductors.

<sup>&</sup>lt;sup>2</sup>High Bias corresponds to LNA\_Mixer Setting of 33 in SPI Register 0x01.

$<sup>^3</sup> Low\ Bias\ corresponds\ to\ LNA\_Mixer\ Setting\ of\ 12$  in SPI Register 0x01.

## **SERIAL PERIPHERAL INTERFACE (SPI)**

The serial peripheral interface (SPI) is a bidirectional serial port. It is used to load configuration information into the registers listed below as well as to read back their contents. Table I provides a list of the registers that may be programmed through the SPI port. Addresses and default values are given in hexadecimal form.

Table I. SPI Address Map

| Address<br>(Hex) | Bit<br>Breakdown                 | Width                 | Default Value    | Name                         | Description                                                                                                                                                                                                                                               |

|------------------|----------------------------------|-----------------------|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER            | CONTROL RI                       | EGISTE                | RS               |                              |                                                                                                                                                                                                                                                           |

| 0x00             | (7:0)                            | 8                     | 0xFF             | STBY                         | Standby Control Bits (REF, LO, CKO, CK, GC, LNAMX, Unused, and ADC).                                                                                                                                                                                      |

| 0x01             | (7:6)<br>(5:4)<br>(3:2)<br>(1:0) | 2<br>2<br>2<br>2<br>2 | 0<br>0<br>0<br>0 | LNAB<br>MIXB<br>CKOB<br>ADCB | LNA Bias Current (0 = 0.5 mA, 1 = 1 mA, 2 = 2 mA, 3 = 3 mA).<br>Mixer Bias Current (0 = 0.5 mA, 1 = 1.5 mA, 2 = 2.7 mA, 3 = 4 mA).<br>CK Oscillator Bias (0 = 0.25 mA, 1 = 0.35 mA, 2 = 0.40 mA, 3 = 0.65 mA)<br>Do not use.                              |

| 0x02             | (7:0)                            | 8                     | 0x00             | TEST                         | Factory Test Mode. Do not use.                                                                                                                                                                                                                            |

| AGC              |                                  |                       |                  |                              |                                                                                                                                                                                                                                                           |

| 0x03             | (7)<br>(6:0)                     | 1 7                   | 0<br>0x00        | ATTEN<br>AGCG(14:8)          | Apply 16 dB attenuation in the front end. AGC Attenuation Setting (7 MSB of a 15-Bit Unsigned Word).                                                                                                                                                      |

| 0x04             | (7:0)                            | 8                     | 0x00             | AGCG(7:0)                    | AGC Attenuation Setting (8 LSB of a 15-Bit Unsigned Word). Default corresponds to maximum gain.                                                                                                                                                           |

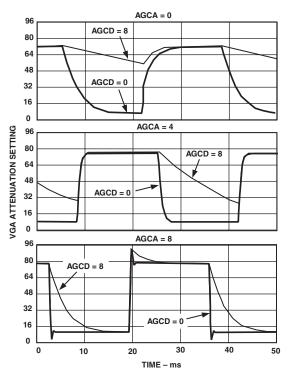

| 0x05             | (7:4)<br>(3:0)                   | 4 4                   | 0 0              | AGCA<br>AGCD                 | AGC Attack Bandwidth Setting. Default yields 50 Hz raw loop bandwidth. AGC Decay Time Setting. Default is decay time = attack time.                                                                                                                       |

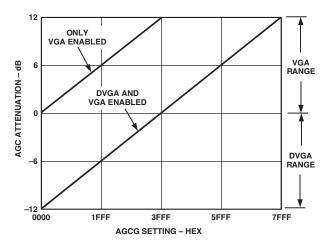

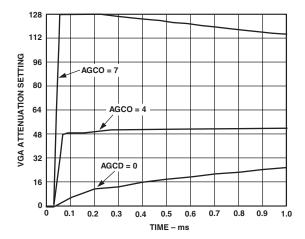

| 0x06             | (7)<br>(6:4)<br>(3)<br>(2:0)     | 1<br>3<br>1<br>3      | 0<br>0<br>0<br>0 | AGCV<br>AGCO<br>AGCF<br>AGCR | Enable digital VGA to increase AGC range by 12 dB.  AGC Overload Update Setting. Default is slowest update.  Fast AGC (Minimizes resistance seen between GCP and GCN).  AGC Enable/Reference Level (Disabled, 3 dB, 6 dB, 9 dB, 12 dB, 15 dB below Clip). |

| DECIMA           | TION FACTO                       | OR                    |                  |                              |                                                                                                                                                                                                                                                           |

| 0x07             | (7:5)<br>(4)<br>(3:0)            | 3<br>1<br>4           | 0 4              | Unused<br>K<br>M             | Decimation Factor = $60 \times (M + 1)$ , if K = 0; $48 \times (M + 1)$ , if K = 1. Default is Decimate-by-300.                                                                                                                                           |

| LO SYN           | THESIZER                         |                       |                  |                              |                                                                                                                                                                                                                                                           |

| 0x08             | (5:0)                            | 6                     | 0x00             | LOR(13:8)                    | Reference Frequency Divisor (6 MSB of a 14-Bit Word).                                                                                                                                                                                                     |

| 0x09             | (7:0)                            | 8                     | 0x38             | LOR(7:0)                     | Reference Frequency Divisor (8 LSB of a 14-Bit Word).<br>Default (56) yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.                                                                                                                                    |

| 0x0A             | (7:5)<br>(4:0)                   | 3 5                   | 0x5<br>0x00      | LOA<br>LOB(12:8)             | "A" Counter (Prescaler Control Counter). "B" Counter MSB (5 MSB of a 13-Bit Word). Default LOA and LOB values yield 300 kHz from 73.35 MHz to 2.25 MHz.                                                                                                   |

| 0x0B             | (7:0)                            | 8                     | 0x1D             | LOB(7:0)                     | "B" Counter LSB (8 LSB of a 13-Bit Word).                                                                                                                                                                                                                 |

| 0x0C             | (6)<br>(5)<br>(4:2)<br>(1:0)     | 1<br>1<br>3<br>2      | 0<br>0<br>0<br>3 | LOF<br>LOINV<br>LOI<br>LOTM  | Enable fast acquire. Invert charge pump (0 = source current to increase VCO frequency). Charge Pump Current in Normal Operation. $I_{PUMP}$ = (LOI + 1) × 0.625 mA. Manual Control of LO Charge Pump (0 = Off, 1 = Up, 2 = Down, 3 = Normal).             |

| 0x0D             | (5:0)                            | 4                     | 0x0              | LOFA(13:8)                   | LO Fast Acquire Time Unit (6 MSB of a 14-Bit Word).                                                                                                                                                                                                       |

| 0x0E             | (7:0)                            | 8                     | 0x04             | LOFA(7:0)                    | LO Fast Acquire Time Unit (8 LSB of a 14-Bit Word).                                                                                                                                                                                                       |

|                  |                                  |                       | -                |                              |                                                                                                                                                                                                                                                           |

REV. A -13-

Table I. SPI Address Map (continued)

| Address       | Bit                          |                  |                      |                             | dress Map (continued)                                                                                                                                                                                                                                        |

|---------------|------------------------------|------------------|----------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Hex)         | Breakdown                    | Width            | Default Value        | Name                        | Description                                                                                                                                                                                                                                                  |

| CLOCK         | SYNTHESIZE                   | R                |                      |                             |                                                                                                                                                                                                                                                              |

| 0x10          | (5:0)                        | 6                | 00                   | CKR(13:8)                   | Reference Frequency Divisor (6 MSB of a 14-Bit Word).                                                                                                                                                                                                        |

| 0x11          | (7:0)                        | 8                | 0x38                 | CKR(7:0)                    | Reference Frequency Divisor (8 LSB of a 14-Bit Word). Default yields 300 kHz from f <sub>REF</sub> =16.8 MHz; Min = 3, Max = 16383.                                                                                                                          |

| 0x12          | (4:0)                        | 5                | 0x00                 | CKN(12:8)                   | Synthesized Frequency Divisor (5 MSB of a 13-Bit Word).                                                                                                                                                                                                      |

| 0x13          | (7:0)                        | 8                | 0x3C                 | CKN(7:0)                    | Synthesized Frequency Divisor (8 LSB of a 13-Bit Word).  Default yields 300 kHz from f <sub>CLK</sub> = 18 MHz; Min = 3, Max = 8191.                                                                                                                         |

| 0x14          | (6)<br>(5)<br>(4:2)<br>(1:0) | 1<br>1<br>3<br>2 | 0<br>0<br>0<br>3     | CKF<br>CKINV<br>CKI<br>CKTM | Enable fast acquire. Invert charge pump (0 = source current to increase VCO frequency). Charge Pump Current in Normal Operation. $I_{PUMP} = (CKI + 1) \times 0.625 \text{ mA}$ . Manual Control of CLK Charge Pump (0 = Off, 1 = Up, 2 = Down, 3 = Normal). |

| 0x15          | (5:0)                        | 6                | 0x0                  | CKFA(13:8)                  | CK Fast Acquire Time Unit (6 MSB of a 14-Bit Word).                                                                                                                                                                                                          |

| 0x16          | (7:0)                        | 8                | 0x04                 | CKFA(7:0)                   | CK Fast Acquire Time Unit (8 LSB of a 14-Bit Word).                                                                                                                                                                                                          |

| SSI CON       | TROL                         |                  |                      |                             |                                                                                                                                                                                                                                                              |

| 0x18          | (7:0)                        | 8                | 0x12                 | SSICRA                      | SSI Control Register A. See Table III. (Default is FS and CLKOUT three-stated.)                                                                                                                                                                              |

| 0x19          | (7:0)                        | 8                | 0x07                 | SSICRB                      | SSI Control Register B. See Table III. (16-bit data, maximum drive strength.)                                                                                                                                                                                |

| 0x1A          | (3:0)                        | 4                | 1                    | SSIORD                      | Output Rate Divisor. $f_{CLKOUT} = f_{CLK}/SSIORD$ .                                                                                                                                                                                                         |

| ADC TU        | NING                         |                  |                      |                             |                                                                                                                                                                                                                                                              |

| 0x1C          | (1)<br>(0)                   | 1 1              | 0 0                  | TUNE_LC<br>TUNE_RC          | Perform tuning on the LC portion of the ADC (cleared when done).  Perform tuning on the RC portion of the ADC (cleared when done).                                                                                                                           |

| 0x1D          | (2:0)                        | 3                | 0                    | CAPL1(2:0)                  | Coarse Capacitance Setting for LC Tank (LSB is 25 pF, Differential).                                                                                                                                                                                         |

| 0x1E          | (5:0)                        | 6                | 0x00                 | CAPL0(5:0)                  | Fine Capacitance Setting for LC Tank (LSB is 0.4 pF, Differential).                                                                                                                                                                                          |

| 0x1F          | (7:0)                        | 8                | 0x00                 | CAPR                        | Capacitance Setting for RC Resonator (64 LSB of Fixed Capacitance).                                                                                                                                                                                          |

| TEST RI       | EGISTERS AN                  | D SPI PO         | RT READ ENAB         | LE                          |                                                                                                                                                                                                                                                              |

| 0x37-<br>0x39 | (7:0)                        | 8                | 0x00                 | TEST                        | Factory Test Mode. Do not use.                                                                                                                                                                                                                               |

| 0x3A          | (7:4, 2:0)<br>(3)            | 7                | 0x0<br>0             | TEST<br>SPIREN              | Factory Test Mode. Do not use.<br>Enable read from SPI port.                                                                                                                                                                                                 |

| 0x3B          | (7:4, 2:0)<br>(3)            | 7 1              | 0x0<br>0             | TEST<br>TRI                 | Factory Test Mode. Do not use.<br>Three-state DOUTB.                                                                                                                                                                                                         |

| 0x3C-<br>0x3E | (7:0)                        | 1                | 0x00                 | TEST                        | Factory Test Mode. Do not use.                                                                                                                                                                                                                               |

| 0x3F          | (7:0)                        | 8                | Subject to<br>Change | ID                          | Revision ID (Read-Only); A write of 0x99 to this register is equivalent to a power-on reset.                                                                                                                                                                 |

-14- REV. A

### **SERIAL PORT INTERFACE (SPI)**

The serial port of the AD9874 has 3-wire or 4-wire SPI capability, allowing read/write access to all registers that configure the device's internal parameters. The default 3-wire serial communication port consists of a clock (PC), peripheral enable (PE), and bidirectional data (PD) signal. The inputs to PC, PE, and PD contain a Schmitt trigger with a nominal hysteresis of 0.4 V centered about the digital interface supply (i.e., VDDH/2).

A 4-wire SPI interface can be enabled by setting the MSB of the SSICRB register (Reg. 0x19, Bit 7), resulting in the output data also appearing on the DOUTB pin. Note that since the default power-up state sets DOUTB low, bus contention is possible for systems sharing the SPI output line. To avoid any bus contention, the DOUTB pin can be three-stated by setting the fourth control bit in the three-state bit (Reg 0x3B, Bit 3). This bit can then be toggled to gain access to the shared SPI output line.

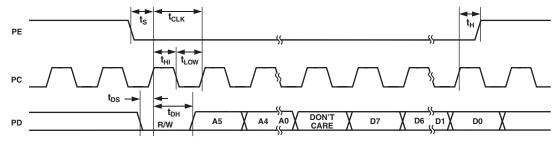

An 8-bit instruction header must accompany each read and write SPI operation. Only the write operation supports an auto-increment mode, allowing the entire chip to be configured in a single write operation. The instruction header is shown in Table II. It includes a read/not-write indicator bit, six address bits, and a don't care bit. The data bits immediately follow the instruction header for both read and write operations. Note that the address and data are always given MSB first.

**Table II. Instruction Header Information**

| MSB        |    |    |    |    |    |    | LSB |

|------------|----|----|----|----|----|----|-----|

| <b>I</b> 7 | I6 | I5 | I4 | I3 | I2 | I1 | I0  |

| R/W        | A5 | A4 | A3 | A2 | A1 | A0 | X   |

Figure 1a illustrates the timing requirements for a write operation to the SPI port. After the peripheral enable (PE) signal goes low, data (PD) pertaining to the instruction header is read on the rising edges of the clock (PC). To initiate a write operation, the read/not-write bit is set low. After the instruction header is read, the eight data bits pertaining to the specified register are

shifted into the data pin (PD) on the rising edge of the next eight clock cycles. PE stays low during the operation and goes high at the end of the transfer. If PE rises before the eight clock cycles have passed, the operation is aborted.

If PE stays low for an additional eight clock cycles, the destination address is incremented and another eight bits of data are shifted in. Again, should PE rise early, the current byte is ignored. By using this implicit addressing mode, the entire chip can be configured with a single write operation. Registers identified as being subject to frequent updates, namely those associated with power control and AGC operation, have been assigned adjacent addresses to minimize the time required to update them. Note that multibyte registers are big-endian (the most significant byte has the lower address) and are updated when a write to the least significant byte occurs.

Figure 1b illustrates the timing for a read operation to the SPI port. Although the AD9874 does not require read access for proper operation, it is often useful in the product development phase or for system authentication. Note that the readback enable bit (Register 0x3A, Bit 3) must be set for a read operation with a 3-wire SPI interface. After the peripheral enable (PE) signal goes low, data (PD) pertaining to the instruction header is read on the rising edges of the clock (PC). A read operation occurs if the read/not-write indicator is set high. After the address bits of the instruction header are read, the eight data bits pertaining to the specified register are shifted out of the data pin (PD) on the falling edges of the next eight clock cycles. If the 4-wire SPI interface is enabled, the eight data bits will also appear on the DOUTB pin with the same timing relationship as those appearing at PD. After the last data bit is shifted out, the user should return PE high, causing PD to become three-stated and return to its normal status as an input pin. Since the auto increment mode is not supported for read operations, an instruction header is required for each register read operation and PE must return high before initiating the next read operation.

Figure 1a. SPI Write Operation Timing

Figure 1b. SPI Read Operation Timing

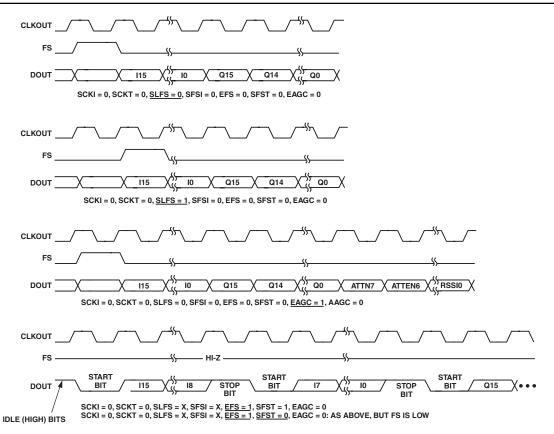

### **SYNCHRONOUS SERIAL INTERFACE (SSI)**

The AD9874 provides a high degree of programmability of its SSI output data format, control signals, and timing parameters to accommodate various digital interfaces. In a 3-wire digital interface, the AD9874 provides a frame sync signal (FS), a clock output (CLKOUT), and a serial data stream (DOUTA) signal to the host device. In a 2-wire interface, the frame sync information is embedded into the data stream, thus only CLKOUT and DOUTA output signals are provided to the host device. The SSI control registers are SSICRA, SSICRB, and SSIORD. Table III shows the different bit fields associated with these registers.

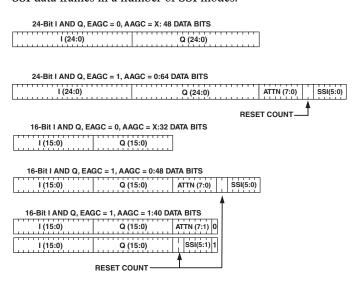

The primary output of the AD9874 is the converted I and Q demodulated signal available from the SSI port as a serial bit stream contained within a frame. The output frame rate is equal to the modulator clock frequency (f<sub>CLK</sub>) divided by the digital filter's decimation factor that is programmed in the Decimator Register (0x07). The bit stream consists of an I word followed by a Q word, where each word is either 24 bits or 16 bits long and is given MSB first in twos complement form. Two optional bytes may also be included within the SSI frame following the Q word. One byte contains the AGC attenuation and the other byte contains both a count of modulator reset events and an estimate of the received signal amplitude (relative to full scale of the AD9874's ADC). Figure 2 illustrates the structure of the SSI data frames in a number of SSI modes.

Figure 2. SSI Frame Structure

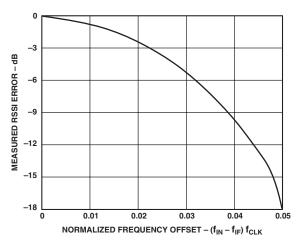

The two optional bytes are output if the EAGC bit of SSICRA is set. The first byte contains the 8-bit attenuation setting (0 = no attenuation, 255 = 24 dB of attenuation), while the second byte contains a 2-bit reset field and 6-bit received signal strength field. The reset field contains the number of modulator reset events since the last report, saturating at 3. The received signal strength (RSSI) field is a linear estimate of the signal strength at the output of the first decimation stage; 60 corresponds to a full-scale signal.

The two optional bytes follow the I and Q data as a 16-bit word provided that the AAGC bit of SSICRA is not set. If the AAGC bit is set, the two bytes follow the I and Q data in an alternating fashion. In this alternate AGC data mode, the LSB of the byte containing the AGC attenuation is a 0, while the LSB of the byte containing reset and RSSI information is always a 1.

In a 2-wire interface, the embedded frame sync bit (EFS) within the SSICRA register is set to 1. In this mode, the framing information is embedded in the data stream, with each eight bits of data surrounded by a start bit (low) and a stop bit (high), and each frame ends with at least 10 high bits. FS remains either low or three-stated (default), depending on the state of the SFST bit. Other control bits can be used to invert the frame sync (SFSI), to delay the frame sync pulse by one clock period (SLFS), to invert the clock (SCKI), or to three-state the clock (SCKT). Note that if EFS is set, SLFS is a don't care.

Table III. SSI Control Registers

| Name                                                                           | Width | Default | Description                                                                                |  |  |

|--------------------------------------------------------------------------------|-------|---------|--------------------------------------------------------------------------------------------|--|--|

| SSICRA (ADDR = 0x1                                                             |       |         | AAGC EAGC EFS SFST SFST SFSI SLFS SCKT                                                     |  |  |

| AAGC                                                                           | 1     | 0       | Alternate AGC Data Bytes.                                                                  |  |  |

| EAGC                                                                           | 1     | 0       | Embed AGC data.                                                                            |  |  |

| EFS                                                                            | 1     | 0       | Embed frame sync.                                                                          |  |  |

| SFST                                                                           | 1     | 1       | Three-state frame sync.                                                                    |  |  |

| SFSI                                                                           | 1     | 0       | Invert frame sync.                                                                         |  |  |

| SLFS                                                                           | 1     | 0       | Late Frame Sync $(1 = \text{Late}, 0 = \text{Early}).$                                     |  |  |

| SCKT                                                                           | 1     | 1       | Three-state CLKOUT.                                                                        |  |  |

| SCKI                                                                           | 1     | 0       | Invert CLKOUT.                                                                             |  |  |

| SSICRB (ADDR = 0x19                                                            |       |         | 00                                                                                         |  |  |

| 4_SPI                                                                          | 1     | 0       | Enable 4-Wire SPI Interface for SPI Read operation via DOUTB.                              |  |  |

| DW                                                                             | 1     | 0       | I/Q Data-Word Width (0 = 16 bit, 1 bit–24 bit).<br>Automatically 16-bit when the AGCV = 1. |  |  |

| DS                                                                             | 3     | 7       | FS, CLKOUT, and DOUT Drive Strength.                                                       |  |  |

| SSIORD (ADDR = $0x1A$ ) $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |       |         |                                                                                            |  |  |

| DIV                                                                            | 4     | 1       | Output Bit Rate Divisor $f_{CLKOUT} = f_{CLK}/SSIORD$ .                                    |  |  |

The SSIORD register controls the output bit rate ( $f_{\rm CLKOUT}$ ) of the serial bit stream.  $f_{\rm CLKOUT}$  can be set to equal the modulator clock frequency ( $f_{\rm CLK}$ ) or an integer fraction of it. It is equal to  $f_{\rm CLK}$  divided by the contents of the SSIORD register. Note that  $f_{\rm CLKOUT}$  should be chosen such that it does not introduce harmful spurs within the pass band of the target signal. Users must verify that the output bit rate is sufficient to accommodate the required number of bits per frame for a selected word size and decimation factor. Idle (high) bits are used to fill out each frame.

–16– REV. A

Figure 3a. SSI Timing for Several SSICRA Settings with 16-Bit I/O Data

Table IV.

Number of Bits per Frame for Different SSICR Settings

| DW         | EAGC | EFS | AAGC | Number of Bits<br>per Frame |

|------------|------|-----|------|-----------------------------|

| 0 (16-bit) | 0    | 0   | NA   | 32                          |

|            | 0    | 1   | NA   | 49*                         |

|            | 1    | 0   | 0    | 48                          |

|            | 1    | 0   | 1    | 40                          |

|            | 1    | 1   | 0    | 69*                         |

|            | 1    | 1   | 1    | 59*                         |

| 1 (24-bit) | 0    | 0   | NA   | 48                          |

|            | 0    | 1   | NA   | 69*                         |

|            | 1    | 0   | 0    | 64                          |

|            | 1    | 0   | 1    | 56                          |

|            | 1    | 1   | 0    | 89*                         |

|            | 1    | 1   | 1    | 79*                         |

<sup>\*</sup>The number of bits per frame with embedded frame sync (EFS = 1) assume at least 10 idle bits are desired.

The maximum SSIORD setting can be determined by the equation

$$SSIORD \le TRUNC\{(Dec. Factor) /$$

$$(# of Bits per Frame)\}$$

(1)

where TRUNC is the truncated integer value.

Table IV lists the number of bits within a frame for 16-bit and 24-bit output data formats for all of the different SSICR settings. The decimation factor is determined by the contents of Register 0x07.

An example helps illustrate how the maximum SSIORD setting is determined. Suppose a user selects a decimation factor of 600 (Register 0x07, K = 0, M = 9) and prefers a 3-wire interface with a dedicated frame sync (EFS = 0) containing 24-bit data (DW = 1) with nonalternating embedded AGC data included (EAGC = 1, AAGC = 0). Referring to Table IV, each frame will consist of 64 data bits. Using Equation 1, the maximum SSIORD setting is 9 (= TRUNC(600/64)). Thus, the user can select any SSIORD setting between 1 and 9.

Figure 3a illustrates the output timing of the SSI port for several SSI control register settings with 16-bit I/Q data, while Figure 3b shows the associated timing parameters. Note that the same timing relationship holds for 24-bit I/Q data, with the exception that I and Q word lengths now become 24 bits. In the default mode of the operation, data is shifted out on rising edges of CLKOUT after a pulse equal to a clock period is output from the Frame Sync (FS) pin. As described above, the output data consists of a 16- or 24-bit I sample followed by a 16- or 24-bit Q sample, plus two optional bytes containing AGC and status information.

Figure 3b. Timing Parameters for SSI Timing\* \*Timing parameters also apply to inverted CLKOUT or FS modes, with  $t_{\rm DV}$  relative to the falling edge of the CLK and/or FS.

REV. A -17-

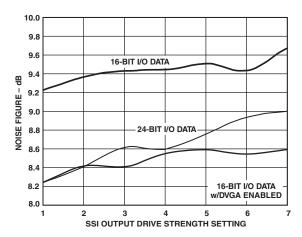

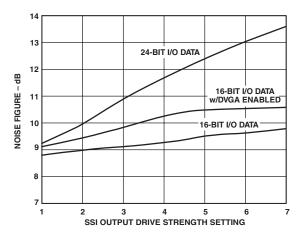

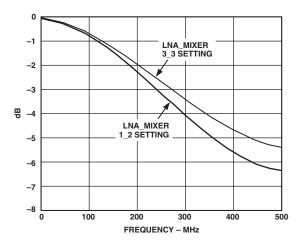

The AD9874 also provides the means for controlling the switching characteristics of the digital output signals via the DS (drive strength) field of the SSICRB. This feature is useful in limiting switching transients and noise from the digital output that may ultimately couple back into the analog signal path, potentially degrading the AD9874's sensitivity performance. Figures 3c and 3d show how the NF can vary as a function of the SSI setting for an IF frequency of 109.65 MHz. The following two observations can be made from these figures:

- The NF becomes more sensitive to the SSI output drive strength level at higher signal bandwidth settings.

- The NF is dependent on the number of bits within an SSI frame, becoming more sensitive to the SSI output drive strength level as the number of bits is increased. As a result, one should select the lowest possible SSI drive strength setting that still meets the SSI timing requirements.

Figure 3c. NF vs. SSI Output Drive Strength (VDDx = 3.0 V,  $f_{CLK} = 18 MSPS$ , BW = 10 kHz)

Figure 3d. NF vs. SSI Output Drive Strength (VDDx = 3.0 V,  $f_{CLK} = 18$  MSPS, BW = 75 kHz)

Table V lists the typical output rise/fall times as a function of DS for a 10 pF load. Rise/fall times for other capacitor loads can be determined by multiplying the typical values presented in Table V by a scaling factor equal to the desired capacitive load divided by 10 pF.

Table V. Typical Rise/Fall Times (±25%) with a 10 pF Capacitive Load for Each DS Setting

| DS | Typ (ns) |

|----|----------|

| 0  | 13.5     |

| 1  | 7.2      |

| 2  | 5.0      |

| 3  | 3.7      |

| 4  | 3.2      |

| 5  | 2.8      |

| 6  | 2.3      |

| 7  | 2.0      |

## **Synchronization Using SYNCB**

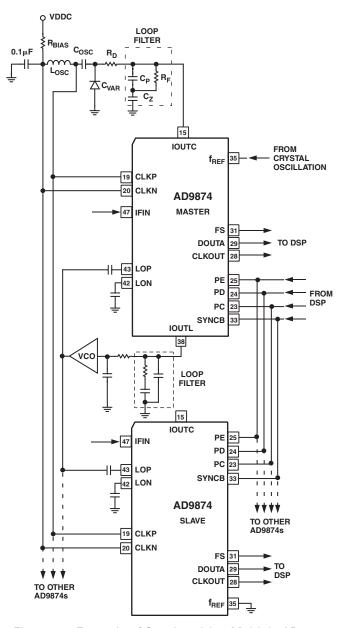

Many applications require the ability to synchronize one or more AD9874 in a way that causes the output data to be precisely aligned to an external asynchronous signal. For example, receiver applications employing diversity often require synchronization of multiple AD9874 digital outputs. Satellite communication applications using TDMA methods may require synchronization between payload bursts to compensate for reference frequency drift and Doppler effects.

SYNCB can be used for this purpose. It is an active-low signal that clears the clock counters in both the decimation filter and the SSI port. The counters in the clock synthesizers are not reset because it is presumed that the CLK signals of multiple chips would be connected. SYNCB also resets the modulator, resulting in a large-scale impulse that must propagate through the AD9874's digital filter and SSI data formatting circuitry before recovering valid output data. At a result, data samples unaffected by this SYNCB induced impulse can be recovered 12 output data samples after SYNCB goes high (independent of the decimation factor).

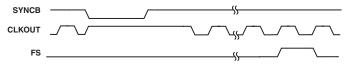

Figure 4a shows the timing relationship between SYNCB and the SSI port's CLKOUT and FS signals. SYNCB is an asynchronous active-low signal that must remain low for at least half an input clock period (i.e.,  $1/(2 \times f_{CLK})$ ). CLKOUT remains high while FS remains low upon SYNCB going low. CLKOUT will become active within one to two output clock periods upon SYNCB returning high. FS will reappear several output cycles later, depending on the digital filter's decimation factor and the SSIORD setting. Note that for any decimation factor and SSIORD setting, this delay is fixed and repeatable. To verify proper synchronization, the FS signals of the multiple AD9874 devices should be monitored.

Figure 4a. SYNCB Timing

## Interfacing to DSPs

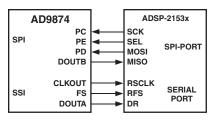

The AD9874 connects directly to an Analog Devices programmable digital signal processor (DSP). Figure 4b illustrates an example with the Blackfin® series of ADSP-2153x processors. The Blackfin DSP series is a family of 16-bit products optimized for telecommunications applications with its dynamic power management feature, making it well suited for portable radio products. The code compatible family members share the fundamental core attributes of high performance, low power consumption, and the ease-of-use advantages of a microcontroller instruction set.

–18– REV. A

Figure 4b. Example of AD9874 and ADSP-2153x Interface

As shown in Figure 4b, AD9874's synchronous serial interface (SSI) links the receive data stream to the DSP's Serial Port (SPORT). For AD9874 setup and register programming, the device connects directly to ADSP-2153x's SPI port. Dedicated select lines (SEL) allow the ADSP-2153x to program and read back registers of multiple devices using only one SPI port. The DSP driver code pertaining to this interface is available on the AD9874 web page (http://www.analog.com/Analog\_Root/static/techSupport/designTools/evaluationBoards/ad9874blackfinInterfacing.html).

### **POWER CONTROL**

To allow power consumption to be minimized, the AD9874 possesses numerous SPI programmable power-down and bias control bits. The AD9874 powers up with all of its functional blocks placed into a standby state (i.e., STBY register default is 0xFF). Each major block may then be powered up by writing a 0 to the appropriate bit of the STBY register. This scheme provides the greatest flexibility for configuring the IC to a specific application as well as for tailoring the IC's power-down and wake-up characteristics. Table VI summarizes the function of each of the STBY bits. Note that when all the blocks are in standby, the master reference circuit is also put into standby, and thus the current is reduced by a further 0.4 mA.

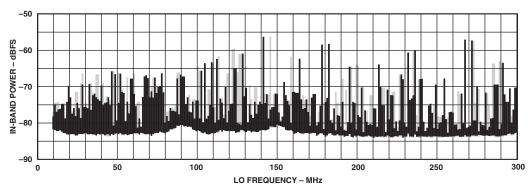

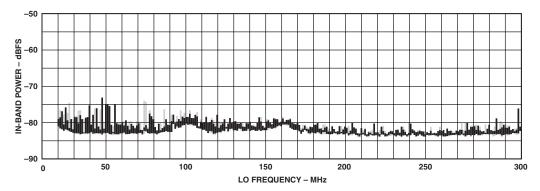

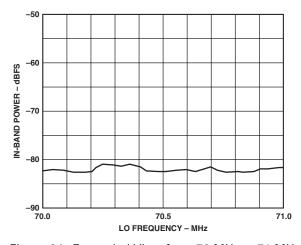

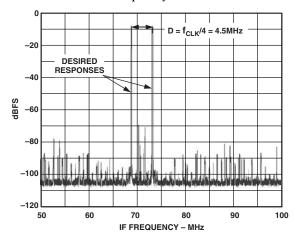

Table VI. Standby Control Bits