# OBSOLETE PRODUCT POSSIBLE SUBSTITUTE PRODUCT ICM7244B

# DATASHEET

ICM7244

8-Character, Microprocessor Compatible, LED Display Decoder Driver

FN6675 Rev.1.00 Jan 22, 2009

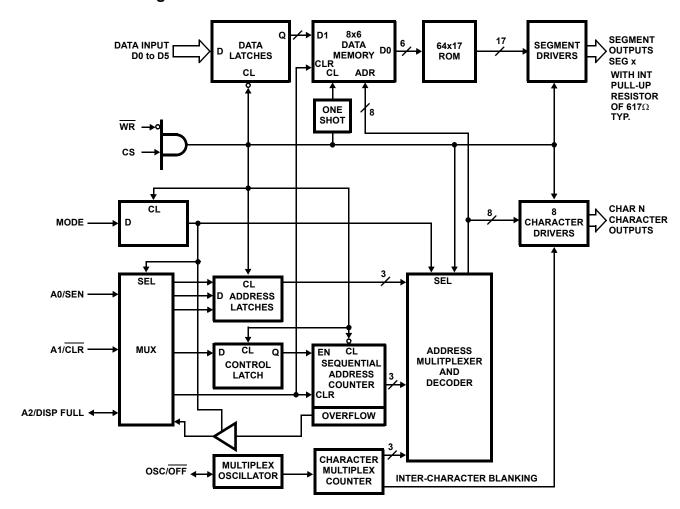

The ICM7244 is an 8-character, alphanumeric display driver and controller which provides all the circuitry required to interface a microprocessor or digital system to a 16-segment display with internal pull-up resistors. It is primarily intended for use in microprocessor systems, where it minimizes hardware and software overhead. Incorporated on-chip are a 64-character ASCII decoder, 8x6 memory, high power character and segment drivers, and the multiplex scan circuitry.

6-bit ASCII data to be displayed is written into the memory directly from the microprocessor data bus. Data location depends upon the selection of either **Sequential** (MODE = 1) or **Random** access mode (MODE = 0). In the **Sequential Access** mode the first entry is stored in the lowest location and displayed in the "left-most" character position. Each subsequent entry is automatically stored in the next higher location and displayed to the immediate "right" of the previous entry. A DISPlay FULL signal is provided after 8 entries; this signal can be used for cascading devices together. A  $\overline{\text{CLR}}$  pin is provided to clear the memory and reset the location counter. The **Random Access** mode allows the processor to select the memory address and display digit for each input word.

The character multiplex scan runs whenever data is not being entered. It scans the memory and CHARacter drivers, and ensures that the decoding from memory to display is done in the proper sequence. Intercharacter blanking is provided to avoid display ghosting.

### Features

- · 6-Segment Fonts with Decimal Point

- Has Internal Pull-Up Resistors of  $617\Omega$  Typ.

- Mask Programmable for Other Font-Sets Up to 64 Characters

- · Microprocessor Compatible

- · Directly Drives LED Common Cathode Displays

- · Cascadable Without Additional Hardware

- Standby Feature Turns Display Off; Puts Chip in Low Power Mode

- Sequential Entry or Random Entry of Data Into Display

- · Single +5V Operation

- Character and Segment Drivers, All MUX Scan Circuitry, 8x6 Static Memory and 64-Character ASCII Font Generator Included On-Chip

- · Pb-Free (RoHS Compliant)

## Ordering Information

| PART NUMBER<br>(Note) | PART MARKING   | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)       | PKG. DWG. # |  |

|-----------------------|----------------|---------------------|----------------------------|-------------|--|

| ICM7244AIM44Z         | ICM7244 AIM44Z | -25°C to +85°C      | 44 Ld MQFP                 | Q44.10x10   |  |

| ICM7244AIM44ZT        | ICM7244 AIM44Z | -25°C to +85°C      | 44 Ld MQFP (Tape and Reel) | Q44.10x10   |  |

<sup>\*</sup>Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

RENESAS

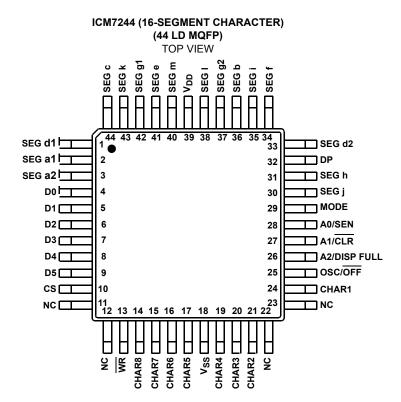

## **Pinout**

# Functional Block Diagram

## **Absolute Maximum Ratings**

| Supply Voltage V <sub>DD</sub> - V <sub>SS</sub> | +6.0V                                            |

|--------------------------------------------------|--------------------------------------------------|

| Input Voltage (Any Terminal)                     | V <sub>DD</sub> + 0.3V to V <sub>SS</sub> - 0.3V |

| CHARacter Output Current                         |                                                  |

| SEGment Output Current                           |                                                  |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | θ <sub>JA</sub> (°C/W) |

|------------------------------------------------|------------------------|

| MQFP Package                                   | 70                     |

| Maximum Storage Temperature Range              | 65°C to +150°C         |

| Pb-free reflow profile                         | see link belov         |

| http://www.intersil.com/pbfree/Pb-FreeReflow.i | asp                    |

## **Operating Conditions**

Temperature Range . . . . . . . . . . . . . . . . . -25°C to +85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications  $V_{DD}$  = 5V,  $V_{SS}$  = 0V,  $T_A$  = +25°C, Unless Otherwise Specified

| PARAMETER SYMBOL TEST CONDITIONS                    |                   | MIN                                                                 | TYP  | MAX  | UNITS |    |

|-----------------------------------------------------|-------------------|---------------------------------------------------------------------|------|------|-------|----|

| DC CHARACTERISTICS                                  |                   |                                                                     |      | "    |       | '  |

| Supply Voltage (V <sub>DD</sub> - V <sub>SS</sub> ) | V <sub>SUPP</sub> |                                                                     | 4.75 | 5.0  | 5.25  | V  |

| Operating Supply Current                            | I <sub>DD</sub>   | V <sub>SUPP</sub> = 5.25V, 10 Segments ON, All 8 Characters         | -    | 180  | -     | mA |

| Quiescent Supply Current                            | I <sub>STBY</sub> | $V_{SUPP}$ = 5.25V, OSC/ $\overline{OFF}$ Pin < 0.5V, CS = $V_{SS}$ | -    | 30   | 250   | μA |

| Input High Voltage                                  | V <sub>IH</sub>   |                                                                     | 2    | -    | -     | V  |

| Input Low Voltage                                   | V <sub>IL</sub>   |                                                                     | -    | -    | 0.8   | V  |

| Input Current                                       | I <sub>IN</sub>   |                                                                     | -10  | -    | +10   | μA |

| CHARacter Drive Current                             | I <sub>CHAR</sub> | V <sub>SUPP</sub> = 5V, V <sub>OUT</sub> = 1V                       | 140  | 190  | -     | mA |

| CHARacter Leakage Current                           | ICHLK             |                                                                     | -    | -    | 100   | μA |

| SEGment Drive Current                               | I <sub>SEG</sub>  | V <sub>SUPP</sub> = 5V, V <sub>OUT</sub> = 2.5V                     | 3.3  | 4.5  | 5.5   | mA |

| SEGment Leakage Current                             | I <sub>SLK</sub>  |                                                                     | -    | 0.01 | 10    | μA |

| DISPlay FULL Output Low                             | V <sub>OL</sub>   | I <sub>OL</sub> = 1.6mA                                             | -    | -    | 0.4   | V  |

| DISPlay FULL Output High                            | V <sub>OH</sub>   | I <sub>IH</sub> = 100μA                                             | 2.4  | -    | -     | V  |

| Display Scan Rate                                   | f <sub>DS</sub>   |                                                                     | -    | 400  | -     | Hz |

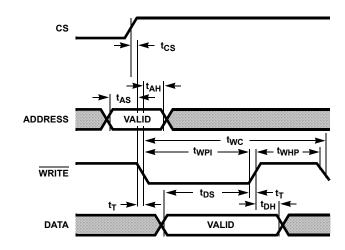

Electrical Specifications Drive levels 0.4V and 2.4V, timing measured at 0.8V and 2.0V.  $V_{DD}$  = 5V,  $T_A$  = +25°C, Unless Otherwise Specified

| PARAMETER                           | SYMBOL           | TEST CONDITIONS | MIN | TYP  | MAX | UNITS |

|-------------------------------------|------------------|-----------------|-----|------|-----|-------|

| AC CHARACTERISTICS                  |                  |                 | •   |      |     | •     |

| WR, CLeaR Pulse Width Low           | t <sub>WPI</sub> |                 | 300 | 250  | -   | ns    |

| WR, CLeaR Pulse Width High (Note 2) | twpH             |                 | -   | 250  | -   | ns    |

| Data Hold Time                      | t <sub>DH</sub>  |                 | 0   | -100 | -   | ns    |

| Data Setup Time                     | t <sub>DS</sub>  |                 | 250 | 150  | -   | ns    |

| Address Hold Time                   | t <sub>AH</sub>  |                 | 125 | -    | -   | ns    |

| Address Setup Time                  | t <sub>AS</sub>  |                 | 40  | 15   | -   | ns    |

| CS Setup Time                       | tcs              |                 | 0   | -    | -   | ns    |

| Pulse Transition Time               | t <sub>T</sub>   |                 | -   | -    | 100 | ns    |

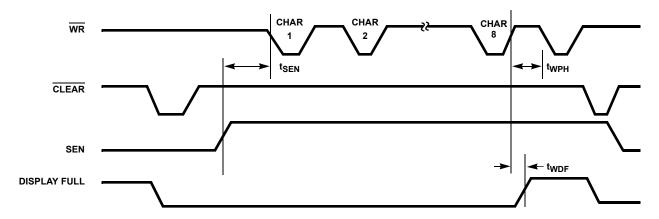

| SEN Setup Time                      | t <sub>SEN</sub> |                 | 0   | -25  | -   | ns    |

| Display Full Delay                  | t <sub>WDF</sub> |                 | 760 | 540  | -   | ns    |

## Capacitance

| PARAMETER          | SYMBOL          | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------|-----------------|-----------------|-----|-----|-----|-------|

| Input Capacitance  | C <sub>IN</sub> | (Note 3)        | -   | 5   | -   | pF    |

| Output Capacitance | CO              | (Note 3)        | -   | 5   | -   | pF    |

- 2. In Sequential mode  $\overline{WR}$  high must be  $\geq T_{SEN} + T_{WDF}$ .

- 3. For design reference only, not tested.

# **Timing Waveforms**

FIGURE 1. RANDOM ACCESS TIMING

FIGURE 2. SEQUENTIAL ACCESS MODE TIMING (MODE = 1)

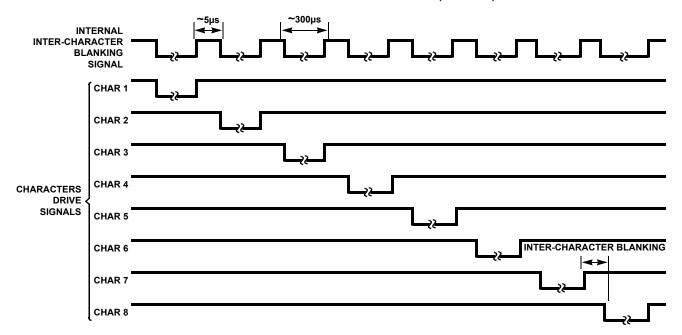

FIGURE 3. DISPLAY CHARACTERS MULTIPLEX TIMING DIAGRAM

# Pin Descriptions

| SIGNAL                                                                                                                                           | PIN                                   | FUNCTION                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 - D5                                                                                                                                          | 4 thru 9                              | 6-Bit ASCII Data input pins (active high).                                                                                                                                                                                                                                                                   |

| CS                                                                                                                                               | 10                                    | Chip Select from µP address decoder, etc.                                                                                                                                                                                                                                                                    |

| WR                                                                                                                                               | 13                                    | WRite pulse input pin (active low). For an active high write pulse, CS can be used.                                                                                                                                                                                                                          |

| MODE                                                                                                                                             | 29                                    | Selects data entry MODE. High selects <b>Sequential Access (SA)</b> mode where first entry is displayed in "leftmost" character and subsequent entries appear to the "right". Low selects the <b>Random Access (RA)</b> mode where data is displayed on the character addressed via A0 thru A2 Address pins. |

| A0/SEN                                                                                                                                           | 28                                    | In <b>RA</b> mode it is the LSB of the character Address. In <b>SA</b> mode it is used for cascading devices for displays of more than 8 characters (active high enables device controller).                                                                                                                 |

| A1/CLR                                                                                                                                           | 27                                    | In <b>RA</b> mode this is the second bit of the address. In <b>SA</b> mode, a low input will CLeaR the Serial Address Counter, the Data Memory and the display.                                                                                                                                              |

| A2/DISP FULL                                                                                                                                     | 26                                    | In <b>RA</b> mode this is the MSB of the Address. In <b>SA</b> mode, the output goes high after 8 entries, indicating DISPlay FULL.                                                                                                                                                                          |

| OSC/OFF                                                                                                                                          | 25                                    | OSCillator input pin. Adding capacitance to V <sub>DD</sub> will lower the internal oscillator frequency. An external oscillator can be applied to this pin. A low at this input sets the device into a (shutdown) mode, shutting OFF the display and oscillator but retaining data stored in memory.        |

| SEG d1, SEG a1,<br>SEG a2,<br>SEG j, SEG h, DP,<br>SEG d2, SEG f,<br>SEG i, SEG b, SEG<br>g2, SEG I,<br>SEG m, SEG e,<br>SEG g1, SEG k,<br>SEG c | 1 thru 3,<br>30 thru 38<br>40 thru 44 | SEGment driver outputs.                                                                                                                                                                                                                                                                                      |

| CHAR8 thru<br>CHAR5,<br>CHAR4 thru<br>CHAR2,<br>CHAR1                                                                                            | 14 thru 17,<br>19 thru 21,<br>24      | CHARacter driver outputs.                                                                                                                                                                                                                                                                                    |

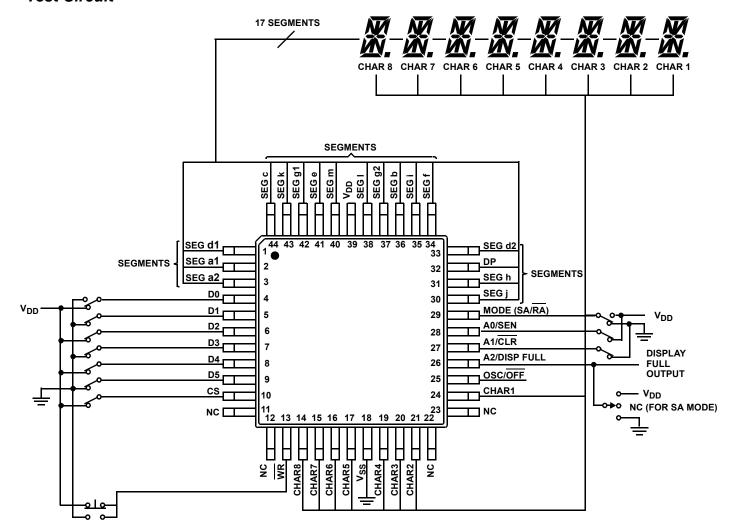

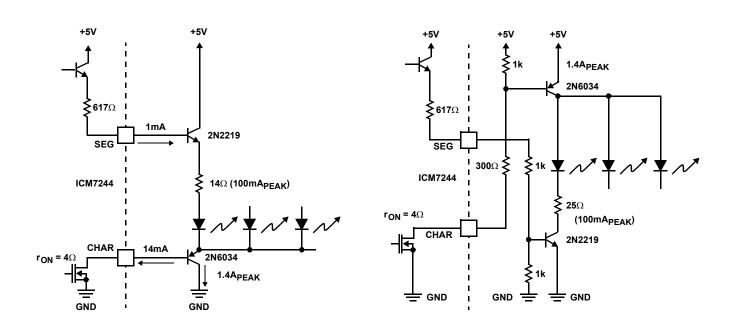

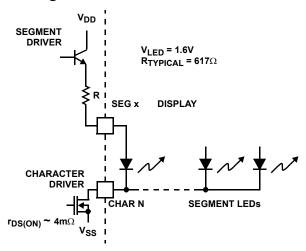

# **Test Circuit**

FIGURE 4.

# **Typical Applications**

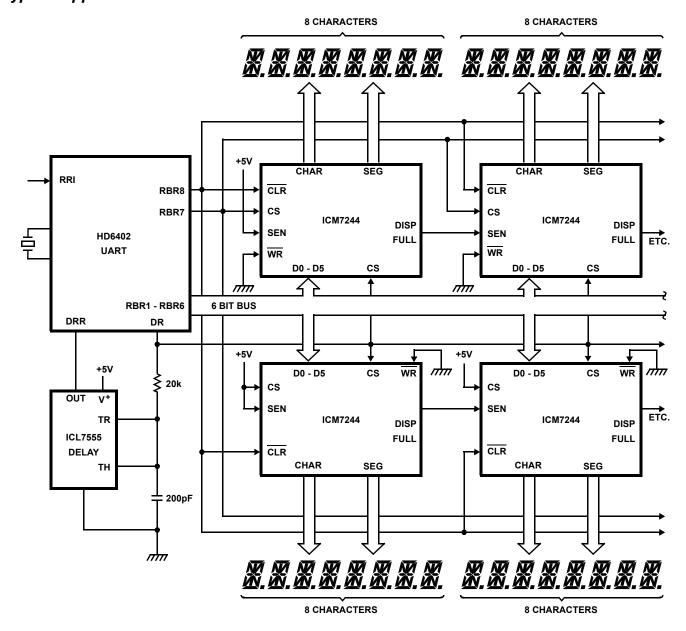

FIGURE 5. DRIVING TWO ROWS OF CHARACTERS FROM A SERIAL INPUT

# Typical Applications (Continued)

NOTE: 17 for ICM7244.

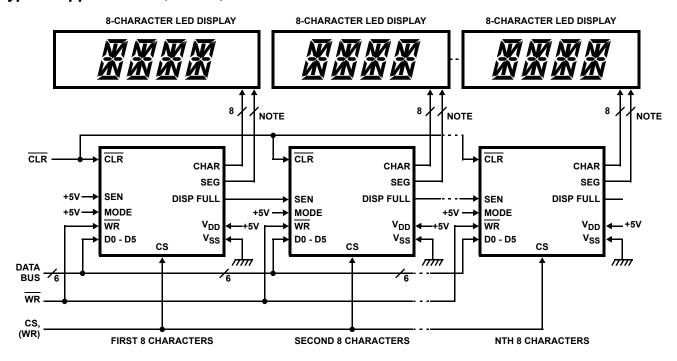

FIGURE 6. MULTICHARACTER DISPLAY USING SEQUENTIAL ACCESS MODE

FIGURE 7A. COMMON CATHODE DISPLAY

FIGURE 7B. COMMON ANODE DISPLAY

FIGURE 7. DRIVING LARGE DISPLAYS

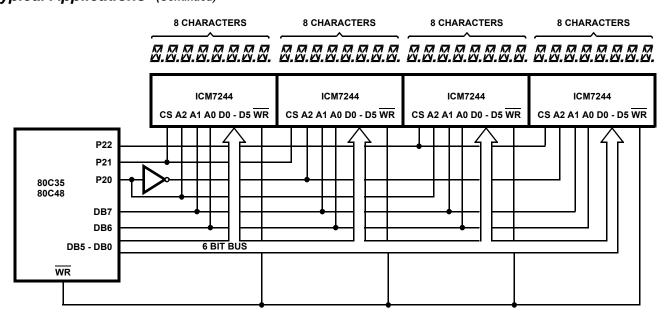

# Typical Applications (Continued)

FIGURE 8. RANDOM ACCESS 32-CHARACTER DISPLAY IN A 80C48 SYSTEM

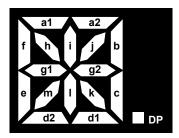

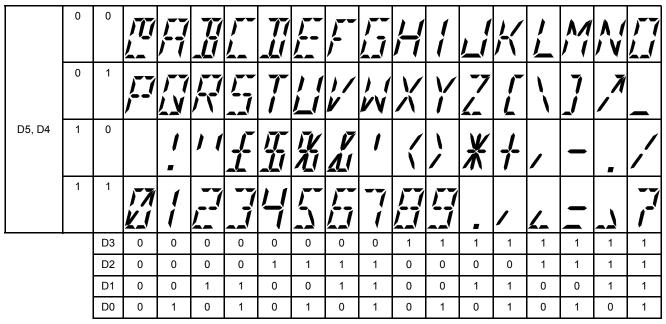

# Display Font and Segment Assignments

FIGURE 9. 16-SEGMENT CHARACTER FONT WITH DECIMAL POINT

## Display Font and Segment Assignments (Continued)

FIGURE 10. SEGMENT AND CHARACTER DRIVERS OUTPUT CIRCUIT

## **Detailed Description**

## WR, CS

These pins are immediately functionally ANDed, so all actions described as occurring on an edge of  $\overline{WR}$ , with CS enabled, will occur on the equivalent (last) enabling or (first) disabling edge of any of these inputs. The delays from CS pins are slightly (about 5ns) greater than from  $\overline{WR}$  due to the additional inverter required on the former.

#### **MODE**

The MODE pin input is latched on the falling edge of  $\overline{\text{WR}}$  (or its equivalent, see  $\overline{\text{WR}}$  description). The location (in Data Memory) where incoming data will be placed is determined either from the Address pins or the Sequential Address Counter. This is controlled by MODE input. MODE also controls the function of A0/SEN, A1/ $\overline{\text{CLR}}$ , and A2/DISPlay FULL lines.

#### Random Access Mode

When the internal mode latch is set for **Random Access (RA)** (MODE latched low), the Address input on A0, A1 and A2 will be latched by the falling edge of  $\overline{WR}$  (or its equivalent). Subsequent changes on the Address lines will not affect device operation. This allows use of a multiplexed 6-bit bus controlling both address and data, with timing controlled by  $\overline{WR}$ .

### Sequential Access Mode

If the internal latch is set for **Sequential Access (SA)**, (MODE latched high), the Serial ENable input or SEN will be latched on the falling edge of  $\overline{WR}$  (or its equivalent). The  $\overline{CLR}$  input is asynchronous, and will force-clear the Sequential Address Counter to address 000 (CHARacter 1), and set all Data Memory contents to 100000 (blank) at any time. The DISPlay FULL output will be active in **SA** mode to indicate the overflow status of the Sequential Address Counter. If this

output is low, and SEN is (latched) high, the contents of the Counter will be used to establish the Data Memory location for the Data input. The Counter is then incremented on the rising edge of  $\overline{\text{WR}}$ . If SEN is low, or DISPlay FULL is high, no action will occur. This allows easy "daisy-chaining" of display drivers for multiple character displays in a **Sequential Access** mode.

## **Changing Modes**

Care must be exercised in any application involving changing from one mode to another. The change will occur only on a falling edge of WR (or its equivalent). When changing mode from **Sequential Access** to **Random Access**, note that A2/DISPlay FULL will be an output until WR has fallen low, and an Address drive here could cause a conflict. When changing from **Random Access** to **Sequential Access**, A1/CLR should be high to avoid inadvertent clearing of the Data Memory and Sequential Address Counter. DISPlay FULL will become active immediately after the rising edge of WR.

### Data Entry

The input Data is latched on the rising edge of WR (or its equivalent) and then stored in the Data Memory location determined as described above. The six Data bits can be multiplexed with the Address information on the same lines in **Random Access** mode. Timing is controlled by the WR input.

#### OSC/OFF

The device includes a relaxation oscillator with an internal capacitor and a nominal frequency of 200kHz. By adding external capacitance to  $V_{DD}$  at the OSC/ $\overline{\text{OFF}}$  pin, this frequency can be reduced as far as desired. Alternatively, an external signal can be injected on this pin. The oscillator (or external) frequency is pre-divided by 64, and then further divided by 8 in the Multiplex Counter, to drive the CHARacter drive lines ( Figure 3). An inter-character blanking signal is

derived from the pre-divider. An additional comparator on the OSC/OFF input detects a level lower than the relaxation oscillator's range, and blanks the display, disables the DISPlay FULL output (if active), and clears the pre-divider and Multiplex Counter. This puts the circuit in a low-power-dissipation mode in which all outputs are effectively open circuits, except for parasitic diodes to the supply lines. Thus a display connected to the output may be driven by another circuit (including another ICM7244) without driver conflicts.

## Display Output

The output of the Multiplex Counter is decoded and multiplexed into the address input of the Data Memory, except during  $\overline{WR}$  operations (in Sequential Access mode, with SEN high and DISPlay FULL low), when it scans through the display data. The address decoder also drives the CHARacter outputs, except during the inter-character

blanking interval (nominally about 5µs). Each CHARacter output lasts nominally about 300µs, and is repeated nominally every 2.5ms, i.e., at a 400Hz rate (times are based on internal oscillator without external capacitor).

The 6 bits read from the Data Memory are decoded in the ROM to the 17 segment signals, which drive the SEGment outputs. Both CHARacter and SEGment outputs are disabled during WR operations (with SEN high and DISPlay FULL Low for **Sequential Access** mode). The outputs may also be disabled by pulling OSC/OFF low.

The decode pattern from 6 bits to 17 segments is done by a ROM pattern according to the ASCII font shown. Custom decode patterns can be arranged, within these limitations, by consultation with the factory.

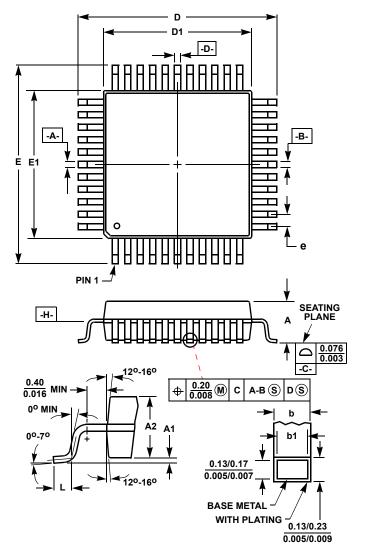

# Metric Plastic Quad Flatpack Packages (MQFP)

Q44.10x10 (JEDEC MS-022AB ISSUE B)

44 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

|        | INCHES    |       | MILLIN |       |       |

|--------|-----------|-------|--------|-------|-------|

| SYMBOL | MIN       | MAX   | MIN    | MAX   | NOTES |

| Α      | -         | 0.096 | -      | 2.45  | -     |

| A1     | 0.004     | 0.010 | 0.10   | 0.25  | -     |

| A2     | 0.077     | 0.083 | 1.95   | 2.10  | -     |

| b      | 0.012     | 0.018 | 0.30   | 0.45  | 6     |

| b1     | 0.012     | 0.016 | 0.30   | 0.40  | -     |

| D      | 0.515     | 0.524 | 13.08  | 13.32 | 3     |

| D1     | 0.389     | 0.399 | 9.88   | 10.12 | 4, 5  |

| E      | 0.516     | 0.523 | 13.10  | 13.30 | 3     |

| E1     | 0.390     | 0.398 | 9.90   | 10.10 | 4, 5  |

| L      | 0.029     | 0.040 | 0.73   | 1.03  | -     |

| N      | 44        |       | 44     |       | 7     |

| е      | 0.032 BSC |       | 0.80   | BSC   | -     |

Rev. 2 4/99

#### NOTES:

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 2. All dimensions and tolerances per ANSI Y14.5M-1982.

- 3. Dimensions D and E to be determined at seating plane -C-

- 4. Dimensions D1 and E1 to be determined at datum plane -H-.

- Dimensions D1 and E1 do not include mold protrusion.

Allowable protrusion is 0.25mm (0.010 inch) per side.

- Dimension b does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total.

- 7. "N" is the number of terminal positions.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system, Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### SALES OFFICES

## Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited Dukes Meadow, Milliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0898, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd.

80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia

Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangiae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338