### NOT RECOMMENDED FOR NEW DESIGN NO ALTERNATE PART

NIS5135

#### 3.6A 5V RESETTABLE ELECTRONIC FUSE

# **Description**

The NIS5135 is a self-protected resettable electronic fuse designed for consumer applications such as hard disk drives to industrial applications to enhance system reliability against catastrophic and shutdown failures.

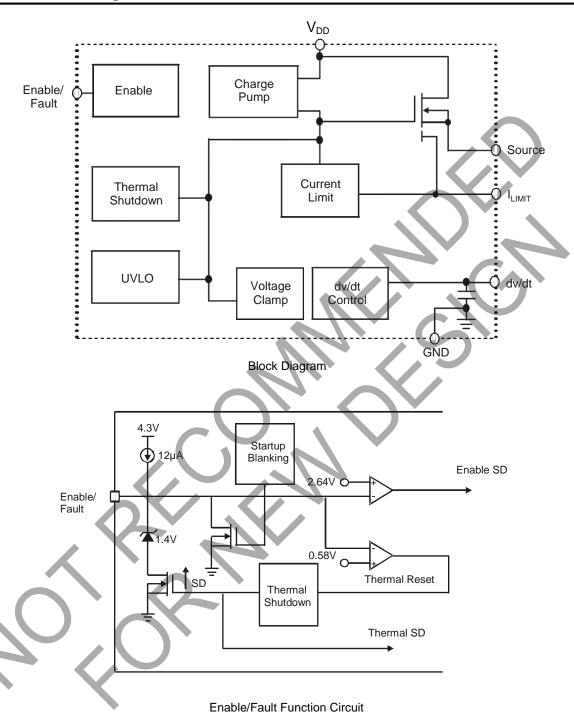

To support a wide range of demanding applications, the design has been optimized to operate over the supply range of 3.1V to 18V. For robustness and protection, the device integrates a low  $R_{\rm DS(ON)}\,{\rm NMOS}$  buffer power device along with an undervoltage lockout, overvoltage clamp, a current limit, a dv/dt control and a thermal shutdown circuit. The overvoltage circuit limits the output voltage without shutting the device down to allow the load to continue operating during overvoltage. Thermal shutdown can be either latching type (NIS5135MN1) or auto-retry type (NIS5135MN2).

### **Features**

- 3.1V to 18V Operating Input Voltage

- Integrated NMOS Power Device with R<sub>DS(ON)</sub> of 30mΩ Typical

- Internal Current Limit No External Current Sense Resistor in Load Path

- Undervoltage Lockout

- Over Voltage Clamp (NIS5135MN1 and NIS5135MN2)

- Thermal Shutdown

- -40°C to +150°C Operating Junction Temperature

- ESD Ratings: HBM > 1500V; MM 200V

- Small Low Profile U-DFN3030-10 package

- Totally Lead Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

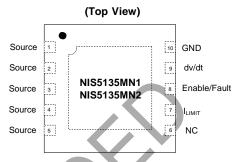

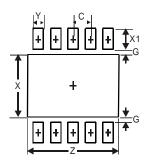

# **Pin Assignments**

U-DFN3030-10

## **Applications**

- Hard Disk Drives

- Solid State Drives (SSD)

- Set-top Boxes

- DVDs and Blu-ray Disc Drivers

- Mother Board Power Management

- Printer Load Power Management

- Fan Drives

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

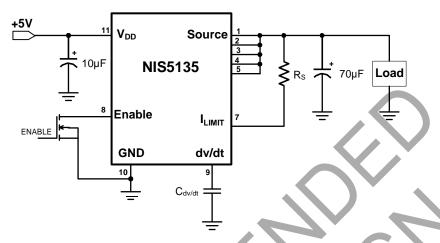

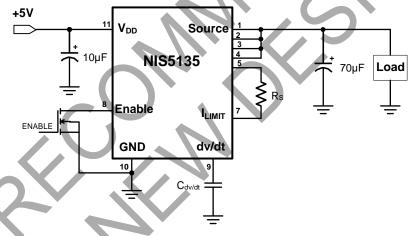

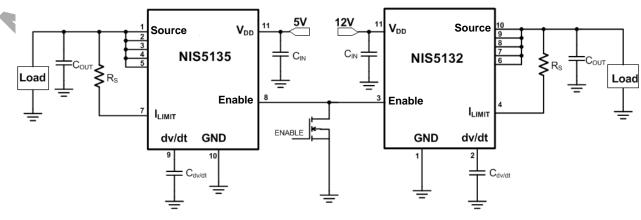

# **Typical Application Circuits**

Figure 1. Application Circuit with Direct Current Sensing

Figure 2. Application Circuit with Kelvin Current Sensing

Figure 3. Application Circuit with Common Thermal Shutdown

# **Pin Descriptions**

| Pin Number  | Pin Name           | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 5      | Source             | The internal NMOS power device's Source pins: These pins are the Source of internal power device and also the output terminal of the electronic fuse.                                                                                                                                                                                                                                                      |

| 6           | NC                 | No internal connection to device Internal NMOS power device turn-on time adjustment pin:  If this pin is left unconnected, the internal capacitor ensures the turn-on ramp is over a period of 2ms typical. If an additional delay is required, connect a capacitor from this pin to the ground.                                                                                                           |

| 7           | I <sub>LIMIT</sub> | Current limit setting pin: A resistor between Source pins and this pin sets the overload and short-circuit current limit thresholds.                                                                                                                                                                                                                                                                       |

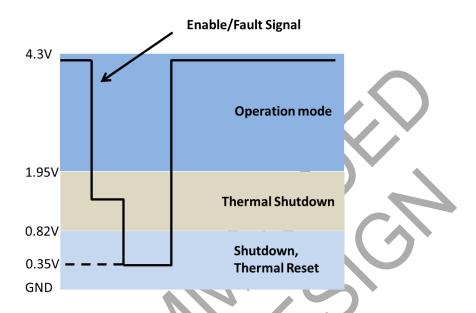

| 8           | Enable/Fault       | Tri-state bi-directional interface pin:  The output can be disabled by pulling this pin to ground through an open drain or an open collector. Additionally, this pin output goes to an intermediate state to indicate that the device is in thermal shutdown state. This pin can also be connected together with other NIS5135 devices to cause a system-wide simultaneous shutdown during thermal events. |

| 9           | dv/dt              | Internal NMOS power device turn-on time adjustment pin:  If this pin is is left unconnected, the internal capacitor ensures the turn-on ramp is over a period of 2ms typical. If an additional delay is required, connect a capacitor from this pin to the ground.                                                                                                                                         |

| 10          | GND                | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                 |

| Exposed PAD | $V_{DD}$           | Positive input voltage to the device                                                                                                                                                                                                                                                                                                                                                                       |

NIS5135

# **Functional Block Diagram**

### NOT RECOMMENDED FOR NEW DESIGN **NO ALTERNATE PART**

**NIS5135**

### **Absolute Maximum Ratings** (Note 4) (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol            | Characteristic                                              | Value                        | Unit        |   |

|-------------------|-------------------------------------------------------------|------------------------------|-------------|---|

| \/                | Input Voltage in Steady State Operating Conditions (Note 5) |                              | -0.6 to +18 | V |

| $V_{DD}$          | Input Voltage - Transient (100ms)                           |                              | -0.6 to +25 | V |

| 0                 | Junction to Air Thermal Resistance                          | 0.1 in <sup>2</sup> (Note 6) | 227         |   |

| $\Theta$ JA       | Junction to All Thermal Resistance                          | 0.5 in <sup>2</sup> (Note 6) | 95          |   |

| θJL               | Junction to Lead Thermal Resistance                         | 27                           | °C/W        |   |

| θЈС               | Junction to Case Thermal Resistance                         | 20                           |             |   |

| P <sub>DMAX</sub> | Package Power Dissipation at T <sub>A</sub> = +25°C         | 1.3                          | W           |   |

| _                 | Thermal Derating Above +25°C                                | 10.4                         | mW/°C       |   |

| T <sub>S</sub>    | Storage Temperature Range                                   | -55 to +155                  | °C          |   |

| TJ                | Operating Junction Temperature (Note 7)                     | -40 to +150                  | °C          |   |

| TL                | Lead Temperature During Soldering (10s)                     | +260                         | °C          |   |

Notes:

- 4. Stresses greater than the 'Absolute Maximum Ratings' specified above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may be affected by exposure to absolute maximum rating conditions for extended periods of time.

5. Negative voltage will not damage the device provided that the power dissipation is within the package dissipation rating.

- 6. 1 oz copper on double sided FR-4 PCB.

- 7. Thermal limit is set above the maximum thermal rating. It is not recommended to operate the device at temperature above the maximum rating for extended period.

# **Recommended Operating Conditions**

| Symbol   | Characteristic                      | Tes | st Condition | Rating      | Unit |

|----------|-------------------------------------|-----|--------------|-------------|------|

| $V_{DD}$ | Supply Voltage                      |     | Operating    | 3.1 to 18.0 | V    |

| TJ       | Operating Juntion Temperature Range |     | Operating    | -40 to +150 | °C   |

### NOT RECOMMENDED FOR NEW DESIGN **NO ALTERNATE PART**

NIS5135

# $\textbf{Electrical Characteristics} \ (V_{DD} = 5V, \ C_L = 70 \mu F, \ \text{dv/dt pin open}, \ R_{LIMIT} = 10 \Omega, \ \text{and} \ T_A = +25 ^{\circ}C, \ \text{unless otherwise noted.})$

| Symbol                  | Characteristic                                                                                         | Test Condition                                                        | Min                 | Тур  | Max      | Unit  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------|------|----------|-------|--|

| Device                  |                                                                                                        |                                                                       |                     |      |          |       |  |

| I <sub>BIAS</sub>       | Bias Current                                                                                           | Device Operational                                                    | _                   | 0.8  | 1.5      | mA    |  |

| I <sub>BIAS_SD</sub>    | Bias Current during Shutdown                                                                           | Device Shutdown                                                       | _                   | 0.4  | _        | mA    |  |

| V <sub>DD_MIN</sub>     | Minimum Operating Voltage Once<br>Successfully Started Up                                              | _                                                                     | _                   | _    | 3.1      | V     |  |

| NMOS Powe               | r Device                                                                                               |                                                                       |                     |      |          |       |  |

| t <sub>DLY</sub>        | Chip Enable Dealy Time                                                                                 | Enabling of the IC to I <sub>D</sub> = 100mA (with 1A resistive load) | _                   | 220  | _        | μs    |  |

| В                       | NMOS Drain to Source Kelvin ON                                                                         | NMOS fully on                                                         | 20                  | 30   | 40       | m0    |  |

| R <sub>DS(ON)</sub>     | Resistance (Note 8)                                                                                    | NMOS fully on, T <sub>J</sub> = +140°C                                | _                   | 45   | _        | - mΩ  |  |

| V <sub>OUT_OFF</sub>    | Off State Output Voltage                                                                               | $V_{DD} = 10V, V_{GS} = 0V, R_{L} = \infty$                           | _                   | 0.05 | 0.2      | V     |  |

|                         | Continue Comment (Net e 2)                                                                             | $T_A = +25^{\circ}C$ , 0.5 in. <sup>2</sup> pad                       | <b>\</b> - <i>\</i> | 3.6  | _        | Δ.    |  |

| I <sub>D</sub>          | Continuous Current (Note 9)                                                                            | T <sub>A</sub> = +80°C, min copper                                    |                     | 1.7  | A        |       |  |

| _                       | Output Capacitance                                                                                     | $V_{DS} = 12V, V_{GS} = 0V, f = 1MHz$                                 |                     | 230  |          | pF    |  |

| dv/dt Ramp              |                                                                                                        |                                                                       |                     |      |          |       |  |

| tslew                   | Output Voltage Ramp Time                                                                               | Device enable to V <sub>DS</sub> = 11.7V                              | 0.7                 | 1.4  | 2.4      | ms    |  |

| V <sub>C_MAX</sub>      | Maximum Capacitor Voltage                                                                              | -                                                                     |                     | _    | $V_{DD}$ | V     |  |

| Under/Overv             | voltage Protection                                                                                     |                                                                       |                     |      |          |       |  |

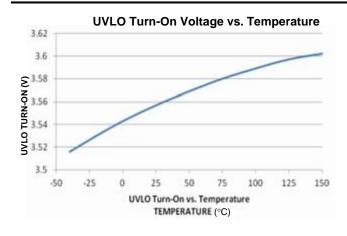

| V <sub>UVLO</sub>       | Undervoltage Lockout Threshold                                                                         | Turn on, Voltage rising                                               | 3.2                 | 3.6  | 4.0      | V     |  |

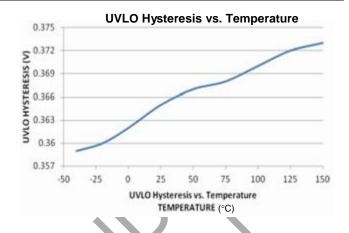

| V <sub>U</sub> VLO_HYST | Undervoltage Lockout Hysteresis                                                                        | - 101                                                                 | -                   | 0.40 |          | V     |  |

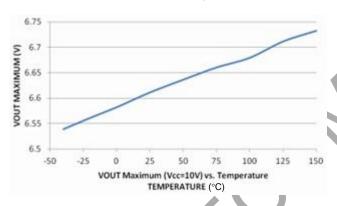

| V <sub>CLAMP</sub>      | Overvoltage Clamp Limit (Note 10)                                                                      | During over voltage protection,<br>V <sub>DD</sub> = 18V              | 5.95                | 6.65 | 7.35     | V     |  |

| Current Limi            | t                                                                                                      |                                                                       |                     |      |          |       |  |

| ILIMIT_SS               | Kelvin Short Circuit Current Limit (Note 11)                                                           | R <sub>LIMIT</sub> = 11Ω                                              | 2.3                 | 3.1  | 4.4      | А     |  |

| I <sub>LIMIT_OL</sub>   | Kelvin Over Load Current Limit<br>(Note 11)                                                            | $R_{\text{LIMIT}} = 11\Omega$                                         | _                   | 3.5  | _        | А     |  |

| Thermal Pro             | tection                                                                                                |                                                                       |                     |      |          |       |  |

| T <sub>SD</sub>         | Thermal Shutdown Junction Temperature Threshold (Note 9)                                               | Temperature rising                                                    | +150                | +175 | +200     | °C    |  |

| T <sub>SD_HYST</sub>    | Thermal Shutdown Hysteresis in Non<br>Latching Devices                                                 |                                                                       | -                   | +45  | _        | °C    |  |

| Enable/Fault            |                                                                                                        |                                                                       |                     |      |          |       |  |

| $V_{EN\_LOW}$           | Enable Logic Level Low Voltage                                                                         | Output disabled                                                       | 0.35                | 0.58 | 0.81     | V     |  |

| V <sub>EN_MID</sub>     | Enable Logic Level Mid Voltage                                                                         | Output disabled, Thermal fault                                        | 0.82                | 1.4  | 1.95     | V     |  |

| V <sub>EN_HI</sub>      | Enable Logic Level High                                                                                | Output enabled                                                        | 1.96                | 2.64 | 3.3      | V     |  |

| V <sub>EN_MAX</sub>     | High State Maximum Voltage                                                                             | _                                                                     | 3.4                 | 4.3  | 5.3      | V     |  |

| I <sub>EN_SINK</sub>    | Logic Low Sink Current                                                                                 | V <sub>ENABLE</sub> = 0V                                              | _                   | -12  | -20      | μΑ    |  |

| I <sub>EN_LKG</sub>     | Logic High Leakage Current for External Switch                                                         | V <sub>ENABLE</sub> = 3.3V                                            | _                   | _    | 1.0      | μΑ    |  |

| Fanout                  | Maximum Fanout – Number of device that can be connected together to this pin for simultaneous shutdown | _                                                                     | _                   | _    | 3.0      | Units |  |

| Notes 8                 | Pulse test with pulse width of 300us, duty cycle 2                                                     | i e e e e e e e e e e e e e e e e e e e                               |                     |      |          |       |  |

Notes:

<sup>8.</sup> Pulse test with pulse width of 300µs, duty cycle 2%.

9. This parameter is not tested in production. It is guaranteed by design, process control and characterization.

10. Overvoltage clamp feature is available on in NIS5135MN1 and NIS5135MN2 versions.

11. Refer to application note on explanation on short circuit and overload conditions.

# **Performance Characteristics**

### **Output Clamp Voltage vs. Temperature**

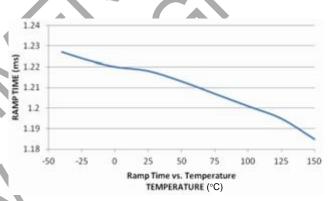

Output Voltage dv/dt Ramp Time vs. Temperature

# **Input Transient Response**

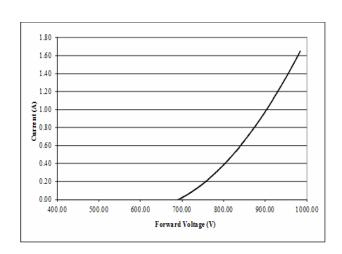

### **Body Diodes Forward Characteristics**

## **Performance Characteristics** (Cont.)

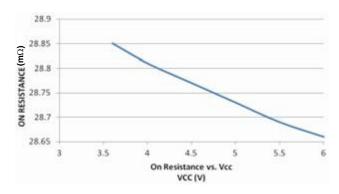

# Power Device ON Resistance (R<sub>DS(ON)</sub>) vs. V<sub>CC</sub>

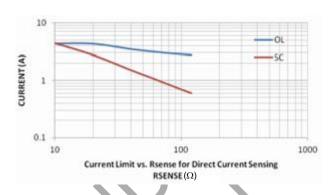

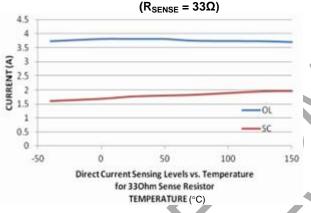

### Current Limit vs. R<sub>SENSE</sub> for Direct Current Sensing

**Direct Current Sensing Level vs. Temperature**

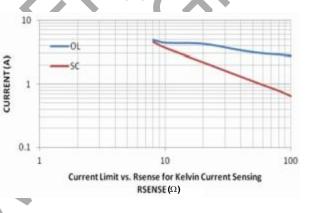

Current Limit vs. R<sub>SENSE</sub> for Kelvin Current Sensing

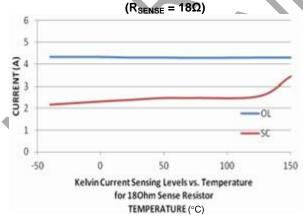

Kelvin Current Sensing Levels vs. Temperature

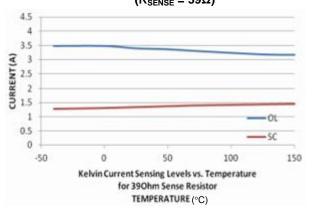

# Kelvin Current Sensing Levels vs. Temperature $(R_{SENSE} = 39\Omega)$

# NOT RECOMMENDED FOR NEW DESIGN NO ALTERNATE PART

NIS5135

# **Application Note**

### **Theory of Operation**

The NIS5135 is a self-protected, resettable electronic fuse. It monitors the input and output voltage, the output current and the die temperature. When the NIS5135 is powered up it will ramp up the output voltage based on the dv/dt setting (see description below) and current will begin to flow. The device current limit can be set with an external resistor, the ramp rate (dv/dt) can be adjusted with an external capacitor. The Overvoltage Clamp, Undervoltage Lockout and Thermal Protection are internally set.

#### **Power Supply Considerations**

Placing a high-value electrolytic capacitor or X7R (X5R) ceramic capacitor between  $V_{DD}$  to GND (10 $\mu$ F) and Source to GND (70 $\mu$ F) as close to the device as possible is highly recommended. This precaution reduces power-supply transients that may cause ringing on the input and load transients that may cause output voltage falls below input voltage resulting device over-heat.

#### **Current Limit**

The NIS5135 incorporates a sensefet with a reference and amplifier to control the current in the device. The sensefet uses a small fraction of the load current to measure the actual current. This reduces the losses as a smaller sense resistor can be used. The current can be measured directly with the R<sub>s</sub> resistor connected between the load and the I<sub>LIMIT</sub> pin (see Figure 1). That method includes the resistance of the bond wires in the current limiting circuit. A Kelvin connection (see Figure 2) can be used also; in that case one of the 5 source pins will be used and the voltage is measured on the die, eliminating the bond wire resistance. That reduces the Source pins to the load to four and therefore increases the on-resistance of the effuse to the load.

#### Overvoltage Clamp

The NIS5135MN1 and NIS5135MN2 monitor the input voltage and clamp it once it exceeds 6.65V. This will allow for transient on the input for short periods of time. If the input voltage stays above 6.65V for extended time the voltage drop across the FET with the load current will increase the die temperature and the thermal shutdown feature will protect the device and shut it down.

#### **Undervoltage Lock Out**

The input voltage of the NIS5135 is monitored by an UVLO circuit (undervoltage lockout) if the input voltage drops below this threshold the output transistor will be pulled into a high impedance state.

#### dv/dt

The NIS5135 has an integrated control circuit that forces a linear ramp on the output voltage raise regardless of the load impedance. Without connecting a capacitor on the dv/dt pin the ramp time is roughly 2ms. Adding an external capacitor can increase this ramp rate. The internal current source of 90µA will charge the external capacitor at a slow rate. It is recommended to utilize a ceramic capacitor.

The ramp time can be determined with the following equation:

$$t_{ramp} = 30e^6(50pF + C_{ext})$$

$$C_{ext} = \frac{t_{ramp}}{30e^6} - 50pF$$

C<sub>ext</sub> in Farad t<sub>ramp</sub> in seconds

The ramp-up circuit is discharged and V<sub>OUT</sub> starts from 0V when the units shut down after a fault, enable shutdown or input power cycle.

#### Enable/Fault

The NIS5135 has a tri state Enable/Fault pin. It is used to turn on and off the device with high and low signals from a GPIO, but can also indicate a thermal fault. When the Enable/Fault pin is pulled low, the output is turned off. When the Enable/Fault pin is pulled high, the output is turned on. In the event of a thermal fault, the Enable/Fault pin will be pulled low to an intermediate voltage by an internal circuit. This can be used to chain up to 4 NIS5135 together that during a thermal shut down the linked devices turn off as well.

Due to this fault indication capability, it should not be connected to any type of logic with an internal pull up device.

The NIS5135MN1 connected to a 2<sup>nd</sup> device will latch off until the Enable/Fault pin has been pulled to low and then allowed to go back up to a high signal, or if the power has been cycled. Once the part starts up again it will go through the start up ramp determined by the internal circuit or based on the externally connected capacitor on pin dv/dt.

The MN2 devices will auto restart once the part that indicated a thermal shutdown has cooled down. It will also go through the start up ramp.

## **Application Note** (Cont.)

Enable/Fault (Cont.)

Figure 4. Enable/Fault Signal Levels

### **Thermal Protection**

The NIS5135 has an integrated temperature sensing circuit that protects the die in the event of over temperature. The trip point has been intentionally set high at +175°C to allow for increased trip times during high power transient events. The NIS5135 will shut down current flow to the output when the die temperature reaches +175°C. The NIS5135MN1 will restart after the Enable pin has been toggled or the input power has been cycled. The NIS5135MN2 will auto restart after the die temperature has been reduced by -45°C.

Even though the thermal trip point has been set high to allow for high current transients the circuit design should accomplish best thermal performance with good thermal layout of the PCB. It is not recommended to operate NIS5135 above +150°C over extended periods of time.

NIS5135 10 of 13 May 2017

Document number: DS37968 Rev. 4 - 3 www.diodes.com © Diodes Incorporated

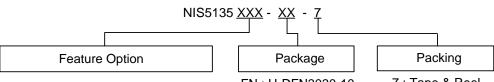

# **Ordering Information**

MN1: Thermal Latching with V<sub>CLAMP</sub> MN2: Thermal Auto-retry with V<sub>CLAMP</sub>

7: Tape & Reel FN: U-DFN3030-10

| David Massala as | Bashana Oada |              | 7" Tape and Reel  |                    |  |

|------------------|--------------|--------------|-------------------|--------------------|--|

| Part Number      | Package Code | Packaging    | Quantity          | Part Number Suffix |  |

| NIS5135MN1-FN-7  | FN           | U-DFN3030-10 | 3,000/Tape & Reel | -7                 |  |

| NIS5135MN2-FN-7  | FN           | U-DFN3030-10 | 3,000/Tape & Reel | -7                 |  |

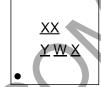

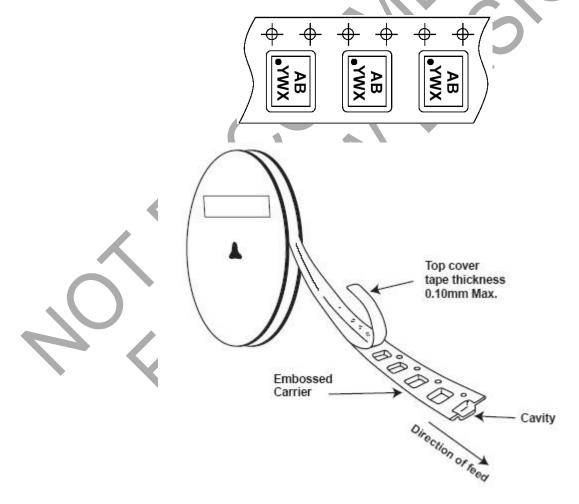

# **Marking Information**

(1) Package Type: U-DFN3030-10

### (Top View)

XX: Identification Code

Y: Year: 0~9

W: Week: A~Z: 1~26 week;

a~z: 27~52 week; z represents

52 and 52 week

X: A~Z: Internal Code

| Part Number     | Package      | Identification Code |

|-----------------|--------------|---------------------|

| NIS5135MN1-FN-7 | U-DFN3030-10 | M5                  |

| NIS5135MN2-FN-7 | U-DFN3030-10 | N5                  |

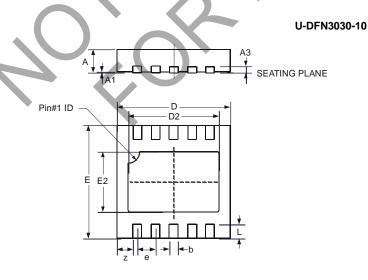

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

| U-DFN3030-10         |      |      |       |  |

|----------------------|------|------|-------|--|

| Dim                  | Min  | Max  | Тур   |  |

| Α                    | 0.57 | 0.63 | 0.60  |  |

| A1                   | 0    | 0.05 | 0.02  |  |

| A3                   | -    | -    | 0.15  |  |

| b                    | 0.20 | 0.30 | 0.25  |  |

| D                    | 2.90 | 3.10 | 3.00  |  |

| D2                   | 2.30 | 2.50 | 2.40  |  |

| е                    | 1    | -    | 0.50  |  |

| E                    | 2.90 | 3.10 | 3.00  |  |

| E2                   | 1.50 | 1.70 | 1.60  |  |

| L                    | 0.25 | 0.55 | 0.40  |  |

| Z                    | -    | -    | 0.375 |  |

| All Dimensions in mm |      |      |       |  |

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### U-DFN3030-10

| <b>Dimensions</b> | Value (in mm) |

|-------------------|---------------|

| Z                 | 2.60          |

| G                 | 0.15          |

| X                 | 1.80          |

| X1                | 0.60          |

| Y                 | 0.30          |

| С                 | 0.50          |

# **Taping Orientation**

(1) Package Type: U-DFN3030-10

$Note: \quad 12. \ The \ taping \ or ientation \ of \ the \ other \ package \ type \ can \ be \ found \ on \ our \ website \ at \ http://www.diodes.com/datasheets/ap02007.pdf.$

# NOT RECOMMENDED FOR NEW DESIGN NO ALTERNATE PART

NIS5135

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2017, Diodes Incorporated

www.diodes.com