# ACS8522 SETS LITE

Synchronous Equipment Timing Source for Stratum 3/4E/4 and SMC Systems

### **ADVANCED COMMUNICATIONS**

### **FINAL**

**DATASHEET**

### Description

The ACS8522 is a highly integrated, single-chip solution for the Synchronous Equipment Timing Source (SETS) function in a SONET or SDH Network Element. The device generates SONET or SDH Equipment Clocks (SEC) and Frame Synchronization clocks. The ACS8522 is fully compliant with the required international specifications and standards.

The device supports Free-run, Locked and Holdover modes, with mode selection controlled either automatically by an internal state machine or forced by register configuration.

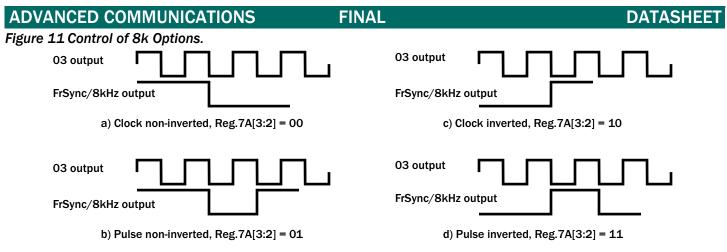

The ACS8522 accepts up to four independent input SEC reference clock sources from Recovered Line Clock, PDH network, and Node Synchronization. The ACS8522 generates independent SEC and BITS clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock, both with programmable pulse width and polarity.

The ACS8522 includes a Serial Port, which can be SPI compatible, providing access to the configuration and status registers for device setup.

The ACS8522 supports IEEE 1149.1<sup>[5]</sup> JTAG boundary scan.

The User can choose between OCXO or TCXO to define the Stratum and/or Holdover performance required.

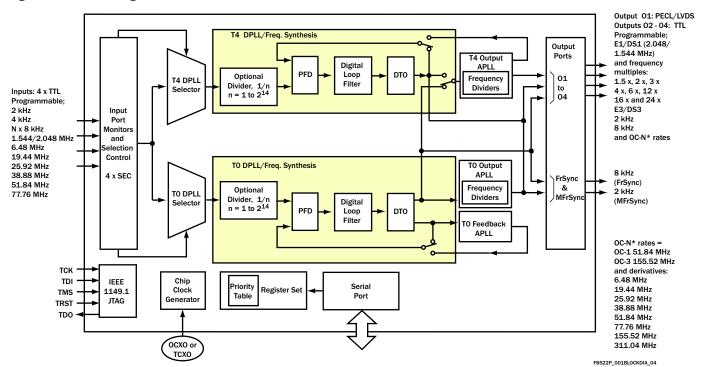

# Block Diagram

Figure 1 Block Diagram of the ACS8522 SETS LITE

# Features

- ◆ Suitable for Stratum 3, 4E, 4 and SONET Minimum Clock (SMC) or SONET/SDH Equipment Clock (SEC) applications (to Telcordia 1244-CORE<sup>[19]</sup> Stratum 3 and GR-253<sup>[17]</sup>, and ITU-T G.813<sup>[11]</sup> Options I and II specifications)

- Accepts four individual input reference clocks, all with robust input clock source quality monitoring

- Simultaneously generates four output clocks, plus two Sync pulse outputs

- ◆ Absolute Holdover accuracy better than 3 x 10<sup>-10</sup> (manual), 7.5 x 10<sup>-14</sup> (instantaneous); Holdover stability defined by choice of external XO

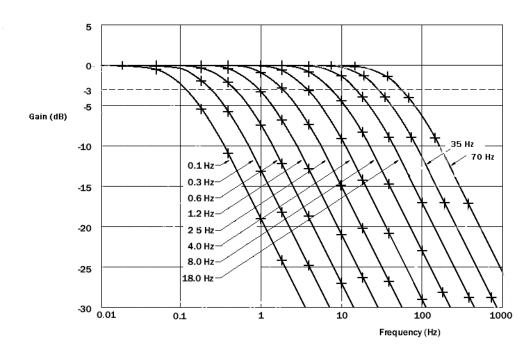

- Programmable PLL bandwidth, for wander and jitter tracking/attenuation, 0.1 Hz to 70 Hz in 10 steps

- Automatic hit-less source switchover on loss of input

- Serial SPI compatible interface

- ◆ Output phase adjustment in 6 ps steps up to ±200 ns

- ◆ IEEE 1149.1<sup>[5]</sup> JTAG Boundary Scan

- Available in LQFP 64-pin package

- Single 3.3 V operation. 5 V tolerant

- Lead (Pb)-free version available (ACS8522T), RoHS and WEEE compliant.

# **FINAL**

# DATASHEET

# Table of Contents

| Section                                                    | Page |

|------------------------------------------------------------|------|

| Description                                                |      |

| Block Diagram                                              |      |

| Features                                                   | 1    |

| Table of Contents                                          | 2    |

| Pin Diagram                                                | 4    |

| Pin Description                                            | 5    |

| Introduction                                               |      |

| General Description                                        |      |

| Overview                                                   | 7    |

| Input Reference Clock Ports                                | 9    |

| Locking Frequency Modes                                    | 9    |

| Clock Quality Monitoring                                   | 10   |

| Activity Monitoring                                        | 11   |

| Frequency Monitoring                                       | 12   |

| Selection of Input Reference Clock Source                  | 12   |

| Forced Control Selection                                   | 13   |

| Automatic Control Selection                                | 13   |

| Ultra Fast Switching                                       | 13   |

| Fast External Switching Mode-SRCSW pin                     | 13   |

| Output Clock Phase Continuity on Source Switchover         | 14   |

| Modes of Operation                                         | 14   |

| Free-run Mode                                              | 14   |

| Pre-locked Mode                                            | 14   |

| Locked Mode                                                | 14   |

| Lost-phase Mode                                            | 14   |

| Holdover Mode                                              | 15   |

| Pre-locked2 Mode                                           | 17   |

| DPLL Architecture and Configuration                        | 17   |

| TO DPLL Main Features                                      | 18   |

| T4 DPLL Main Features                                      |      |

| TO DPLL Automatic Bandwidth Controls                       | 18   |

| Phase Detectors                                            |      |

| Phase Lock/Loss Detection                                  |      |

| Damping Factor Programmability                             |      |

| Local Oscillator Clock                                     |      |

| Output Wander                                              |      |

| Jitter and Wander Transfer                                 |      |

| Phase Build-out                                            |      |

| Input-to-Output Phase Adjustment                           |      |

| Input Wander and Jitter Tolerance                          |      |

| Using the DPLLs for Accurate Frequency and Phase Reporting |      |

| MFrSync and FrSync Alignment-SYNC2K                        |      |

| Output Clock Ports                                         |      |

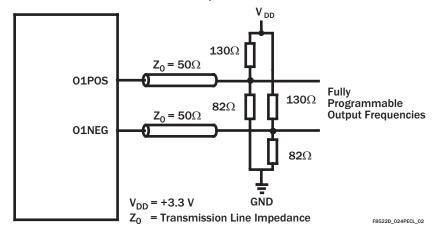

| PECL/LVDS Output Port Selection                            |      |

| Output Frequency Selection and Configuration               |      |

| Power-On Reset                                             |      |

| Serial Interface                                           | 38   |

| ADVANCED COMMUNICATIONS    | FINAL | DATASHEET |

|----------------------------|-------|-----------|

| Section                    |       | Page      |

| Register Map               |       | 41        |

| Register Organization      |       |           |

| Register Access            |       |           |

| Interrupt Enable and Clear |       |           |

| Defaults                   |       |           |

| Register Descriptions      |       |           |

| Electrical Specifications  |       |           |

| JTAG                       |       |           |

| Over-voltage Protection    |       |           |

| ESD Protection             |       |           |

| Latchup Protection         |       |           |

| Maximum Ratings            |       |           |

| Operating Conditions       |       |           |

| DC Characteristics         |       |           |

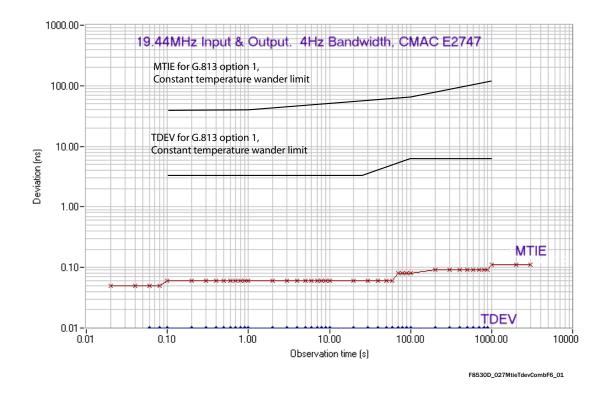

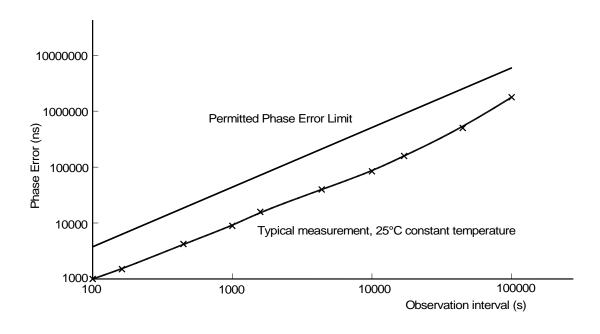

| Jitter Performance         |       |           |

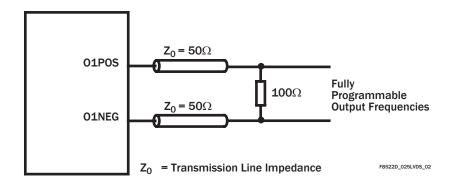

| Input/Output Timing        |       |           |

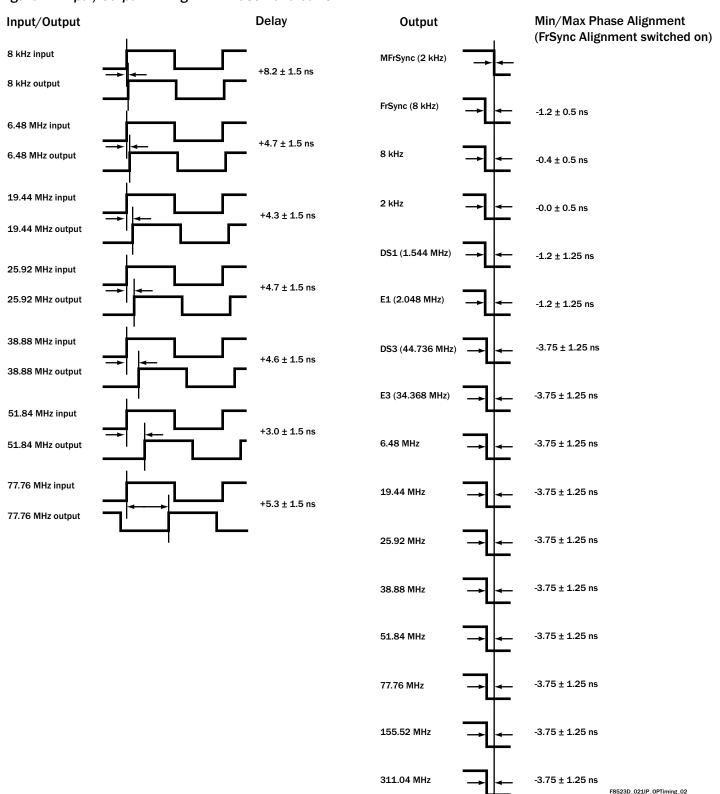

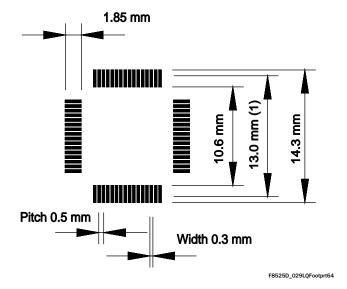

| Package Information        |       |           |

| Thermal Conditions         |       |           |

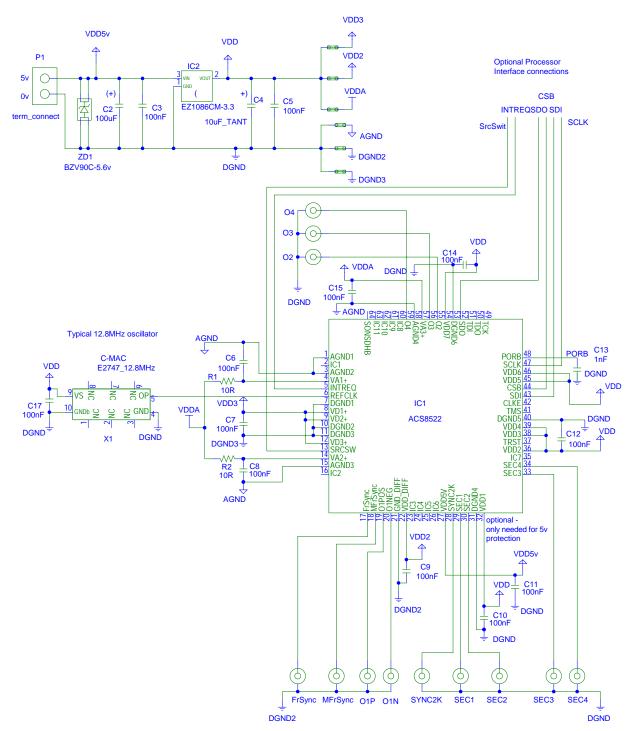

| Application Information    |       |           |

| References                 |       |           |

| Abbreviations              |       |           |

| Trademark Acknowledgements |       |           |

| Revision Status/History    |       |           |

| Ordering Information       |       |           |

| Disclaimers                |       |           |

| Contacts                   |       |           |

**FINAL**

**DATASHEET**

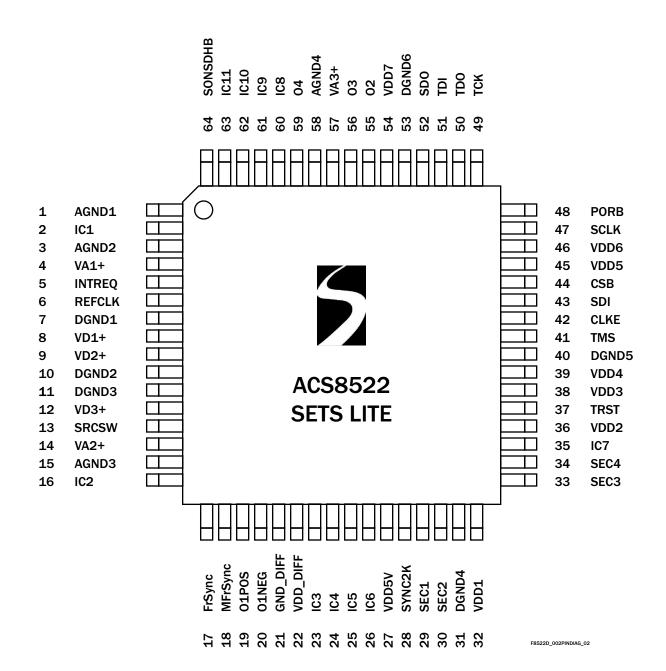

Pin Diagram

Figure 2 ACS8522 Pin Diagram Synchronous Equipment Timing Source for Stratum 3/4E/4 and SMC Systems

**FINAL**

DATASHEET

# Pin Description

### Table 1 Power Pins

| Pin Number                          | Symbol                                            | I/O | Туре | Description                                                                                                                                                                                                                       |

|-------------------------------------|---------------------------------------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8, 9,<br>12                         | VD1+, VD2+,<br>VD3+                               | Р   | -    | Supply Voltage: Digital supply to gates in analog section, +3.3 Volts ±10%.                                                                                                                                                       |

| 22                                  | VDD_DIFF                                          | Р   | -    | Supply Voltage: Digital supply for differential output pins 19 and 20, +3.3 Volts ±10%.                                                                                                                                           |

| 27                                  | VDD5V                                             | Р   | -    | VDD5V: Digital supply for +5 Volts tolerance to input pins. Connect to +5 Volts (±10%) for clamping to +5 Volts. Connect to VDD for clamping to +3.3 Volts. Leave floating for no clamping. Input pins tolerant up to +5.5 Volts. |

| 32, 36,<br>38, 39,<br>45, 46,<br>54 | VDD1, VDD2,<br>VDD3, VDD4,<br>VDD5, VDD6,<br>VDD7 | Р   | -    | Supply Voltage: Digital supply to logic, +3.3 Volts ±10%.                                                                                                                                                                         |

| 4                                   | VA1+                                              | Р   | -    | Supply Voltage: Analog supply to clock multiplying PLL, +3.3 Volts ±10%.                                                                                                                                                          |

| 14, 57                              | VA2+, VA3+                                        | Р   | -    | Supply Voltage: Analog supply to output PLLs APLL2 and APLL1, +3.3 Volts ±10%.                                                                                                                                                    |

| 15, 58                              | AGND3, AGND4                                      |     | -    | Supply Ground: Analog ground for output PLLs APLL2 and APLL1.                                                                                                                                                                     |

| 7, 10,<br>11                        | DGND1, DGND2,<br>DGND3                            | Р   | -    | Supply Ground: Digital ground for components in PLLs.                                                                                                                                                                             |

| 31, 40,<br>53                       | DGND4, DGND5,<br>DGND6                            | Р   | -    | Supply Ground: Digital ground for logic.                                                                                                                                                                                          |

| 21                                  | GND_DIFF                                          | Р   | -    | Supply Ground: Digital ground for differential output pins 19 and 20.                                                                                                                                                             |

| 1, 3                                | AGND1, AGND2                                      | Р   | -    | Supply Ground: Analog grounds.                                                                                                                                                                                                    |

Note...I = Input, O = Output, P = Power,  $TTL^U = TTL$  input with pull-up resistor,  $TTL_D = TTL$  input with pull-down resistor.

# Table 2 Internally Connected Pins

| Pin Number                                         | Symbol                                                           | I/O | Туре | Description                           |

|----------------------------------------------------|------------------------------------------------------------------|-----|------|---------------------------------------|

| 2, 16, 23, 24,<br>25, 26, 35,<br>60, 61, 62,<br>63 | IC1, IC2, IC3, IC4,<br>IC5, IC6, IC7,<br>IC8, IC9, IC10,<br>IC11 | -   | -    | Internally Connected: Leave to Float. |

### Table 3 Other Pins

| Pin Number | Symbol | I/O | Туре     | Description                                                                   |  |  |  |  |  |

|------------|--------|-----|----------|-------------------------------------------------------------------------------|--|--|--|--|--|

| 5          | INTREQ | 0   | TTL/CMOS | Interrupt Request: Active High/Low software Interrupt output.                 |  |  |  |  |  |

| 6          | REFCLK | I   | TTL      | Reference Clock: 12.800 MHz (refer to section headed Local Oscillator Clock). |  |  |  |  |  |

# FINAL

DATASHEET

Table 3 Other Pins (cont...)

| Pin Number | Symbol       | I/O | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------|--------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 13         | SRCSW        | I   | TTL <sub>D</sub> | Source Switching: Force Fast Source Switching on SEC1 and SEC2.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 17         | FrSync       | 0   | TTL/CMOS         | Output Reference: 8 kHz Frame Sync output.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 18         | MFrSync      | 0   | TTL/CMOS         | Output Reference: 2 kHz Multi-Frame Sync output.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 19, 20     | 01POS, 01NEG | 0   | LVDS/PECL        | Output Reference: Programmable, default 38.88 MHz, LVDS.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 28         | SYNC2K       | I   | TTL <sub>D</sub> | Multi-Frame Sync 2kHz input.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 29         | SEC1         | I   | TTL <sub>D</sub> | Input Reference: Programmable, default 8 kHz.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 30         | SEC2         | I   | TTL <sub>D</sub> | Input Reference: Programmable, default 8 kHz.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 33         | SEC3         | I   | TTL <sub>D</sub> | Input Reference: Programmable, default 19.44 kHz.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 34         | SEC4         | I   | TTL <sub>D</sub> | Input Reference: Programmable, default 19.44 kHz.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

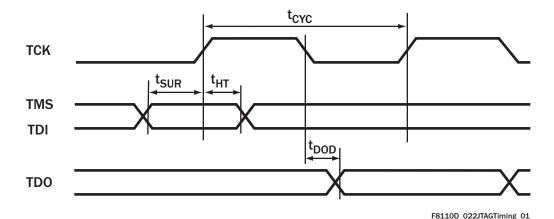

| 37         | TRST         | I   | ΠL <sub>D</sub>  | JTAG Control Reset Input: TRST = 1 to enable JTAG Boundary Scar mode. TRST = 0 for Boundary Scan stand-by mode, still allowing condevice operation. If not used connect to GND or leave floating.                                                                                                                                                                                   |  |  |  |

| 41         | TMS          | I   | TTL <sub>D</sub> | JTAG Test Mode Select: Boundary Scan enable. Sampled on rising edge of TCK. If not used connect to VDD or leave floating.                                                                                                                                                                                                                                                           |  |  |  |

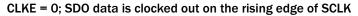

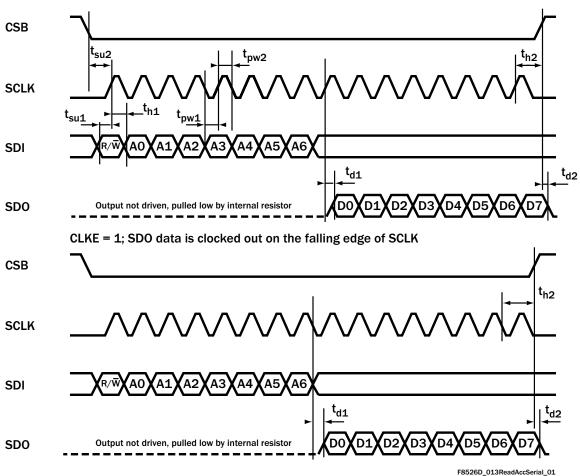

| 42         | CLKE         | I   | TTL <sub>D</sub> | SCLK Edge Select: SCLK active edge select, CLKE = 1, selects falling edge of SCLK to be active.                                                                                                                                                                                                                                                                                     |  |  |  |

| 43         | SDI          | I   | TTL <sub>D</sub> | Microprocessor Interface Address: Serial Data Input.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 44         | CSB          | I   | ΠL <sup>U</sup>  | Chip Select (Active Low): This pin is asserted Low by the microprocessor to enable the microprocessor interface.                                                                                                                                                                                                                                                                    |  |  |  |

| 47         | SCLK         | I   | TTL <sub>D</sub> | Serial Data Clock. When this pin goes High data is latched from SDI pin.                                                                                                                                                                                                                                                                                                            |  |  |  |

| 48         | PORB         | I   | TTL <sup>U</sup> | Power-On Reset: Master reset. If PORB is forced Low, all internal states are reset back to default values.                                                                                                                                                                                                                                                                          |  |  |  |

| 49         | TCK          | I   | TTL <sub>D</sub> | JTAG Clock: Boundary Scan clock input.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 50         | TDO          | 0   | TTL/CMOS         | JTAG Output: Serial test data output. Updated on falling edge of TCK.                                                                                                                                                                                                                                                                                                               |  |  |  |

| 51         | TDI          | I   | TTL <sub>D</sub> | JTAG Input: Serial test data Input. Sampled on rising edge of TCK.                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 52         | SDO          | 0   | TTL <sub>D</sub> | Interface Address: SPI compatible Serial Data Output.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 55         | 02           | 0   | TTL/CMOS         | Output Reference 2: Programmable, default 38.88 MHz.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 56         | 03           | 0   | TTL/CMOS         | Output Reference 3: Programmable, default 19.44 MHz.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 59         | 04           | 0   | TTL/CMOS         | Output Reference 4: Programmable, default 1.544/2.048 MHz (BITS).                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 64         | SONSDHB      | I   | ΠL <sub>D</sub>  | SONET or SDH Frequency Select: Sets the initial power-up state (or state after a PORB) of the SONET/SDH frequency selection registers, Reg. 34 Bit 2, and Reg. 38 Bits 5 and 6. When set <i>Low</i> , SDH rates are selected (2.048 MHz etc.), and when set <i>High</i> , SONET rates are selected (1.544 MHz etc.). The register states can be changed after power-up by software. |  |  |  |

# **FINAL**

### **DATASHEET**

# Introduction

The ACS8522 is a highly integrated, single-chip solution for the SETS function in a SONET/SDH Network Element, for the generation of SEC and Frame/MultiFrame sync pulses. Digital Phase Locked Loop (DPLL) and direct digital synthesis methods are used in the device so that the overall PLL characteristics are very stable and consistent compared to traditional analog PLLs.

In Free-run mode, the ACS8522 generates a stable, lownoise clock signal at a frequency to the same accuracy as the external oscillator, or it can be made more accurate via software calibration to within 0.02 ppm. In Locked mode, the ACS8522 selects the most appropriate input reference source and generates a stable, low-noise clock signal locked to the selected reference. In Holdover mode, the ACS8522 generates a stable, low-noise clock signal, adjusted to match the last known good frequency of the last selected reference source. A high level of phase and frequency accuracy is made possible by an internal resolution of up to 54 bits and internal Holdover accuracy of 0.0012 ppb ( $1.2 \times 10^{-12}$ ). In all modes, the frequency accuracy, jitter and drift performance of the clock meet the requirements of ITU G.736<sup>[7]</sup>, G.742<sup>[8]</sup>, G783<sup>[9]</sup>,  $G.812^{[10]}, G.813^{[11]}, G.823^{[13]}, G.824^{[14]}$  and Telcordia GR-253-CORE<sup>[17]</sup> and GR-1244-CORE<sup>[19]</sup>.

The ACS8522 supports all three types of reference clock source: recovered line clock, PDH network synchronization timing and node synchronization. The ACS8522 generates independent TO and T4 clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock.

One key architectural advantage that the ACS8522 has over traditional solutions is in the use of DPLL technology for precise and repeatable performance over temperature or voltage variations and between parts. The overall PLL bandwidth, loop damping, pull-in range and frequency accuracy are all determined by digital parameters that provide a consistent level of performance. An Analog PLL (APLL) takes the signal from the DPLL output and provides a lower jitter output. The APLL bandwidth is set four orders of magnitude higher than the DPLL bandwidth. This ensures that the overall system performance still maintains the advantage of consistent behavior provided by the digital approach.

The DPLLs are clocked by the external Oscillator module (TCXO or OCXO) so that the Free-run or Holdover frequency stability is only determined by the stability of the external oscillator module. This second key advantage

confines all temperature critical components to one well defined and pre-calibrated module, whose performance can be chosen to match the application; for example an TCXO for Stratum 3 applications.

All performance parameters of the DPLLs are programmable without the need to understand detailed PLL equations. Bandwidth, damping factor and lock range can all be set directly, for example. The PLL bandwidth can be set over a wide range, 0.1 Hz to 70 Hz in 18 steps, to cover all SONET/SDH clock synchronization applications.

The ACS8522 includes a serial port, providing access to the configuration and status registers for device setup and monitoring.

# **General Description**

### **Overview**

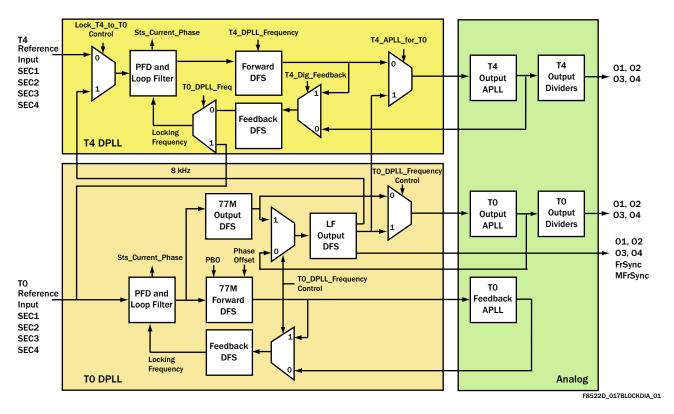

The following description refers to the Block Diagram (Figure 1 on page 1).

The ACS8522 SETS device has four SEC clock inputs (SEC1 to SEC4), and generates four output clocks on outputs O1 to O4. The device offers a total of 55 possible output frequencies. There are two independent paths through the device: TO path comprising TO DPLL and TO Output and Feedback APLLs, and T4 path comprising T4 DPLL and T4 Output APLL.

The TO path is a high quality, highly configurable path designed to provide features necessary for node timing synchronization within a SONET/SDH network. The T4 path is a simpler and less configurable path designed to give a totally independent path for internal equipment synchronization. The device supports use of either or both paths, either locked together or independent.

The four SEC inputs ports are TTL/CMOS, 3 V and 5 V compatible (with clamping if required by connecting the VDD5V pin). Refer to the electrical characteristics section for more information on the electrical compatibility and details. Input frequencies supported range from 2 kHz to 100 MHz.

Common E1, DS1, OC3 and sub-divisions are supported as spot frequencies that the DPLLs will directly lock to. Any input frequency, up to 100 MHz, that is a multiple of 8 kHz can also be locked to via an inbuilt programmable divider.

### **FINAL**

# **DATASHEET**

An input reference monitor is assigned to each of the four inputs. The monitors operate continuously such that at all times the status of all of the inputs to the device are known. Each input can be monitored for both frequency and activity, activity alone, or the monitors can be disabled.

The frequency monitors have a "hard" (rejection) alarm limit and a "soft" (flag only) alarm limit for monitoring frequency, whilst the reference is still within its allowed frequency band. Each input reference can be programmed with a priority number allowing references to be chosen according to the highest priority valid input. The two paths (TO and T4) have independent priorities to allow completely independent operation of the two paths. Both paths operate either automatic or external source selection.

For automatic input reference selection, the TO path has a more complex state machine than the T4 path.

The TO and T4 PLL paths support the following common features:

- Automatic source selection according to input priorities and quality level

- Different quality levels (activity alarm thresholds) for each input

- Variable bandwidth, lock range and damping factor

- Direct PLL locking to common SONET/SDH input frequencies or any integer multiple of 8 kHz up to 100 MHz

- Automatic mode switching between Free-run, Locked and Holdover states

- Fast detection on input failure and entry into Holdover mode (holds at the last good frequency value)

- Frequency translation between input and output rates via direct digital synthesis

- High accuracy digital architecture for stable PLL dynamics combined with an APLL for low jitter final output clocks.

There are a number of features supported by the TO path that are not supported by the T4 path, although these can also all be externally controlled by software.

The additional TO features supported are:

- Non-revertive mode

- Phase Build-out on source switch (hit-less source switching)

- I/O phase offset control

- Greater programmable bandwidth from 0.1 Hz to 70 Hz in 10 steps (T4 path programmable bandwidth in 3 steps, 18, 35 and 70 Hz)

- Noise rejection on low frequency input

- Manual Holdover frequency control

- Controllable automatic Holdover frequency filtering

- Frame Sync pulse alignment.

Either the software or an internal state machine controls the operation of the DPLL in the TO path. The state machine for the T4 path is very simple and cannot be manually/externally controlled, however the overall operation can be controlled by manual reference source selection. One additional feature of the T4 path is the ability to measure a phase difference between two inputs.

The TO path DPLL always produces an output at 77.76 MHz to feed the APLL, regardless of the frequency selected at the output pins. The T4 path can be operated at a number of frequencies. This is to enable the generation of extra output frequencies, which cannot be easily related to 77.76 MHz. When the T4 path is selected to lock to the T0 path, the T4 DPLL locks to the 8 kHz from the T0 DPLL. This is because all of the frequencies of operation of the T4 path can be divided to 8 kHz and this will ensure synchronization of all the frequencies within the two paths.

Both of the DPLLs' outputs are connected to multiplying and filtering APLLs. The outputs of these APLLs are divided making a number of frequencies simultaneously available for selection at the output clock ports. The various combinations of DPLL, APLL and divider configurations allow for generation of a comprehensive set of frequencies as listed in Table 12).

To synchronize the lower output frequencies when the TO PLL is locked to a high frequency reference input, an additional input is provided. The SYNC2K pin (pin 28) is used to reset the dividers that generate the 2 kHz and 8 kHz outputs such that the output 2/8 kHz clocks are lined up with the input 2 kHz. This synchronization method could allow for example, a master and a slave device to be in precise alignment.

The ACS8522 also supports Sync pulse references of 4 kHz or 8 kHz although in these cases frequencies lower than the Sync pulse reference may not necessarily be in phase.

# **FINAL**

# **DATASHEET**

# **Input Reference Clock Ports**

Table 4 gives details of the input reference ports, showing the input technologies and the range of frequencies supported on each port; the default spot frequencies and default priorities assigned to each port on power-up or by reset are also shown. Note that SDH and SONET networks use different default frequencies; the network type is pinselectable (using either the SONSDHB pin or via software). Specific frequencies and priorities are set by configuration.

The input ports are fully interchangeable.

SDH and SONET networks use different default frequencies; the network type is selectable using cnfg\_input\_mode Reg. 34, Bit 2 ip\_sonsdhb.

- For SONET, ip\_sonsdhb = 1

- For SDH, ip\_sonsdhb = 0

On power-up or by reset, the default will be set by the state of the SONSDHB pin (pin 64). Specific frequencies and priorities are set by configuration.

The frequency selection is programmed via the *cnfg\_ref\_source\_frequency* register (Reg. 22, 23, 27 and 28).

### **Locking Frequency Modes**

There are three locking frequency modes that can be configured: Direct Lock, Lock 8k and DivN.

#### **Direct Lock Mode**

In Direct Lock Mode, the internal DPLL can lock to the selected input at the spot frequency of the input, for example 19.44 MHz performs the DPLL phase comparisons at 19.44 MHz.

In Lock8K and DivN modes an internal divider is used prior to the DPLL to divide the input frequency before it is used for phase comparisons in the DPLL.

#### Lock8K Mode

Lock8K mode automatically sets the divider parameters to divide the input frequency down to 8 kHz. Lock8K can only be used on the supported spot frequencies (see Table 4 Note(i)). Lock8k mode is enabled by setting the Lock8k bit (Bit 6) in the appropriate cnfg\_ref\_source\_frequency register location. Using lower frequencies for phase comparisons in the DPLL results in a greater tolerance to input jitter. It is possible to choose which edge of the input reference clock to lock to, by setting 8K edge polarity (Bit 2 of Reg. 03, test\_register1).

Table 4 Input Reference Source Selection and Priority Table

| Input Port | Channel<br>Number (Bin) | Input Port<br>Technology | Frequencies Supported                                                            | Default<br>Priority |

|------------|-------------------------|--------------------------|----------------------------------------------------------------------------------|---------------------|

| SEC1       | 0011                    | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (SONET): 8 kHz Default (SDH): 8 kHz      | 2                   |

| SEC2       | 0100                    | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (SONET): 8 kHz Default (SDH): 8 kHz      | 3                   |

| SEC3       | 1000                    | TTL/CMOS                 | Up to 100 MHz (see Note (i)) Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz | 4                   |

| SEC4       | 1001                    | TTL/CMOS                 | Up to 100 MHz (see Note (i)) Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz | 5                   |

Note: (i) TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot frequency being 77.76 MHz. The actual spot frequencies are: 2 kHz, 4 kHz, 8 kHz (and N x 8 kHz), 1.544 MHz (SONET)/2.048 MHz (SDH), 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz. SONET or SDH input rate is selected via Reg. 34 Bit 2, ip\_sonsdhb).

### **FINAL**

# **DATASHEET**

#### **DivN Mode**

In DivN mode, the divider parameters are set manually by configuration (Bit 7 of the *cnfg\_ref\_source\_frequency* register), but must be set so that the frequency after division is 8 kHz. The DivN function is defined as:

DivN = "Divide by N+ 1", i.e. it is the dividing factor used for the division of the input frequency, and has a value of (N+1) where N is an integer from 1 to 12499 inclusive. Therefore, in DivN mode the input frequency can be divided by any integer value between 2 to 12500. Consequently, any input frequency which is a multiple of 8 kHz, between 8 kHz to 100 MHz, can be supported by using DivN mode.

Note...Any reference input can be set to use DivN independently of the frequencies and configurations of the other inputs. However only one value of N is allowed, so all inputs with DivN selected must be running at the same frequency.

#### **DivN Examples**

- (a) To lock to 2.000 MHz:

- (i) Set the cnfg\_ref\_source\_frequency register to 10XX0000 (binary) to enable DivN, and set the frequency to 8 kHz - the frequency required after division. (XX = "Leaky Bucket" ID for this input).

- (ii) To achieve 8 kHz, the 2 MHz input must be divided by 250. So, if DivN = 250 = (N + 1) then N must be set to 249. This is done by writing F9 hex (249 decimal) to the DivN register pair Reg. 46/47.

### (b) To lock to 10.000 MHz:

- (i) The cnfg\_ref\_source\_frequency register is set to 10XX0000 (binary) to set the DivN and the frequency to 8 kHz, the post-division frequency. (XX = "Leaky Bucket" ID for this input).

- (ii) To achieve 8 kHz, the 10 MHz input must be divided by 1,250. So, if DivN, = 250 = (N+1) then N must be set to 1,249. This is done by writing 4E1 hex (1,249 decimal) to the DivN register pair Reg. 46/47

# **Clock Quality Monitoring**

Clock quality is monitored and used to modify the priority tables. The following parameters are monitored:

- 1. Activity (toggling).

- 2. Frequency (this monitoring is only performed when there is no irregular operation of the clock or loss of clock condition).

Any reference source that suffers a loss-of-activity or clock-out-of-band condition will be declared as unavailable.

Clock quality monitoring is a continuous process which is used to identify clock problems. There is a difference in dynamics between the selected clock and the other reference clocks. Anomalies occurring on non-selected reference sources affect only that source's suitability for selection, whereas anomalies occurring on the selected clock could have a detrimental impact on the accuracy of the output clock.

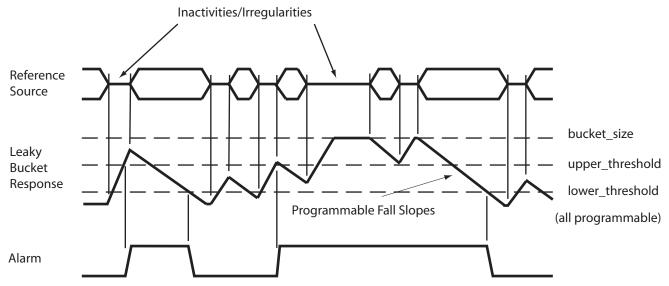

Anomalies detected by the activity detector are integrated in a Leaky Bucket Accumulator. Occasional anomalies do not cause the Accumulator to cross the alarm setting threshold, so the selected reference source is retained. Persistent anomalies cause the alarm setting threshold to be crossed and result in the selected reference source being rejected.

Anomalies on the currently locked-to input reference clock, whether affecting signal purity or signal frequency, could induce jitter or frequency offsets in the output clock, leading to anomalous behavior. Anomalies on the selected clock, therefore, have to be detected as they occur and the phase locked loop must be temporarily isolated until the clock is once again pure. The clock monitoring process cannot be used for this because the high degree of accuracy required dictates that the process be slow. To achieve the immediacy required by the phase locked loop requires an alternative mechanism.

The phase locked loop itself contains a fast activity detector such that within approximately two missing input clock cycles, a no-activity flag is raised and the DPLL is frozen in Holdover mode. This flag can also be read as the main\_ref\_failed bit (from Reg. 06, Bit 6) and can be set to indicate a phase lost state by enabling Reg. 73, Bit 6. With the DPLL in Holdover mode it is isolated from further disturbances. If the input becomes available again before the activity or frequency monitor rejection alarms have

### **FINAL**

# **DATASHEET**

been raised, then the DPLL will continue to lock to the input, with little disturbance. In this scenario, with the DPLL in the "locked" state, the DPLL uses "nearest edge locking" mode (±180° capture) avoiding cycle slips or glitches caused by trying to lock to an edge 360° away, as would happen with traditional PLLs.

### **Activity Monitoring**

The ACS8522 has a combined inactivity and irregularity monitor. The ACS8522 uses a Leaky Bucket Accumulator, which is a digital circuit which mimics the operation of an analog integrator, in which input pulses increase the output amplitude but die away over time. Such integrators are used when alarms have to be triggered either by fairly regular defect events, which occur sufficiently close together, or by defect events which occur in bursts. Events which are sufficiently spread out should not trigger the alarm. By adjusting the alarm setting threshold, the point at which the alarm is triggered can be controlled. The point at which the alarm is cleared depends upon the decay rate and the alarm clearing threshold.

On the alarm setting side, if several events occur close together, each event adds to the amplitude and the alarm will be triggered quickly; if events occur further apart, but still sufficiently close together to overcome the decay, the alarm will be triggered eventually. If events occur at a rate which is not sufficient to overcome the decay, the alarm will not be triggered. On the alarm clearing side, if no defect events occur for a sufficient time, the amplitude will decay gradually and the alarm will be cleared when the amplitude falls below the alarm clearing threshold. The ability to decay the amplitude over time allows the importance of defect events to be reduced as time passes by. This means that, in the case of isolated events, the alarm will not be set, whereas, once the alarm becomes set, it will be held on until normal operation has persisted for a suitable time (but if the operation is still erratic, the alarm will remain set). See Figure 3.

There is one Leaky Bucket Accumulator per input channel. Each Leaky Bucket can select from four Configurations (Leaky Bucket Configuration 0 to 3). Each Leaky Bucket Configuration is programmable for size, alarm set and reset thresholds, and decay rate.

Each source is monitored over a 128 ms period. If, within a 128 ms period, an irregularity occurs that is not deemed to be due to allowable jitter/wander, then the Accumulator is incremented.

The Accumulator will continue to increment up to the point that it reaches the programmed Bucket size. The "fill rate" of the Leaky Bucket is, therefore, 8 units/second. The "leak rate" of the Leaky Bucket is programmable to be in multiples of the fill rate (x 1, x 0.5, x 0.25 and x 0.125) to give a programmable leak rate from 8 units/sec down to 1 unit/sec. A conflict between trying to "leak" at the same time as a "fill" is avoided by preventing a leak when a fill event occurs.

Disqualification of a non-selected reference source is based on inactivity, or on an out-of-band result from the frequency monitors. The currently selected reference source can be disqualified for phase, frequency, inactivity or if the source is outside the DPLL lock range. If the currently selected reference source is disqualified, the next highest priority, qualified reference source is selected.

### **Interrupts for Activity Monitors**

The loss of the currently selected reference source will eventually cause the input to be considered invalid, triggering an interrupt, if not masked. The time taken to raise this interrupt is dependent on the Leaky Bucket Configuration of the activity monitors. The fastest Leaky Bucket setting will still take up to 128 ms to trigger the interrupt. The interrupt caused by the brief loss of the currently selected reference source is provided to facilitate very fast source failure detection if desired. It is triggered after missing just a couple of cycles of the reference source. Some applications require the facility to switch downstream devices based on the status of the reference sources. In order to provide extra flexibility, it is possible to flag the main\_ref\_failed interrupt (Reg. 06 Bit 6) on the pin TDO. This is simply a copy of the status bit in the interrupt register and is independent of the mask register settings. The bit is reset by writing to the interrupt status register in the normal way. This feature can be enabled and disabled by writing to Reg. 48 Bit 6.

**FINAL**

**DATASHEET**

Figure 3 Inactivity and Irregularity Monitoring

#### **Leaky Bucket Timing**

The time taken (in seconds) to raise an inactivity alarm on a reference source that has previously been fully active (Leaky Bucket empty) will be:

where n is the number of the Leaky Bucket Configuration. If an input is intermittently inactive then this time can be longer. The default setting of *cnfg\_upper\_threshold* is 6, therefore the default time is 0.75 s.

The time taken (in seconds) to cancel the activity alarm on a previously completely inactive reference source is calculated, for a particular Leaky Bucket, as:

$$[2^{(a)} x (b - c)]/8$$

where:

a = cnfg\_decay\_rate\_n

b = cnfg\_bucket\_size\_n

c = cnfg\_lower\_threshold\_n

(where n = the number of the relevant Leaky Bucket Configuration in each case).

The default setting is shown in the following:

$$[2^{1} \times (8 - 4)] / 8 = 1.0 \text{ secs}$$

### **Frequency Monitoring**

The ACS8522 performs input frequency monitoring to identify reference sources which have drifted outside the acceptable frequency range measured with respect either to the output clock or to the XO clock.

The sts\_reference\_sources out-of-band alarm for a particular reference source is raised when the reference source is outside the acceptable frequency range. With the default register settings a soft alarm is raised if the drift is outside  $\pm 11.43$  ppm and a hard alarm is raised if the drift is outside  $\pm 15.24$  ppm. Both of these limits are programmable from 3.8 ppm up to 61 ppm.

The ACS8522 DPLL has a programmable lock and capture range frequency limit up to  $\pm 80$  ppm (default is  $\pm 9.2$  ppm).

# **Selection of Input Reference Clock Source**

Under normal operation, the input reference sources are selected automatically by an order of priority. But, for special circumstances, such as chip or board testing, the selection may be forced by configuration.

Automatic operation selects a reference source based on its pre-defined priority and its current availability. A table is maintained which lists all reference sources in the order of priority. This is initially defined by the default configuration and can be changed via the Serial interface by the Network Manager. In this way, when all the defined sources are active and valid, the source with the highest programmed priority is selected but, if this source fails, the next-highest source is selected, and so on.

Restoration of repaired reference sources is handled carefully to avoid inadvertent disturbance of the output clock. For this, the ACS8522 has two modes of operation; Revertive and Non-revertive.

### **FINAL**

# **DATASHEET**

In Revertive mode, if a re-validated (or newly validated) source has a higher priority than the reference source which is currently selected, a switch over will take place. Many applications prefer to minimize the clock switching events and choose Non-revertive mode.

In Non-revertive mode, when a re-validated (or newly validated) source has a higher priority then the selected source will be maintained. The re-validation of the reference source will be flagged in the sts\_sources\_valid register (Reg. OE and OF) and, if not masked, will generate an interrupt. Selection of the re-validated source can take place under software control or if the currently selected source fails.

To enable software control, the software should briefly enable Revertive mode to effect a switch-over to the higher priority source. When there is a reference available with higher priority than the selected reference, there will be NO change of reference source as long as the Non-revertive mode remains on, and the currently selected source is valid. A failure of the selected reference will always trigger a switch-over regardless of whether Revertive or Non-revertive mode has been chosen.

### **Forced Control Selection**

A configuration register, force\_select\_reference\_source Reg. 33, controls both the choice of automatic or forced selection and the selection itself (when forced selection is required). For Automatic choice of source selection, the four LSB bit value is set to all zeros or all ones (default). To force a particular input the bit value must be set as follows: 0011 forces SEC1, 0100 forces SEC2, 1000 forces SEC3 and 1001 forces SEC4. Forced selection is not the normal mode of operation, and the force\_select\_reference\_source variable is defaulted to the all-one value on reset, thereby adopting the automatic selection of the reference source.

#### **Automatic Control Selection**

When an automatic selection is required, the force\_select\_reference\_source register LSB four bits must be set to all zeros or all ones. The configuration registers, cnfg\_ref\_selection\_priority (Reg. 19, 1B and 1C), hold 4-bit values which represents the desired priority of that particular port. Unused ports should be given the value 0000 in the relevant register to indicate they are not to be included in the priority table. On power-up, or following a reset, the whole of the configuration file will be defaulted to the values defined

by Table 4. The selection priority values are all relative to each other, with lower-valued numbers taking higher priorities. Each reference source should be given a unique number: the valid values are 1 to 15 (dec). A value of zero disables the reference source. However if two or more inputs are given the same priority number those inputs will be selected on a first in, first out basis. If the first of two same priority number sources goes invalid the second will be switched in. If the first then becomes valid again, it becomes the second source on the first in, first out basis, and there will not be a switch. If a third source with the same priority number as the other two becomes valid, it joins the priority list on the same first in, first out basis. There is no implied priority based on the channel numbers. Revertive/Non-revertive mode has no effect on sources with the same priority value.

### **Ultra Fast Switching**

A reference source is normally disqualified after the Leaky Bucket monitor thresholds have been crossed. An option for a faster disqualification has been implemented, whereby if Reg. 48 Bit 5 (*ultra\_fast\_switch*) is set, then a loss of activity of just a few reference clock cycles will set the *main\_ref\_failed* alarm and cause a reference switch. This can be configured (see Reg. 06, Bit 6) to cause an interrupt to occur instead of, or as well as, causing the reference switch.

The sts\_interrupts register Reg. 06 Bit 6 (main\_ref\_failed) is used to flag inactivity on the reference that the device is locked to much faster than the activity monitors can support. If Reg. 48 Bit 6 of the cnfg\_monitors register (los\_flag\_on\_TDO) is set, then the state of this bit is driven onto the TDO pin of the device.

Note... The flagging of the loss of the main reference failure on TDO is simply allowing the status of the sts\_interrupts bit main\_ref\_failed (Reg. 06, Bit 6) to be reflected in the state of the TDO output pin. The pin will, therefore, remain High until the interrupt is cleared. This functionality is not enabled by default so the usual JTAG functions can be used. When the TDO output from the ACS8522 is connected to the TDI pin of the next device in the JTAG scan chain, the implementation should be such that a logic change caused by the action of the interrupt on the TDI input should not effect the operation when JTAG is not active.

### Fast External Switching Mode-SRCSW pin

Fast External Switching mode allows fast switching between inputs SEC1 and SEC2 only. The mode must first be enabled before switching can take place, and then switching is controlled via the SRCSW pin.

**FINAL**

# **DATASHEET**

There are two ways to enable Fast External Switching mode:

- Mode enable by register write by writing to Reg. 48 Bit 4, or

- Mode enable by hardware "initialization" by holding SRCSW High throughout reset and for at least a further 251 ms after PORB has gone High (250 ms allowance for the internal reset to be removed plus 1 ms allowance for APLLs to start-up and become stable). A simple external circuit to set SCRSW high for the required period is shown in "Simplified Application Schematic" on page 114. If SCRSW pin is held Low at any time during the 251 ms initialization period, this may result in Fast External Switching mode not being enabled correctly.

Once Fast External Switching mode is enabled, then the value of the SRCSW pin directly selects either SEC1 (SRCSW High) or SEC2 (SRCSW Low). If this mode is enabled by hardware initialization, then it configures the default frequency tolerance of SEC1 and SEC2 to  $\pm$  80 ppm (Reg. 41 and Reg. 42). Either of these registers can be subsequently reconfigured by external software, if required.

When Fast External Switching mode is enabled, the device operates as a simple switch. All clock monitoring is disabled and the DPLL will simply be forced to try to lock on to the indicated reference source. Consequently the device will always indicate "locked" state in the sts\_operating register (Reg. 09, Bits 2:0).

# **Output Clock Phase Continuity on Source Switchover**

If either PBO is selected on (default), or, if DPLL frequency limit is set to less than  $\pm 30$  ppm or ( $\pm 9.2$  ppm default), the device will always comply with GR-1244-CORE<sup>[19]</sup> specification for Stratum 3 (maximum rate of phase change of 81 ns/1.326 ms), for all input frequencies.

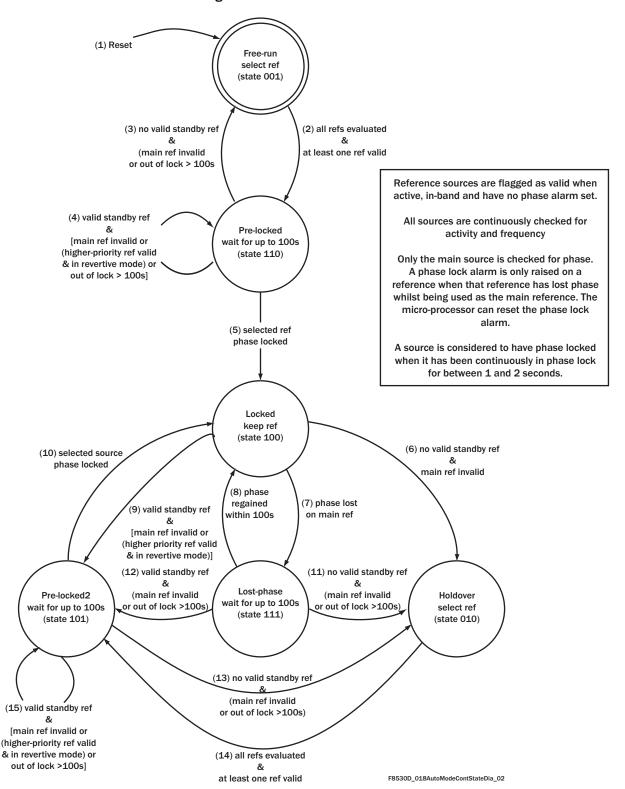

# **Modes of Operation**

The ACS8522 has three primary modes of operation (Free-run, Locked and Holdover) supported by three secondary, temporary modes (Pre-locked, Lost-phase and Pre-locked2). These are shown in the State Transition Diagram, Figure 4.

The ACS8522 can operate in Forced or Automatic control. On reset, the ACS8522 reverts to Automatic Control, where transitions between states are controlled

completely automatically. Forced Control can be invoked by configuration, allowing transitions to be performed under external control. This is not the normal mode of operation, but is provided for special occasions such as testing, or where a high degree of hands-on control is required.

#### Free-run Mode

The Free-run mode is typically used following a power-on-reset or a device reset before network synchronization has been achieved. In the Free-run mode, the timing and synchronization signals generated from the ACS8522 are based on the 12.800 MHz clock frequency provided from the external oscillator and are not synchronized to an input reference source. By default, the frequency of the output clock is a fixed multiple of the frequency of the external oscillator, and the accuracy of the output clock is equal to the accuracy of the oscillator. However the external oscillator frequency can be calibrated to improve its accuracy by a software calibration routine using register <code>cnfg\_nominal\_frequency</code> (Reg. 3C and 3D). For example a 500 ppm offset crystal could be made to look like one accurate to within ±0.02 ppm.

The transition from Free-run to Pre-locked occurs when the ACS8522 selects a reference source.

#### **Pre-locked Mode**

The ACS8522 will enter the Locked state in a maximum of 100 seconds, as defined by GR-1244-CORE<sup>[19]</sup> specification, if the selected reference source is of good quality. If the device cannot achieve lock within 100 seconds, it reverts to Free-run mode and another reference source is selected.

#### **Locked Mode**

The Locked mode is entered from Pre-locked, Pre-locked2 or Phase-lost mode when an input reference source has been selected and the DPLL has locked. The DPLL is considered to be locked when the phase loss/lock detectors (See"Phase Lock/Loss Detection" on page 19) indicate that the DPLL has remained in phase lock continuously for at least one second. When the ACS8530 is in Locked mode, the output frequency and phase tracks that of the selected input reference source.

# **Lost-phase Mode**

Lost-phase mode is used whenever the phase loss/lock detectors (See"Phase Lock/Loss Detection" on page 19)

### **FINAL**

# **DATASHEET**

indicate that the DPLL has lost phase lock. The DPLL will still be trying to lock to the input clock reference, if it exists. If the Leaky Bucket Accumulator calculates that the anomaly is serious, the device disqualifies the reference source. If the device spends more than 100 seconds in Lost-phase mode, the reference is disqualified and a phase alarm is raised on it. If the reference is disqualified, one of the following transitions takes place:

- 1. Go to Pre-locked2:

- If a known good stand-by source is available.

- 2. Go to Holdover:

- If no stand-by sources are available.

#### **Holdover Mode**

Holdover mode is the operating condition the device enters when its currently selected input source becomes invalid, and no other valid replacement source is available. In this mode, the device resorts to using stored frequency data, acquired when the input reference source was still valid, to control its output frequency.

In Holdover mode, the ACS8522 provides the timing and synchronization signals to maintain the Network Element but is not phase locked to any input reference source. Its output frequency is determined by an averaged version of the DPLL frequency when last in the Locked Mode.

Holdover can be configured to operate in either:

- Automatic mode

(Reg. 34 Bit 4, cnfg\_input\_mode: man\_holdover set Low), or

- Manual mode

(Reg. 34 Bit 4, cnfg\_input\_mode: man\_holdover set

High).

#### **Automatic Mode**

In Automatic mode, the device can be configured to operate using either:

- Averaged (Reg. 40 Bit 7, cnfg\_holdover\_modes, auto\_averaging: set High), or

- Instantaneous (Reg. 40 Bit 7, cnfg\_holdover\_modes, auto\_averaging: set Low).

#### **Averaged**

In the Averaged mode, the frequency (as reported by sts\_current\_DPLL\_frequency, see Reg. OC, Reg. OD and Reg. O7) is filtered internally using an Infinite Impulse Response filter, which can be set to either:

- Fast (Reg. 40 Bit 6, cnfg\_holdover\_modes, fast\_averaging: set High), giving a -3 dB filter response point corresponding to a period of approximately eight minutes, or

- Slow (Reg. 40 Bit 6, cnfg\_holdover\_modes, fast\_averaging: set Low) giving a -3 dB filter response point corresponding to a period of approximately 110 minutes

#### Instantaneous

In Instantaneous mode, the DPLL freezes at the frequency it was operating at the time of entering Holdover mode. It does this by using only its internal DPLL integral path value (as reported in Reg. OC, OD, and O7) to determine output frequency. The DPLL proportional path is not used so that any recent phase disturbances have a minimal effect on the Holdover frequency. The integral value used can be viewed as a filtered version of the locked output frequency over a short period of time. The period being in inverse proportion to the DPLL bandwidth setting.

#### **Manual Mode**

(Reg. 34 Bit 4, cnfg\_input\_mode, man\_holdover set High.) The Holdover frequency is determined by the value in register cnfg\_holdover\_frequency (Reg. 3E, Reg. 3F, and part of Reg. 40). This is a 19-bit signed number, with a LSB resolution of 0.0003068 ppm, which gives an adjustment range of ±80 ppm. This value can be derived from a reading of the register sts current DPLL frequency (Reg. OD, OC and O7), which gives, in the same format, an indication of the current output frequency deviation, which would be read when the device is locked. If required, this value could be read by external software and averaged over time. The averaged value could then be fed to the cnfg\_holdover\_frequency register, ready for setting the averaged frequency value when the device enters Holdover mode. The sts\_current\_DPLL\_frequency value is internally derived from the Digital Phase Locked Loop (DPLL) integral path, which represents a short-term average measure of the current frequency, depending on the locked loop bandwidth (Reg. 67) selected.

It is also possible to combine the internal averaging filters with some additional software filtering. For example the internal fast filter could be used as an anti-aliasing filter and the software could further filter this before determining the actual Holdover frequency. To support this feature, a facility to read out the internally averaged frequency has been provided.

# **FINAL**

**DATASHEET**

Figure 4 Automatic Mode Control State Diagram

# **FINAL**

# **DATASHEET**

By setting Reg. 40, Bit 5, <code>cnfg\_holdover\_modes</code>, <code>read\_average</code>, the value read back from the <code>cnfg\_holdover\_frequency</code> register will be the filtered value. The filtered value is available regardless of what actual Holdover mode is selected. Clearly this results in the register not reading back the data that was written to it.

#### Example: Software averaging to eliminate temperature drift.

Select Manual Holdover mode by setting Reg. 34 Bit 4, cnfg\_input\_mode, man\_holdover High.

Select Fast Holdover Averaging mode by setting Reg. 40 Bit 6, *cnfg\_holdover\_modes*, *auto\_averaging High* and Reg. 40 Bit 7 *High*.

Select to be able to read back filtered output by setting Reg. 40 Bit 5, cnfg\_holdover\_modes, read\_average High.

Software periodically reads averaged value from the *cnfg\_holdover\_frequency* register and the temperature (not supplied from ACS8522). Software processed frequency and temperature and places data in software look-up table or other algorithm. Software writes back appropriate averaged value into the *cnfg\_holdover\_frequency* register.

Once Holdover mode is entered, software periodically updates the *cnfg\_holdover\_frequency* register using the temperature information (not supplied from ACS8522).

#### Mini-holdover Mode

Holdover mode so far described refers to a state to which the internal state machine switches as a result of activity or frequency alarms, and this state is reported in Reg. 09. To avoid the DPLL's frequency being pulled off as a result of a failed input, then the DPLL has a fast mechanism to freeze its current frequency within one or two cycles of the input clock source stopping. Under these circumstances the DPLL enters Mini-holdover mode; the Mini-holdover frequency used being determined by Reg. 40, Bits [4:3], cnfg\_holdover\_modes, mini\_holdover\_mode.

Mini-holdover mode only lasts until one of the following happens:

- A new source has been selected, or

- The state machine enters Holdover mode, or

- The original fault on the input recovers.

#### **External Factors Affecting Holdover Mode**

If the external TCXO/OCXO frequency is varying due to temperature fluctuations in the room, then the

instantaneous value can be different from the average value, and then it may be possible to exceed the 0.05 ppm limit (depending on how extreme the temperature fluctuations are). It is advantageous to shield the TCXO/OCXO to slow down frequency changes due to drift and external temperature fluctuations.

The frequency accuracy of Holdover mode has to meet the ITU-T, ETSI and Telcordia performance requirements. The performance of the external oscillator clock is critical in this mode, although only the frequency stability is important - the stability of the output clock in Holdover is directly related to the stability of the external oscillator.

### Pre-locked2 Mode

This state is very similar to the Pre-Locked state. It is entered from the Holdover state when a reference source has been selected and applied to the phase locked loop. It is also entered if the device is operating in Revertive mode and a higher-priority reference source is restored.

Upon applying a reference source to the phase locked loop, the ACS8522 will enter the Locked state in a maximum of 100 seconds, as defined by GR-1244-CORE<sup>[19]</sup> specification, if the selected reference source is of good quality.

If the device cannot achieve lock within 100 seconds, it reverts to Holdover mode and another reference source is selected.

# **DPLL Architecture and Configuration**

A Digital PLL gives a stable and consistent level of performance that can be easily programmed for different dynamic behavior or operating range. It is not affected by operating conditions or silicon process variations. Digital synthesis is used to generate all required SONET/SDH output frequencies. The digital logic operates at 204.8 MHz that is multiplied up from the external 12.800 MHz oscillator module. Hence the best resolution of the output signals from the DPLL is one 204.8 MHz cycle or 4.9 ns.

Additional resolution and lower final output jitter is provided by a de-jittering Analog PLL that reduces the 4.9 ns pk-pk jitter from the digital down to 500 ps pk-pk and 60 ps RMS as typical final outputs measured broadband (from 10 Hz to 1 GHz).

This arrangement combines the advantages of the flexibility and repeatability of a DPLL with the low jitter of an APLL. The DPLLs in the ACS8522 are uniquely very

### **FINAL**

# **DATASHEET**

programmable for all PLL parameters of bandwidth (from 0.1 Hz up to 70 Hz), damping factor (from 1.2 to 20), frequency acceptance and output range (from 0 to 80 ppm, typically 9.2 ppm), input frequency (12 common SONET/SDH spot frequencies) and input-to-output phase offset (in 6 ps steps up to 200 ns). There is no requirement to understand the loop filter equations or detailed gain parameters since all high level factors such as overall bandwidth can be set directly via registers in the microprocessor interface. No external critical components are required for either the internal DPLLs or APLLs, providing another key advantage over traditional discrete designs.

The T4 DPLL is similar in structure to the T0 DPLL, but since the T4 is only providing a clock synthesis and input to output frequency translation function, with no defined requirement for jitter attenuation or input phase jump absorption, then its bandwidth is limited to the high end and the T4 does not incorporate many of the Phase Buildout and adjustment facilities of the T0 DPLL.

#### **TO DPLL Main Features**

- Two programmable DPLL bandwidth controls (Locked and Acquisition bandwidth), each with 10 steps from 0.1 Hz to 70 Hz

- Programmable damping factor: For optional faster locking and peaking control. Factors = 1.2, 2.5, 5, 10 or 20

- Multiple phase lock detectors

- Input to output phase offset adjustment (Master/Slave), ±200 ns, 6 ps resolution step size

- PBO phase offset on source switching disturbance down to ±5 ns

- Multi-cycle phase detection and locking, programmable up to ±8192 UI - improves jitter tolerance in direct lock mode

- Holdover frequency averaging with a choice of: Average times: 8 minutes or 110 minutes. Value can also be read out.

- Multiple E1 and DS1 outputs supported

- Low jitter MFrSync (2 kHz) and FrSync (8 kHz) outputs.

#### **T4 DPLL Main Features**

- Single programmable DPLL bandwidth control: 18 Hz, 35 Hz or 70 Hz

- Programmable damping factor: For optional faster locking and peaking control. Factors = 1.2, 2.5, 5, 10 or 20

- Multiple phase lock detectors

- Multi-cycle phase detection and locking, programmable up to ±8192 UI - improves jitter tolerance in direct lock mode

- DS3/E3 support (44.736 MHz / 34.368 MHz) at same time as OC-N rates from TO DPLL

- Low jitter E1/DS1 options at same time as OC-N rates from T0 DPLL

- Frequencies of n x E1/DS1 including 16 and 12 x E1, and 16 and 24 x DS1 supported

- Low jitter MFrSync (2 kHz) and FrSync (8 kHz) outputs

- Can use the T4 DPLL as an Independent FrSync DPLL

- Can use the phase detector in T4 DPLL to measure the input phase difference between two inputs.

The structure of the TO and T4 PLLs are shown later in Figure 10 in the section on output clock ports. That section also details how the DPLLs and particular output frequencies are configured. The following sections detail some component parts of the DPLL.

#### **TO DPLL Automatic Bandwidth Controls**

In Automatic Bandwidth Selection mode (Reg. 3B), the TO DPLL bandwidth setting is selected automatically from the Acquisition Bandwidth or Locked Bandwidth configurations programmed in <code>cnfg\_TO\_DPLL\_acq\_bw</code> Reg. 69 and <code>cnfg\_TO\_DPLL\_locked\_bw</code> Reg. 67 respectively. If this mode is not selected, the DPLL acquires and locks using only the bandwidth set by Reg. 67.

#### **Phase Detectors**

A Phase and Frequency detector is used to compare input and feedback clocks. This operates at input frequencies up to 77.76 MHz. The whole DPLL can operate at spot frequencies from 2 kHz up to 77.76 MHz. A common arrangement however is to use Lock8k mode (see Bit 6 of Reg. 22, 23, 27 and 28) where all input frequencies are divided down to 8 kHz internally. Marginally better MTIE figures may be possible in direct lock mode due to more regular phase updates.

### **FINAL**

#### DATASHEET

A patented multi-phase detector is used in order to give an infinitesimally small input phase resolution combined with large jitter tolerance. The following phase detectors are used:

- Phase and frequency detector (±360° or ±180° range)

- An early/late phase detector for fine resolution

- A multi-cycle phase detector for large input jitter tolerance (up to 8191 UI), which captures and remembers phase differences of many cycles between input and feedback clocks.

The phase detectors can be configured to be immune to occasional missing input clock pulses by using nearest edge detection ( $\pm 180^{\circ}$  capture) or the normal  $\pm 360^{\circ}$  phase capture range which gives frequency locking. The device will automatically switch to nearest edge locking when the multi-UI phase detector is not enabled and the other phase detectors have detected that phase lock has been achieved.

It is possible to disable the selection of nearest edge locking via Reg. 03 Bit 6 set to 1. In this setting, frequency locking will always be enabled.

The balance between the first two types of phase detector employed can be adjusted via registers 6A to6D. The default settings should be sufficient for all modes. Adjustment of these settings affects only small signal overshoot and bandwidth.

The multi-cycle phase detector is enabled via Reg. 74, Bit 6 set to 1 and the range is set in exponentially increasing steps from ±1 UI, 3 UI, 7 UI, 15 UI ... up to 8191 UI via Reg. 74, Bits [3:0].

When this detector is enabled it keeps a track of the correct phase position over many cycles of phase difference to give excellent jitter tolerance. This provides an alternative to switching to Lock8k mode as a method of achieving high jitter tolerance.

An additional control (Reg. 74 Bit 5) enables the multiphase detector value to be used in the final phase value as part of the DPLL loop. When enabled by setting *High*, the multi cycle phase value will be used in the loop and gives faster pull in (but more overshoot). The characteristics of the loop will be similar to Lock8k mode where again large input phase differences contribute to the loop dynamics. Setting the bit *Low* only uses a max figure of 360 degrees in the loop and will give slower pullin but gives less overshoot. The final phase position that

the loop has to pull in to is still tracked and remembered by the multi-cycle phase detector in either case.

### Phase Lock/Loss Detection

Phase lock/loss detection is handled in several ways. Phase loss can be triggered from:

- The fine phase lock detector, which measures the phase between input and feedback clock

- The coarse phase lock detector, which monitors whole cycle slips

- Detection that the DPLL is at min. or max. frequency

- Detection of no activity on the input.

Each of these sources of phase loss indication is individually enabled via register bits (see Reg. 73, 74 and 4D). Phase lock or lost is used to determine whether to switch to nearest edge locking and whether to use acquisition or Locked bandwidth settings for the DPLL. Acquisition bandwidth is used for faster pull-in from an unlocked state.

The coarse phase lock detector detects phase differences of n cycles between input and feedback clocks, where n is set by Reg. 74, Bits 3:0; the same register that is used for the coarse phase detector range, since these functions go hand in hand. This detector may be used in the case where it is required that a phase loss indication is not given for reasonable amounts of input jitter and so the fine phase loss detector is disabled and the coarse detector is used instead.

### **Damping Factor Programmability**

The DPLL damping factor is set by default to provide a maximum wander gain peak of around 0.1 dB. Many of the specifications (e.g. GR-1244-CORE<sup>[19]</sup>, G.812<sup>[10]</sup> and G.813<sup>[11]</sup>) specify a wander transfer gain of less than 0.2 dB. GR-253<sup>[17]</sup> specifies jitter (not wander) transfer of less than 0.1 dB. To accommodate the required levels of transfer gain, the ACS8522 provides a choice of damping factors, with more choice given as the bandwidth setting increases into the frequency regions classified as jitter. Table 5 shows which damping factors are available for selection at the different bandwidth settings, and what the corresponding jitter transfer approximate gain peak will be.

### **FINAL**

# **DATASHEET**

Table 5 Available Damping Factors for different DPLL Bandwidths, and associated Jitter Peak Values

| Bandwidth      | Reg. 6B [2:0] | Damping<br>Factor selected | Gain Peak/ dB |  |  |

|----------------|---------------|----------------------------|---------------|--|--|

| 0.1 Hz to 4 Hz | 1, 2, 3, 4, 5 | 5                          | 0.1           |  |  |

| 8 Hz           | 1             | 2.5                        | 0.2           |  |  |

|                | 2, 3, 4, 5    | 5                          | 0.1           |  |  |

| 18 Hz          | 1             | 1.2                        | 0.4           |  |  |

|                | 2             | 2.5                        | 0.2           |  |  |

|                | 3, 4, 5       | 5                          | 0.1           |  |  |

| 35 Hz          | 1             | 1.2                        | 0.4           |  |  |

|                | 2             | 2.5                        | 0.2           |  |  |

|                | 3             | 5                          | 0.1           |  |  |

|                | 4, 5          | 10                         | 0.06          |  |  |

| 70 Hz          | 1             | 1.2                        | 0.4           |  |  |

|                | 2             | 2.5                        | 0.2           |  |  |

|                | 3             | 5                          | 0.1           |  |  |

|                | 4             | 10                         | 0.06          |  |  |

|                | 5             | 20                         | 0.03          |  |  |

#### **Local Oscillator Clock**

The Master system clock on the ACS8522 should be provided by an external clock oscillator of frequency 12.800 MHz. The clock specification is important for meeting the ITU/ETSI and Telcordia performance requirements for Holdover mode. ITU and ETSI specifications permit a combined drift characteristic, at constant temperature, of all non-temperature-related parameters, of up to 10 ppb per day. The same specifications allow a drift of 1 ppm over a temperature range of 0 to +70°C.

Table 6 ITU and ETSI Specification

| Parameter                          | Value                                 |

|------------------------------------|---------------------------------------|

| Tolerance                          | ±4.6 ppm over 20 year lifetime        |