### **General Description**

The DS2127 Ultra3 LVD/SE SCSI terminator provides low-voltage differential (LVD)/single-ended (SE) terminations for 14 SCSI lines. Through the voltage on the DIFF\_CAP pin, the device detects the types of drivers on the bus. If the device is connected in an LVD-only bus, the DS2127 provides LVD termination. If any single-ended devices are connected to the bus, the DS2127 uses SE termination. If any high-voltage differential (HVD) devices are connected to the bus, the DS2127 isolates itself from the SCSI bus. The mode change has a built-in delay that is determined by an integrated SPI-3 mode change filter/delay. The terminating resistors can also be disconnected from the bus by asserting the ISO pin.

For the LVD termination, the DS2127 provides 14 precisely trimmed resistors. Each resistor is biased with two current sources to a fail-safe state. For SE termination, the DS2127 provides 14 precision  $110\Omega$  resistors and one regulator for active-negation bias.

**Applications**

SCSI Array Backplane SCSI Cables

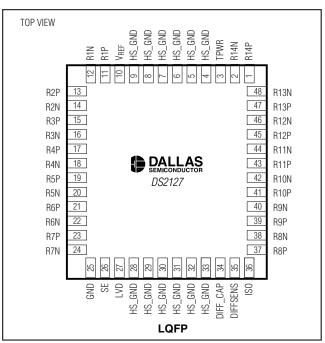

# Pin Configuration

#### **Features**

- ♦ Fully Compliant with Ultra2, Ultra3, Ultra160, and **Ultra320 SCSI Standards**

- ♦ Provides LVD/SE Termination for 14 Signal Pairs

- **♦** Auto-Selection of LVD or SE Termination

- ♦ 5% Tolerance on SE and LVD Termination Resistance

- **♦ Low 3pF Power-Down Capacitance**

- ♦ Built-In Mode-Change Filter/Delay

- ♦ On-Board Thermal-Shutdown Circuitry

- ♦ SCSI Bus Hot-Plug Compatible

- **♦ Fully Supports Actively Negated SE SCSI Signals**

## **Ordering Information**

| PART*      | VOLTAGE<br>(V) | PIN-PACKAGE              | TOP<br>MARK** |

|------------|----------------|--------------------------|---------------|

| DS2127     | 3.3            | 48 LQFP                  | DS2127        |

| DS2127+    | 3.3            | 48 LQFP                  | DS2127        |

| DS2127/T&R | 3.3            | 48 LQFP/Tape<br>and Reel | DS2127        |

| DS2127+T&R | 3.3            | 48 LQFP/Tape<br>and Reel | DS2127        |

- +Denotes a lead-free/RoHS-compliant package.

- \*All devices rated over the 0°C to +70°C commercial temperature range.

- \*\*The top mark includes a "+" on lead-free packages.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on All Pins Relative to Ground0.3V to +6.0V | Storage Temperature Range65°C to +160°C |

|-----------------------------------------------------------|-----------------------------------------|

| V <sub>REF</sub> Continuous Output Current±200mA          | Soldering TemperatureSee IPC/JEDEC      |

| Operating Temperature Range0°C to +70°C                   | J-STD-020A Specification                |

| Junction Temperature+150°C                                |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(TPWR = V<sub>TPWR</sub>(MIN) to V<sub>TPWR</sub>(MAX),  $T_A = 0$ °C to +70°C, unless otherwise noted.)

| PARAMETER                                       | SYMBOL                                                                   | CONDITIONS                                                                                                                                                                                                                                                          | MIN   | TYP  | MAX   | UNITS |  |

|-------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|--|

| TPWR Operating Supply Range (Note 1)            | V <sub>TPWR</sub>                                                        | LVD                                                                                                                                                                                                                                                                 | 2.7   | 3.3  | 5.5   | V     |  |

|                                                 |                                                                          | SE                                                                                                                                                                                                                                                                  | 4     | 5.0  | 5.5   |       |  |

| TPWR SUPPLY CURRENT                             |                                                                          |                                                                                                                                                                                                                                                                     |       |      |       |       |  |

| TPWR Supply Current (All Lines                  | ITPWR_LVD                                                                | LVD SCSI mode                                                                                                                                                                                                                                                       |       |      | 32    | mA    |  |

|                                                 | ITPWR_SE                                                                 | SE SCSI mode                                                                                                                                                                                                                                                        |       |      | 10    | μA    |  |

| Open)                                           | ITPWR_ISO                                                                | ISO mode (terminators disabled)                                                                                                                                                                                                                                     |       |      | 750   |       |  |

| LVD TERMINATION (Applies to ea                  | ach line pair,                                                           | 1 to 14 in LVD mode)                                                                                                                                                                                                                                                |       |      |       |       |  |

| Differential-Mode Termination<br>Resistance     | R <sub>DM</sub>                                                          |                                                                                                                                                                                                                                                                     | 100   |      | 110   | Ω     |  |

| Common-Mode Termination<br>Resistance           | R <sub>CM</sub>                                                          | Rp and R <sub>N</sub> shorted together (VCM(MAX) = 2V, VCM(MIN) = 0.5V)                                                                                                                                                                                             | 110   |      | 165   | Ω     |  |

| Differential-Mode Bias                          | $V_{DM}$                                                                 | All lines open                                                                                                                                                                                                                                                      | 100   |      | 125   | mV    |  |

| Common-Mode Bias                                | V <sub>CM</sub>                                                          | R <sub>P</sub> and R <sub>N</sub> shorted together (Note 1)                                                                                                                                                                                                         | 1.15  | 1.25 | 1.35  | V     |  |

| SE TERMINATION (Applies to sing                 | SE TERMINATION (Applies to single-ended terminators, 1 to 14 in SE mode) |                                                                                                                                                                                                                                                                     |       |      |       |       |  |

| Single-Ended Mode Termination<br>Resistance     | R <sub>SE</sub>                                                          | $\begin{aligned} &R_{SE} = \left(V_{LX} - 0.2\right) / I_{LX}, \text{ where } V_{LX} = \text{voltage} \\ &\text{at terminator pin with pin unloaded and} \\ &I_{LX} = \text{current for each terminator pin with} \\ &\text{the pin forced to } 0.2V \end{aligned}$ | 104.5 | 110  | 115.5 | Ω     |  |

| T                                               | ISE                                                                      | Signal level at 0.2V, all lines low                                                                                                                                                                                                                                 | -21   | -24  | -25.4 | mA    |  |

| Termination Current                             |                                                                          | Signal level at 0.5V                                                                                                                                                                                                                                                | -18   |      | -22.4 |       |  |

| SE Voltage Reference                            | V <sub>REF</sub>                                                         |                                                                                                                                                                                                                                                                     | 2.7   | 2.85 | 3.0   | V     |  |

| Pin Leakage                                     |                                                                          | With ISO high                                                                                                                                                                                                                                                       |       |      | 400   | nA    |  |

| Single-Ended GND Resistance                     | R <sub>GND</sub>                                                         | Measured at R <sub>P</sub> pins, I = 10mA                                                                                                                                                                                                                           |       | 20   | 60    | Ω     |  |

| TERMINATOR PIN CAPACITANC                       | E                                                                        |                                                                                                                                                                                                                                                                     |       |      |       |       |  |

| Terminator Pin Capacitance                      | CIN                                                                      | With ISO high (Note 2)                                                                                                                                                                                                                                              |       |      | 3     | рF    |  |

| V <sub>REF</sub> REGULATOR                      |                                                                          |                                                                                                                                                                                                                                                                     |       |      |       |       |  |

| 1.25V Regulator Output Voltage                  | V <sub>REF_LVD</sub>                                                     | $0.5V \le V_{CM} \le 2.0V$ , $V_{CM}$ applied to all R <sub>P</sub> and R <sub>N</sub> lines simultaneously                                                                                                                                                         | 1.15  | 1.25 | 1.35  | V     |  |

| 1.25V Regulator Short-Circuit<br>Source Current | ISOURCE                                                                  | V <sub>REF</sub> = 0V                                                                                                                                                                                                                                               | -375  | -700 | -1000 | mA    |  |

| 1.25V Regulator Short-Circuit Sink Current      | ISINK                                                                    | V <sub>REF</sub> = 3.3V                                                                                                                                                                                                                                             | 170   | 300  | 700   | mA    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(TPWR =  $V_{TPWR(MIN)}$  to  $V_{TPWR(MAX)}$ ,  $T_A = 0$ °C to +70°C, unless otherwise noted.)

| PARAMETER                                       | SYMBOL                      | CONDITIONS                                             | MIN  | TYP  | MAX      | UNITS |

|-------------------------------------------------|-----------------------------|--------------------------------------------------------|------|------|----------|-------|

| V <sub>REF</sub> REGULATOR                      |                             |                                                        |      |      |          |       |

| 1.25V Regulator Line Regulation                 |                             | V <sub>REF</sub> unloaded; vary TPWR from 2.7V to 5.5V |      | 1.0  | 2.5      | %     |

| 2.85V Regulator                                 |                             |                                                        | 2.7  | 2.85 | 3.0      | V     |

| 2.85V Regulator Short-Circuit<br>Source Current |                             | V <sub>REF</sub> = 0V                                  | -375 | -700 | -1000    | mA    |

| 2.85V Regulator Short-Circuit<br>Sink Current   |                             | V <sub>REF</sub> = 3.3V                                | 170  | 300  | 700      | mA    |

| 2.85V Regulator Line Regulation                 |                             | V <sub>REF</sub> unloaded; vary TPWR from 2.7V to 5.5V |      | 1.0  | 2.5      | %     |

| DIFFSENS OUTPUT                                 | 1                           |                                                        | 1    |      |          |       |

| DIFFSENS Driver Output Voltage                  | V <sub>DSO</sub>            | -5mA ≤ IDIFFSENS ≤ 50μA                                | 1.2  |      | 1.4      | V     |

| DIFFSENS Driver Source Current                  | IDSH                        | V <sub>DIFFSENS</sub> = 0V                             | -15  |      | -5       | mA    |

| DIFFSENS Driver Sink Current                    | I <sub>DSL</sub>            | V <sub>DIFFSENS</sub> = 2.75V                          | 100  |      | 200      | μΑ    |

| DIFFSENS Leakage (Note 3)                       | I <sub>LEAK</sub> ,<br>LOW  | With ISO high, IV <sub>DIFFSENS</sub> I = 0.3V         | -3   |      | +1       | μΑ    |

|                                                 | I <sub>LEAK</sub> ,<br>HIGH | With ISO high, IVDIFFSENS - VTPWRI = 0.3V              | 1    |      | 3        |       |

| THERMAL SHUTDOWN                                | 1                           |                                                        | II.  |      |          |       |

| Thermal-Shutdown Threshold                      |                             | For increasing temperature                             |      | 130  |          | °C    |

| Thermal-Shutdown Hysteresis                     |                             |                                                        |      | 10   |          | °C    |

| MODE CHANGE DELAY/FILTER                        |                             |                                                        |      |      |          |       |

| Mode Change Delay                               | tDELAY                      |                                                        | 0.66 | 1.25 | 2.00     | ms    |

| LOGICAL SIGNALS (ISO)                           |                             |                                                        |      |      |          |       |

| Input Low Voltage                               | VIL                         |                                                        | -0.3 |      | +0.8     | V     |

| Input High Voltage                              | VIH                         |                                                        | 2.0  | TPV  | VR + 0.3 | V     |

| Input Current                                   | I <sub>I</sub> L            | V <sub>CC</sub> = 3.3V                                 | -30  | -10  |          | μΑ    |

| STATUS BITS (LVD, SE)                           |                             |                                                        |      |      |          |       |

| Source Current                                  | Іон                         | $V_{CC} = 3.3V$ , $V_{LOAD} = 2.4V$                    | -4   | -6   |          | mA    |

| Sink Current                                    | loL                         | $V_{CC} = 3.3V$ , $V_{LOAD} = 0.4V$                    | 2    | 5    |          | mA    |

| DIFF_CAP                                        |                             |                                                        |      |      |          |       |

| Input Current                                   | IL                          | V <sub>IL</sub> = -0.3V                                | -1   |      | +1       | μΑ    |

| DIFF_CAP SE Operating Range                     | VSEOR                       |                                                        | -0.3 |      | +0.5     | V     |

| DIFF_CAP LVD Operating Range                    | V <sub>L</sub> VDOR         |                                                        | 0.7  |      | 1.9      | V     |

| DIFF_CAP HVD Operating Range                    | V <sub>H</sub> VDOR         |                                                        | 2.4  | VTP\ | WR + 0.3 | V     |

Note 1: All voltages are referenced to ground.

Note 2: Guaranteed by design and not production tested.

Note 3: Room temperature only.

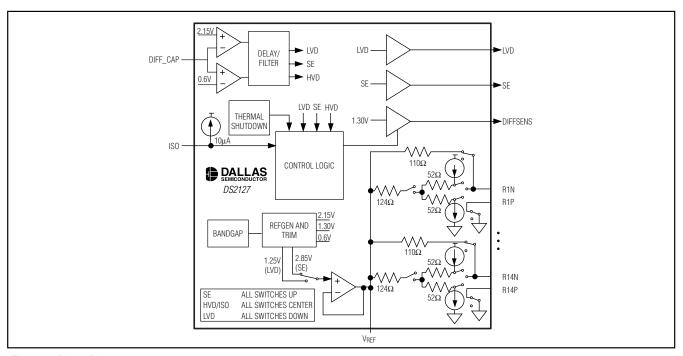

Figure 1. Block Diagram

## **Pin Description**

| PIN                   | NAME                                                                                                                                                         | FUNCTION                                                                                                                                                                                                                                                                                           |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 11–24,<br>37–48 | RP, RN                                                                                                                                                       | Signal Termination. Connect to SCSI bus signal lines. Asserting ISO removes the terminators from the SCSI bus. RP pins are the ground line for SE operation and the positive lines in differential mode. RN pins are the signal lines in SE operation and the negative lines in differential mode. |

| 3                     | TPWR                                                                                                                                                         | Termination Power. Connect to the SCSI TERMPWR line and decouple with a ceramic 2.2µF capacitor.                                                                                                                                                                                                   |

| 4–9, 28–33            | HS_GND                                                                                                                                                       | Heat-Sink Ground. Internally connected to the mounting pad. These pins must be connected to ground. These pins should be connected to a ground plane with the layout optimized for heat transfer.                                                                                                  |

| 10                    | V <sub>REF</sub>                                                                                                                                             | Regulator Output Voltage. This must be decoupled with a 4.7µF capacitor. Asserting ISO floats this output. A high-frequency capacitor (0.1µF) should also be placed on the V <sub>REF</sub> pin in applications that use fast rise/fall-time drivers.                                              |

| 25                    | GND                                                                                                                                                          | Signal Ground                                                                                                                                                                                                                                                                                      |

| 26                    | SE                                                                                                                                                           | SE Mode Indicator. A high state indicates SE mode detected on SCSI bus.                                                                                                                                                                                                                            |

| 27                    | LVD                                                                                                                                                          | LVD Mode Indicator. A high state indicates LVD mode detected on SCSI.                                                                                                                                                                                                                              |

| 34                    | DIFF_CAP DIFFSENSE Capacitor. Connect a 0.1μF capacitor for the DIFFSENSE filter. Input to detect the device (differential or single-ended) on the SCSI bus. |                                                                                                                                                                                                                                                                                                    |

| 35                    | DIFFSENS                                                                                                                                                     | DIFFSENSE. Output to drive the SCSI bus DIFFSENS line.                                                                                                                                                                                                                                             |

| 36                    | ISO                                                                                                                                                          | Isolation Input. When pulled high, terminating resistors and biasing current sources are removed from the SCSI bus. When not connected to ground, the pin has a 10µA current source pulling the pin to the high state.                                                                             |

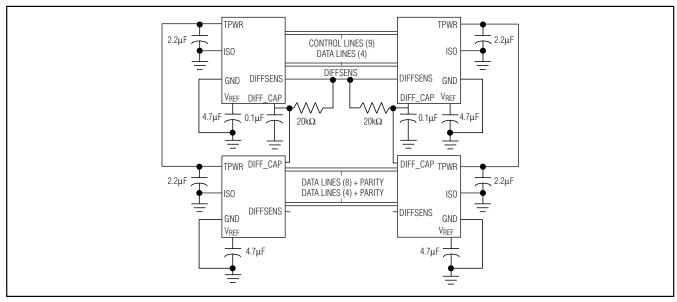

Figure 2. Typical Operating Circuit

## Detailed Description

The DS2127 provides dual-mode active terminators with auto-switching SE and LVD termination for 14 SCSI lines. The DIFFSENSE signal performs mode detection and selection.

In LVD mode, the termination configuration is a y-type terminator with a  $105\Omega$  differential resistance and a  $150\Omega$  common-mode resistance. The termination resistor is biased with two current sources and the common-mode node is connected to a 1.25V voltage regulator. A fail-safe bias of 112mV is maintained when no drivers are connected to the SCSI bus.

In SE mode, each negative signal input pin is connected to 2.85V through a  $110\Omega$  resistor.

In HVD mode, the termination resistors are isolated from the SCSI bus and the resistor pins are left floating. The voltage regulator is powered down and the  $V_{REF}$  pin is in a high-impedance state.

The DIFF\_CAP pin is connected to the SCSI DIFFSENSE line and monitors the voltage to determine the proper operating mode of the device. Any DIFFSENSE voltage below 0.5V indicates single ended; any DIFFSENSE voltage between 0.7V and 1.9V is LVD, and above 2.4V is an HVD SCSI. On power-up, the DS2127 assumes SE mode. If the voltage on the DIFF\_CAP is between 0.7V and 1.9V, the device waits tDELAY before entering the LVD mode. The delay is the same when changing modes. A new mode change can start at any time after a previous mode change has been detected.

Typically, four DS2127s are used in a SCSI bus segment. On two chips, the DIFF\_CAP inputs at each end of the bus should be connected together. There should be a 50Hz noise filter implemented on DIFF\_CAP at each end of the bus, as close as possible to the DIFF\_CAP pins. This filter consists of a  $20k\Omega$  resistor between the DIFFSENS and DIFF\_CAP pins, and a  $0.1\mu\text{F}$  capacitor from DIFF\_CAP to GND. See Figure 2 for the typical operating circuit.

When ISO is connected to TPWR, the termination pins are isolated from the SCSI bus and  $V_{REF}$  becomes inactive, and the device is in a low-power state. During thermal shutdown, the termination pins are isolated from the SCSI bus and  $V_{REF}$  becomes high impedance. The DIFFSENS driver is shut down during either of these two events. LVD and SE signals indicate whether the SCSI bus segment is in LVD or SE mode.

## \_Chip Information

TRANSISTOR COUNT: 8114 CMOS and 87 Bipolar

PROCESS: BICMOS

SUBSTRATE CONNECTED TO GROUND

### Thermal Information

Thermal Resistance (junction-to-ambient):  $\theta_{JA} = +29$ °C/W

Thermal Resistance (junction-to-case):

$\theta_{\text{JC}} = +10^{\circ}\text{C/W}$

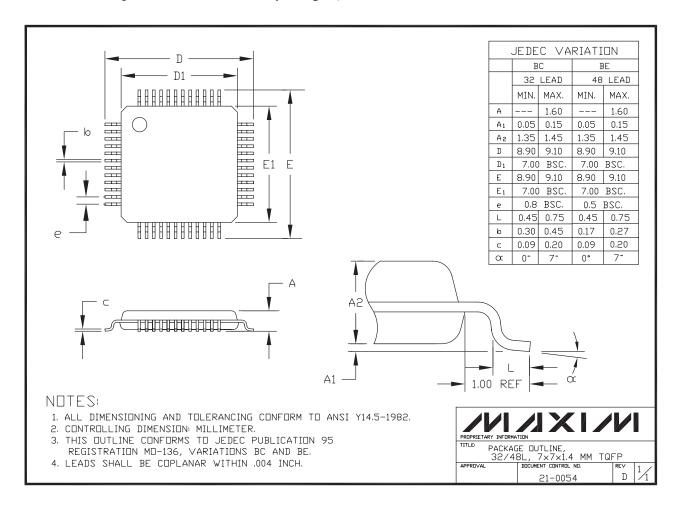

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.