### MSP432P401R, MSP432P401M

SLAS826E -MARCH 2015-REVISED JULY 2016

# MSP432P401R, MSP432P401M Mixed-Signal Microcontrollers

#### 1 Device Overview

**INSTRUMENTS**

# 1.1 Features

**TEXAS**

- · Core

- ARM<sup>®</sup> 32-Bit Cortex<sup>®</sup>-M4F CPU With Floating-Point Unit and Memory Protection Unit

- Frequency up to 48 MHz

- ULPBench™ Benchmark:

- 192.3 ULPMark™-CP

- Performance Benchmark:

- 3.41 CoreMark/MHz

- · 1.22 DMIPS/MHz (Dhrystone 2.1)

- Memories

- Up to 256KB of Flash Main Memory (Organized Into Two Banks Enabling Simultaneous Read/Execute During Erase)

- 16KB of Flash Information Memory (Used for BSL, TLV, and Flash Mailbox)

- Up to 64KB of SRAM (Including 6KB of Backup Memory)

- 32KB of ROM With MSP432<sup>™</sup> Peripheral Driver Libraries

- · Operating Characteristics

- Wide Supply Voltage Range: 1.62 V to 3.7 V

- Temperature Range (Ambient): -40°C to 85°C

- · Ultra-Low-Power Operating Modes

- Active: 80 μA/MHz

- Low-Frequency Active: 83 μA at 128 kHz (Typical)

- LPM3 (With RTC): 660 nA (Typical)

- LPM3.5 (With RTC): 630 nA (Typical)

- LPM4: 500 nA (Typical)

- LPM4.5: 25 nA (Typical)

- Flexible Clocking Features

- Tunable Internal DCO (up to 48 MHz)

- 32.768 kHz Low-Frequency Crystal Support (LFXT)

- High-Frequency Crystal Support (HFXT) up to 48 MHz

- Low-Frequency Internal Reference Oscillator (REFO)

- Very Low-Power Low-Frequency Internal Oscillator (VLO)

- Module Oscillator (MODOSC)

- System Oscillator (SYSOSC)

- · Code Security Features

- JTAG and SWD Lock

- IP Protection (up to Four Secure Flash Zones, Each With Configurable Start Address and Size)

- · Enhanced System Features

- Programmable Supervision and Monitoring of Supply Voltage

Support & Community

- Multiple-Class Resets for Better Control of Application and Debug

- 8-Channel DMA

- RTC With Calendar and Alarm Functions

- · Timing and Control

- Up to Four 16-Bit Timers, Each With up to Five Capture, Compare, PWM Capability

- Two 32-Bit Timers, Each With Interrupt Generation Capability

- · Serial Communication

- Up to Four eUSCI A Modules

- · UART With Automatic Baud-Rate Detection

- IrDA Encode and Decode

- · SPI (up to 16 Mbps)

- Up to Four eUSCI\_B Modules

- I<sup>2</sup>C (With Multiple-Slave Addressing)

- SPI (up to 16 Mbps)

- · Flexible I/O Features

- Ultra-Low-Leakage I/Os (±20 nA Maximum)

- All I/Os With Capacitive-Touch Capability

- Up to 48 I/Os With Interrupt and Wake-up Capability

- Up to 24 I/Os With Port Mapping Capability

- Eight I/Os With Glitch Filtering Capability

- · Advanced Low-Power Analog Features

- 14-Bit 1-MSPS SAR ADC With Differential and Single-Ended Inputs

- Internal Voltage Reference With 10-ppm/°C Typical Stability

- Two Analog Comparators

- Encryption and Data Integrity Accelerators

- 128-, 192-, or 256-Bit AES Encryption and Decryption Accelerator

- 32-Bit Hardware CRC Engine

- · JTAG and Debug Support

- Support for 4-Pin JTAG and 2-Pin SWD Debug Interfaces

- Support for Serial Wire Trace

- Support for Power Debug and Profiling of Applications

#### Texas Instruments

#### 1.2 Applications

- Industrial and Automation

- Home Automation

- Smoke Detectors

- Barcode Scanners

- Access Panels

- Metering

- Electric Meters

- Flow Meters

- Communication Modules

- · Health and Fitness

- Watches

- Activity Monitors

- Fitness Accessories

- Blood Glucose Meters

- · Consumer Electronics

- Mobile Devices

- Sensor Hubs

### 1.3 Description

The MSP432P401x microcontroller (MCU) family is TI's latest addition to its portfolio of efficient ultra-lowpower mixed-signal MCUs. The MSP432P401x MCUs feature the ARM Cortex-M4 processor in a wide configuration of device options including a rich set of analog, timing, and communication peripherals, thereby catering to a large number of application scenarios where both efficient data processing and enhanced low-power operation are paramount.

Overall, the MSP432P401x is an ideal combination of the TI MSP430™ low-power DNA, advance mixedsignal features, and the processing capabilities of the ARM 32-bit Cortex-M4 RISC engine. The devices ship with bundled peripheral driver libraries and are compatible with standard components of the ARM ecosystem.

#### Device Information<sup>(1)</sup>

|                                    | Dovido illiorillation |               |  |  |

|------------------------------------|-----------------------|---------------|--|--|

| PART NUMBER                        | PACKAGE               | BODY SIZE(2)  |  |  |

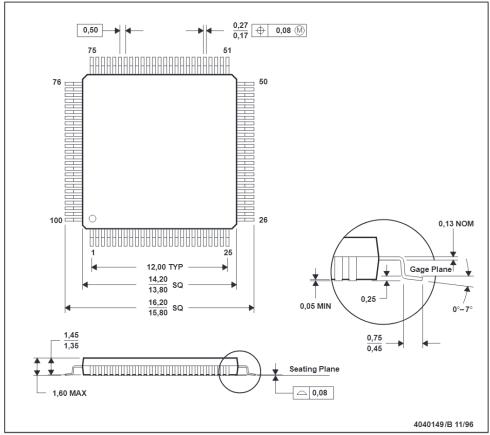

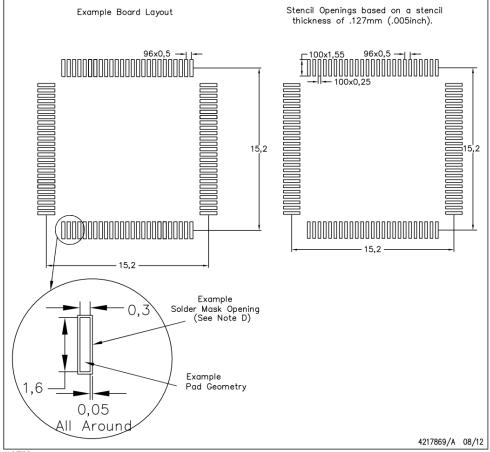

| MSP432P401RIPZ<br>MSP432P401MIPZ   | LQFP (100)            | 14 mm × 14 mm |  |  |

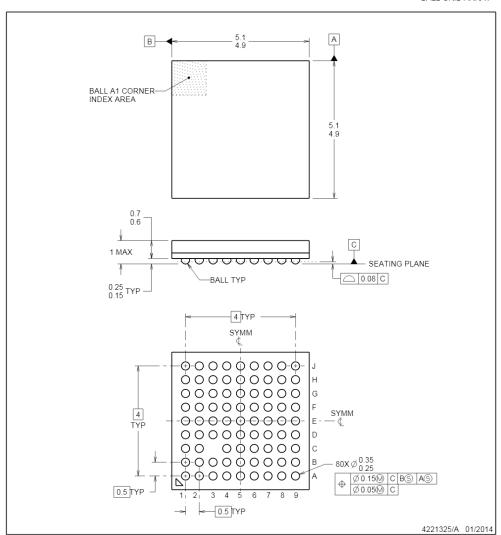

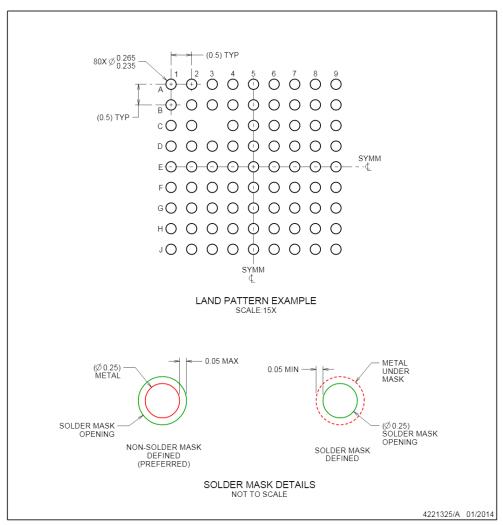

| MSP432P401RIZXH<br>MSP432P401MIZXH | NFBGA (80)            | 5 mm × 5 mm   |  |  |

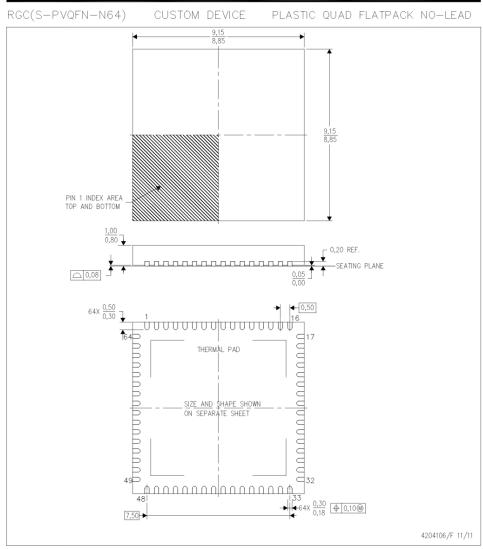

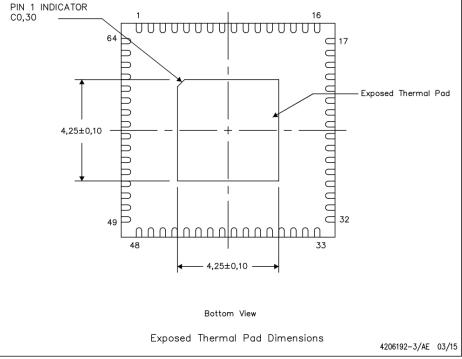

| MSP432P401RIRGC<br>MSP432P401MIRGC | (/OFN (64)            |               |  |  |

For the most current part, package, and ordering information for all available devices, see the *Package Option Addendum* in Section 9, or see the TI website.

The sizes shown here are approximations. For the package dimensions with tolerances, see the

TEXAS

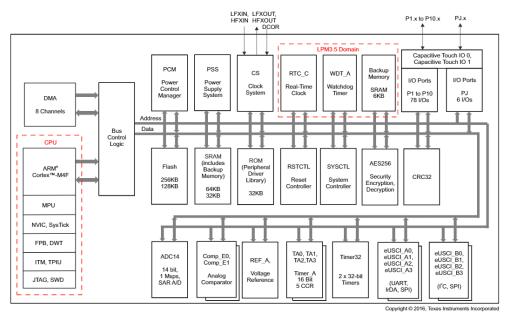

### 1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the MSP432P401R and MSP432P401M devices.

Figure 1-1. MSP432P401R, MSP432P401M Functional Block Diagram

The CPU and all of the peripherals in the device interact with each other through a common AHB matrix. In some cases, there are bridges between the AHB ports and the peripherals. These bridges are transparent to the application from a memory map perspective and, therefore, are not shown in the block diagram.

### **Table of Contents**

| 1 | Devi | ce Overview                                                           | <u>1</u>  |   | 5.19  | Current Consumption in DC-DC-Based LPM0              |            |

|---|------|-----------------------------------------------------------------------|-----------|---|-------|------------------------------------------------------|------------|

|   | 1.1  | Features                                                              | <u> 1</u> |   |       | Modes                                                | . 38       |

|   | 1.2  | Applications                                                          | <u>2</u>  |   | 5.20  | Current Consumption in Low-Frequency LPM0 Modes      | . 38       |

|   | 1.3  | Description                                                           | <u>2</u>  |   | 5.21  | Current Consumption in LPM3, LPM4 Modes              |            |

|   | 1.4  | Functional Block Diagram                                              | <u>3</u>  |   | 5.22  | •                                                    |            |

| 2 | Revi | sion History                                                          | 5         |   | 5.22  | Current Consumption of Digital Parisherals           |            |

| 3 | Devi | ce Comparison                                                         | 6         |   | 5.24  | Current Consumption of Digital Peripherals           | _          |

|   | 3.1  | Related Products                                                      | . 7       |   |       | Thermal Resistance Characteristics                   |            |

| 4 | Term | inal Configuration and Functions                                      | . 8       | 6 | 5.25  | Timing and Switching Characteristicsiled Description |            |

|   | 4.1  | Pin Diagrams                                                          | . 8       | U | 6.1   | Overview                                             |            |

|   | 4.2  | Pin Attributes                                                        | <u>11</u> |   | 6.2   | Processor and Execution Features                     |            |

|   | 4.3  | Signal Descriptions                                                   | <u>17</u> |   | 6.3   | Memory Map                                           |            |

|   | 4.4  | Pin Multiplexing                                                      | <u>27</u> |   | 6.4   | Memories on the MSP432P401x                          |            |

|   | 4.5  | Buffer Types                                                          | <u>27</u> |   | 6.5   | DMA                                                  | 114        |

|   | 4.6  | Connection for Unused Pins                                            | 27        |   | 6.6   | Memory Map Access Details                            |            |

| 5 | Spec | cifications                                                           | 28        |   | 6.7   | Interrupts                                           |            |

|   | 5.1  | Absolute Maximum Ratings                                              | 28        |   | 6.8   | System Control.                                      |            |

|   | 5.2  | ESD Ratings                                                           | 28        |   | 6.9   | Peripherals                                          |            |

|   | 5.3  | Recommended Operating Conditions                                      | <u>28</u> |   | 6.10  | Code Development and Debug                           |            |

|   | 5.4  | Recommended External Components                                       | <u>29</u> |   | 6.11  | Performance Benchmarks                               |            |

|   | 5.5  | Operating Mode V <sub>CC</sub> Ranges                                 | <u>29</u> |   | 6.12  | Input/Output Diagrams                                |            |

|   | 5.6  | Operating Mode CPU Frequency Ranges                                   | 30        |   | 6.13  | Device Descriptors (TLV)                             |            |

|   | 5.7  | Operating Mode Peripheral Frequency Ranges                            | 30        |   | 6.14  | Identification.                                      | 178        |

|   | 5.8  | Operating Mode Execution Frequency vs Flash                           |           | 7 |       | ications, Implementation, and Layout                 |            |

|   |      | Wait-State Requirements                                               | _         | • | 7.1   | Device Connection and Layout Fundamentals            |            |

|   | 5.9  | Current Consumption During Device Reset                               | <u>31</u> |   | 7.2   | Peripheral and Interface-Specific Design             | 100        |

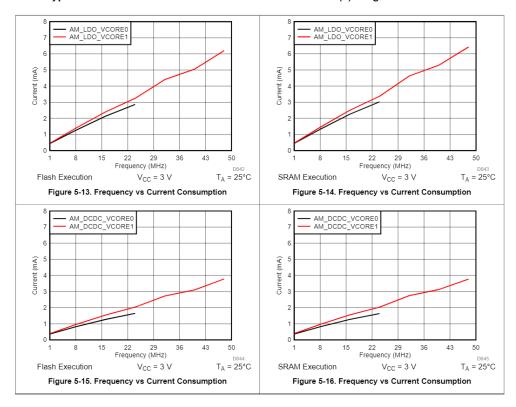

|   | 5.10 | Current Consumption in LDO-Based Active Modes – Dhrystone 2.1 Program | 31        |   |       | Information                                          | 181        |

|   | 5.11 | Current Consumption in DC-DC-Based Active                             | <u>51</u> | 8 | Devi  | ce and Documentation Support                         | 183        |

|   | 0    | Modes – Dhrystone 2.1 Program                                         | 32        |   | 8.1   | Getting Started and Next Steps                       | 183        |

|   | 5.12 | Current Consumption in Low-Frequency Active                           |           |   | 8.2   | Device and Development Tool Nomenclature             | 183        |

|   |      | Modes – Dhrystone 2.1 Program                                         | 32        |   | 8.3   | Tools and Software                                   | 185        |

|   | 5.13 | Typical Characteristics of Active Mode Currents for                   |           |   | 8.4   | Documentation Support                                | 187        |

|   | E 11 | CoreMark Program                                                      | <u>33</u> |   | 8.5   | Related Links                                        | 188        |

|   | 5.14 | Prime Number Program                                                  | 34        |   | 8.6   | Community Resources                                  | 188        |

|   | 5.15 | Typical Characteristics of Active Mode Currents for                   | _         |   | 8.7   | Trademarks                                           | 188        |

|   |      | Fibonacci Program                                                     | 35        |   | 8.8   | Electrostatic Discharge Caution                      | 189        |

|   | 5.16 | Typical Characteristics of Active Mode Currents for                   |           |   | 8.9   | Export Control Notice                                | 189        |

|   |      | While(1) Program                                                      | <u>36</u> |   | 8.10  | Glossary                                             | 189        |

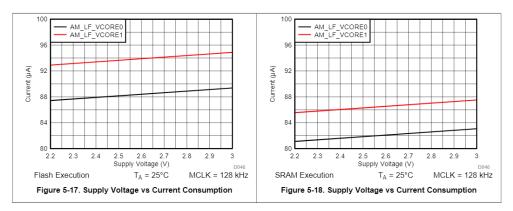

|   | 5.17 | Typical Characteristics of Low-Frequency Active                       | 37        | 9 | Mech  | nanical, Packaging, and Orderable                    |            |

|   | E 10 | Mode Currents for CoreMark Program                                    |           |   | Infor | mation                                               | <u>190</u> |

|   | 3.18 | Current Consumption in LDO-Based LPM0 Modes.                          | 38        |   |       |                                                      |            |

# MSP432P401R, MSP432P401M

SLAS826E - MARCH 2015-REVISED JULY 2016

#### www.ti.com

### 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Chang | ges from June 28, 2016 to July 25, 2016                                                                                                                     | Page      |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| :     | Corrected C0.7 signal type (changed I/O to I) in Table 4-1, Pin Attributes  Corrected C0.7 signal type (changed I/O to I) in Table 4-2, Signal Descriptions | <u>18</u> |

|       | fields to Reserved in Table 6-86, Device Descriptor Table  Added Section 6.14.1, Revision Identification                                                    | . 178     |

TEXAS INSTRUMENTS

### 3 Device Comparison

Table 3-1 summarizes the features of the MSP432P401x microcontrollers.

#### Table 3-1. Device Comparison<sup>(1)</sup>

|                 |               |              |                     |                       | eUSCI                 |                        |                                     |                                        |                    |               |         |

|-----------------|---------------|--------------|---------------------|-----------------------|-----------------------|------------------------|-------------------------------------|----------------------------------------|--------------------|---------------|---------|

| DEVICE          | FLASH<br>(KB) | SRAM<br>(KB) | ADC14<br>(Channels) | COMP_E0<br>(Channels) | COMP_E1<br>(Channels) | Timer_A <sup>(2)</sup> | CHANNEL<br>A:<br>UART,<br>IrDA, SPI | CHANNEL<br>B:<br>SPI, I <sup>2</sup> C | 20-mA<br>DRIVE I/O | TOTAL<br>I/Os | PACKAGE |

| MSP432P401RIPZ  | 256           | 64           | 24 ext, 2 int       | 8                     | 8                     | 5, 5, 5, 5             | 4                                   | 4                                      | 4                  | 84            | 100 PZ  |

| MSP432P401MIPZ  | 128           | 32           | 24 ext, 2 int       | 8                     | 8                     | 5, 5, 5, 5             | 4                                   | 4                                      | 4                  | 84            | 100 PZ  |

| MSP432P401RIZXH | 256           | 64           | 16 ext, 2 int       | 6                     | 8                     | 5, 5, 5                | 3                                   | 4                                      | 4                  | 64            | 80 ZXH  |

| MSP432P401MIZXH | 128           | 32           | 16 ext, 2 int       | 6                     | 8                     | 5, 5, 5                | 3                                   | 4                                      | 4                  | 64            | 80 ZXH  |

| MSP432P401RIRGC | 256           | 64           | 12 ext, 2 int       | 2                     | 4                     | 5, 5, 5                | 3                                   | 3                                      | 4                  | 48            | 64 RGC  |

| MSP432P401MIRGC | 128           | 32           | 12 ext, 2 int       | 2                     | 4                     | 5, 5, 5                | 3                                   | 3                                      | 4                  | 48            | 64 RGC  |

For the most current part, package, and ordering information for all available devices, see the Package Option Addendum in Section 9, or see the TI website at www.ti.com.

Each number in the sequence represents an instantiation of Timer\_A with its associated number of capture/compare registers and PWM output generators available. For example, a number sequence of 3, 5 would represent two instantiations of Timer\_A, the first instantiation having 3 and the second instantiation having 5 capture/compare registers and PWM output generators, respectively.

#### www.ti.com

#### 3.1 Related Products

For information about other devices in this family of products or related products, see the following links.

- Products for MSP 16-Bit and 32-Bit MCUs Low-power mixed-signal processors with smart analog and digital peripherals for a wide range of industrial and consumer applications.

- Products for MSP432 Low Power + Performance MCUs MSP low power and performance microcontrollers from TI provide designers with increased processing capability, smart analog, advanced security, and display and communication peripherals while using less watts than ever before for the development of "always on" embedded applications.

- Companion Products for MSP432P401R Review products that are frequently purchased or used with this product.

- Reference Designs for MSP432P401R The TI Designs Reference Design Library is a robust reference design library that spans analog, embedded processor, and connectivity. Created by TI experts to help you jump start your system design, all TI Designs include schematic or block diagrams, BOMs, and design files to speed your time to market. Search and download designs at ti.com/tidesigns.

#### 4 Terminal Configuration and Functions

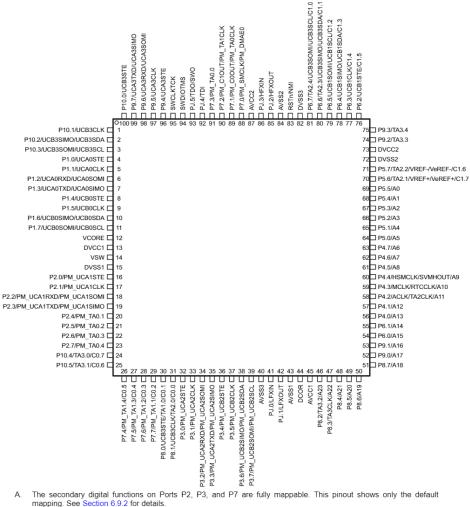

#### 4.1 Pin Diagrams

Figure 4-1 shows the pinout of the 100-pin PZ package.

- The secondary digital functions on Ports P2, P3, and P7 are fully mappable. This pinout shows only the default mapping. See Section 6.9.2 for details

- A glitch filter is implemented on these digital I/Os: P1.0, P1.4, P1.5, P3.0, P3.4, P3.5, P6.6, P6.7.

- UART BSL pins: P1.2 BSLRXD, P1.3 BSLTXD

- SPI BSL pins: P1.4 BSLSTE, P1.5 BSLCLK, P1.6 BSLSIMO, P1.7 BSLSOMI D

- I2C BSL pins: P3.6 BSLSDA, P3.7 BSLSCL

Figure 4-1. 100-Pin PZ Package (Top View)

Copyright © 2015-2016, Texas Instruments Incorporated

Figure 4-2 shows the pinout of the 80-pin ZXH package.

| P1.0 SWCLKTCK PJ.               |      | PJ.3         | PJ.2         | P6.5         | P6.4         | P6.2         |

|---------------------------------|------|--------------|--------------|--------------|--------------|--------------|

| P1.1 SWDIOTMS PJ.               | _    | P7.0         | RSTn/NN      | P6.7         | P6.6         | P6.3         |

| P1.5 VCORE                      | P1.2 | P7.1<br>(C5) | DVCC2        | DVSS3        | P5.5         | P5.7         |

| P1.6 DVCC1 P1.4                 |      | AVCC2        | AVSS2        | P5.3         | P5.4         | P5.6         |

| P1.7 VSW P2.2                   |      | AVSS3        | DVSS2        | P5.0         | P5.1         | P5.2<br>(E9) |

| P2.1 DVSS1 P2.4                 | P2.3 | AVSS1        | AVCC1        | P4.5         | P4.6         | P4.7         |

| P2.5 P2.6 P7.7                  | P8.1 | P3.2<br>(G5) | P3.5<br>(G6) | P4.2         | P4.3<br>(G8) | P4.4<br>(G9) |

| P2.7 P7.5 P8.0                  |      | P3.4<br>(H5) | P3.7         | P6.1         | P4.1<br>(H8) | P4.0         |

| P7.4 P7.6 P3.0<br>(J1) (J2) (J3 | P3.3 | P3.6         | PJ.0<br>(J6) | PJ.1<br>(J7) | DCOR<br>(J8) | P6.0         |

A. A glitch filter is implemented on these digital I/Os: P1.0, P1.4, P1.5, P3.0, P3.4, P3.5, P6.6, P6.7.

B. UART BSL pins: P1.2 - BSLRXD, P1.3 - BSLTXD

Figure 4-2. 80-Pin ZXH Package (Top View)

C. SPI BSL pins: P1.4 - BSLSTE, P1.5 - BSLCLK, P1.6 - BSLSIMO, P1.7 - BSLSOMI

D. I<sup>2</sup>C BSL pins: P3.6 - BSLSDA, P3.7 - BSLSCL

Figure 4-3 shows the pinout of the 64-pin RGC package.

- The secondary digital functions on Ports P2, P3, and P7 are fully mappable. This pinout shows only the default mapping. See Section 6.9.2 for details

- A glitch filter is implemented on these digital I/Os: P1.0, P1.4, P1.5, P3.0, P3.4, P3.5, P6.6, P6.7. В.

- TI recommends connecting the thermal pad on the QFN package to DVSS. C

- UART BSL pins: P1.2 BSLRXD, P1.3 BSLTXD D

- SPI BSL pins: P1.4 BSLSTE, P1.5 BSLCLK, P1.6 BSLSIMO, P1.7 BSLSOMI

- I<sup>2</sup>C BSL pins: P3.6 BSLSDA, P3.7 BSLSCL

Figure 4-3. 64-Pin RGC Package (Top View)

#### 4.2 Pin Attributes

Table 4-1 describes the attributes of the pins.

Table 4-1. Pin Attributes

|    | PIN NO. <sup>(1)</sup> |           | (3)                            | SIGNAL              |                            | POWER                 | RESET                            |     |

|----|------------------------|-----------|--------------------------------|---------------------|----------------------------|-----------------------|----------------------------------|-----|

| PZ | ZXH                    | RGC       | SIGNAL NAME <sup>(2)</sup> (3) | TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7</sup> |     |

| 1  | N/A                    | N/A       | P10.1 (RD)                     | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 1  | N/A                    | N/A       | UCB3CLK                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | P10.2 (RD)                     | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 2  | N/A                    | N/A       | UCB3SIMO                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCB3SDA                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | P10.3 (RD)                     | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 3  | N/A                    | N/A       | UCB3SOMI                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCB3SCL                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    | P1.0 (F                | P1.0 (RD) | I/O                            | LVCMOS              | DVCC                       | OFF                   |                                  |     |

| 4  | A1                     | 1         | UCA0STE                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

| -  | 5 54                   |           |                                | P1.1 (RD)           | I/O                        | LVCMOS                | DVCC                             | OFF |

| 5  | B1                     | 2         | UCA0CLK                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | P1.2 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 6  | 6 C4                   | 3         | UCA0RXD                        | I                   | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCA0SOMI                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    | D4                     |           | P1.3 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 7  |                        | 4         | UCA0TXD                        | 0                   | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCA0SIMO                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

| _  | D0                     | _         | P1.4 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 8  | D3                     | 5         | UCB0STE                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

| _  | 0.4                    |           | P1.5 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 9  | C1                     | 6         | UCB0CLK                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | P1.6 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 10 | D1                     | 7         | UCB0SIMO                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCB0SDA                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | P1.7 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 11 | E1                     | 8         | UCB0SOMI                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

|    |                        |           | UCB0SCL                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

| 12 | C2                     | 9         | VCORE                          | _                   | Power                      | DVCC                  | N/A                              |     |

| 13 | D2                     | 10        | DVCC1                          | _                   | Power                      | N/A                   | N/A                              |     |

| 14 | E2                     | 11        | VSW                            | _                   | Power                      | N/A                   | N/A                              |     |

| 15 | F2                     | 12        | DVSS1                          | -                   | Power                      | N/A                   | N/A                              |     |

| 40 | F.4                    | 10        | P2.0 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |     |

| 16 | E4                     | 13        | PM UCA1STE                     | I/O                 | LVCMOS                     | DVCC                  | N/A                              |     |

- N/A = not available on this package

(RD) indicates the reset default signal name for that pin.

To determine the pin mux encodings for each pin, see Section 6.12, Input/Output Diagrams.

Signal Types: I = Input, O = Output, I/O = Input or Output, P = power

Buffer Types: see Table 4-3 for details

The power source shown in this table is the I/O power source, which may differ from the module power source.

Reset States:

OFF = High-impedance with Schmitt trigger and pullup or pulldown (if available) disabled

PD = High-impedance input with pulldown enabled

PU = High-impedance input with pullup enabled

N/A = Not applicable

Product Folder Links: MSP432P401R MSP432P401M

Table 4-1. Pin Attributes (continued)

|     | PIN NO. (1) |         |                                |                               |                            |                                | RESET                             |       |     |        |      |     |

|-----|-------------|---------|--------------------------------|-------------------------------|----------------------------|--------------------------------|-----------------------------------|-------|-----|--------|------|-----|

| PZ  | ZXH         | RGC     | SIGNAL NAME <sup>(2) (3)</sup> | SIGNAL<br>TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | POWER<br>SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7)</sup> |       |     |        |      |     |

| 47  | F1          | 14      | P2.1 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 17  | FI          | 14      | PM_UCA1CLK                     | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P2.2 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 18  | E3          | 15      | PM_UCA1RXD                     | I                             | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | PM_UCA1SOMI                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P2.3 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 19  | F4          | 16      | PM_UCA1TXD                     | 0                             | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | PM_UCA1SIMO                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 00  |             |         | P2.4 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 20  | F3          | N/A     | PM_TA0.1                       | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 0.4 |             |         | P2.5 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 21  | G1          | N/A     | PM_TA0.2                       | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P2.6 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 22  | G2          | N/A     | PM_TA0.3                       | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P2.7 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 23  | H1          | N/A     | PM TA0.4                       | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P10.4 (RD)                     | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 24  | 24 N/A      | N/A     | N/A                            | 4 N/A                         | N/A                        | N/A                            | N/A                               | TA3.0 | I/O | LVCMOS | DVCC | N/A |

|     |             | 1471    | C0.7                           | ı                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P10.5 (RD)                     | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 25  | N/A         | N/A N/A | TA3.1                          | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | C0.6                           | 1                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             | J1 N/A  | P7.4 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 26  | .11         |         | PM_TA1.4                       | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 20  |             |         | C0.5                           | ı                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P7.5 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 27  | H2          | N/A     | PM_TA1.3                       | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 21  | 112         | 1471    | C0.4                           | 1                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P7.6 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 28  | J2          | N/A     | PM_TA1.2                       | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 20  | 02          | 19/73   | C0.3                           | I                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P7.7 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

| 29  | G3          | N/A     | PM_TA1.1                       | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 20  | 00          | 14//    | C0.2                           | 1                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P8.0 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

|     |             |         | UCB3STE                        | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 30  | H3          | 17      | TA1.0                          | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | C0.1                           | 1/0                           | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

|     |             |         | P8.1 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

|     |             |         | UCB3CLK                        | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 31  | G4          | 18      | TA2.0                          | 1/0                           | LVCMOS                     | DVCC                           | N/A<br>N/A                        |       |     |        |      |     |

|     |             |         |                                |                               |                            |                                |                                   |       |     |        |      |     |

|     |             |         | C0.0                           | 1                             | Analog                     | DVCC                           | N/A                               |       |     |        |      |     |

| 32  | J3          | 19      | P3.0 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

|     |             |         | PM_UCA2STE                     | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

| 33  | H4          | 20      | P3.1 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |       |     |        |      |     |

|     |             |         | PM_UCA2CLK                     | I/O                           | LVCMOS                     | DVCC                           | N/A                               |       |     |        |      |     |

Terminal Configuration and Functions

Copyright © 2015–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: MSP432P401R MSP432P401M

Table 4-1. Pin Attributes (continued)

|     | PIN NO. (1) |      |                                | alona:                        |                            | DOMES                          | RESET                             |      |     |

|-----|-------------|------|--------------------------------|-------------------------------|----------------------------|--------------------------------|-----------------------------------|------|-----|

| PZ  | ZXH         | RGC  | SIGNAL NAME <sup>(2) (3)</sup> | SIGNAL<br>TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | POWER<br>SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7)</sup> |      |     |

|     |             |      | P3.2 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 34  | G5          | 21   | PM_UCA2RXD                     | I                             | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | PM_UCA2SOMI                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | P3.3 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 35  | J4          | 22   | PM_UCA2TXD                     | 0                             | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | PM_UCA2SIMO                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             | - 00 | P3.4 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 36  | H5          | 23   | PM_UCB2STE                     | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

| 0.7 |             | 0.4  | P3.5 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 37  | G6          | 24   | PM_UCB2CLK                     | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | P3.6 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 38  | J5          | 25   | PM UCB2SIMO                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | PM UCB2SDA                     | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | P3.7 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 39  | Н6          | 26   | PM UCB2SOMI                    | I/O                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

|     |             |      | PM UCB2SCL                     | ı                             | LVCMOS                     | DVCC                           | N/A                               |      |     |

| 40  | E5          | 27   | AVSS3                          | _                             | Power                      | N/A                            | N/A                               |      |     |

|     |             |      | PJ.0 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 41  | J6          | 28   | LFXIN                          | I                             | Analog                     | DVCC                           | N/A                               |      |     |

|     |             |      | PJ.1 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 42  | J7          | 29   | LFXOUT                         | 0                             | Analog                     | DVCC                           | N/A                               |      |     |

| 43  | F5          | 30   | AVSS1                          | _                             | Power                      | N/A                            | N/A                               |      |     |

| 44  | J8          | 31   | DCOR                           | _                             | Analog                     | N/A                            | N/A                               |      |     |

| 45  | F6          | 32   | AVCC1                          | _                             | Power                      | N/A                            | N/A                               |      |     |

| 43  | 10          | 32   | P8.2 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 46  | N/A         | N/A  | TA3.2                          | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

| 40  | N/A         | IN/A | N/A                            | IN/A                          | A23                        | 1/0                            | Analog                            | DVCC | N/A |

|     |             |      | P8.3 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 47  | N/A         | N/A  | TA3CLK                         | 1/0                           | LVCMOS                     | DVCC                           | N/A                               |      |     |

| 41  | IN/A        | IN/A | A22                            |                               | Analog                     | DVCC                           | N/A                               |      |     |

|     |             |      |                                | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 48  | N/A         | N/A  | P8.4 (RD)                      |                               |                            |                                |                                   |      |     |

|     |             |      | A21                            | 1                             | Analog                     | DVCC                           | N/A                               |      |     |

| 49  | N/A         | N/A  | P8.5 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

|     |             |      | A20                            | 1                             | Analog                     | DVCC                           | N/A                               |      |     |

| 50  | N/A         | N/A  | P8.6 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

|     |             |      | A19                            | I                             | Analog                     | DVCC                           | N/A                               |      |     |

| 51  | N/A         | N/A  | P8.7 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

|     |             |      | A18                            | I                             | Analog                     | DVCC                           | N/A                               |      |     |

| 52  | N/A         | N/A  | P9.0 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

|     |             | 1    | A17                            | 1                             | Analog                     | DVCC                           | N/A                               |      |     |

| 53  | N/A         | N/A  | P9.1 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

|     |             |      | A16                            | I                             | Analog                     | DVCC                           | N/A                               |      |     |

| 54  | J9          | N/A  | P6.0 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 01  | 54 J9 N/A   |      | A15                            | I                             | Analog                     | DVCC                           | N/A                               |      |     |

| 55  | H7          | N/A  | P6.1 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                               |      |     |

| 55  | '''         | 14// | A14                            | 1                             | Analog                     | DVCC                           | N/A                               |      |     |

Copyright © 2015–2016, Texas Instruments Incorporated

Terminal Configuration and Functions

Table 4-1. Pin Attributes (continued)

|    | PIN NO. <sup>(1)</sup> |      |                                | OLC VIA                       |                            | DOMES                          | RESET                            |     |        |      |

|----|------------------------|------|--------------------------------|-------------------------------|----------------------------|--------------------------------|----------------------------------|-----|--------|------|

| PZ | ZXH                    | RGC  | SIGNAL NAME <sup>(2)</sup> (3) | SIGNAL<br>TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | POWER<br>SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7</sup> |     |        |      |

| 56 | H9                     | N/A  | P4.0 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 36 | ПЭ                     | IN/A | A13                            | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

| 67 | 110                    | N/A  | P4.1 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 57 | H8                     | N/A  | A12                            | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P4.2 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 50 | 0.7                    | 22   | ACLK                           | 0                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

| 58 | G7                     | 33   | TA2CLK                         | I                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | A11                            | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P4.3 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 50 | 9 G8                   | 24   | MCLK                           | 0                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

| 59 |                        | 34   | RTCCLK                         | 0                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | A10                            | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P4.4 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

|    | -00                    |      | HSMCLK                         | 0                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

| 60 | G9                     | 35   | SVMHOUT                        | 0                             | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      |                                | A9                            | 1                          | Analog                         | DVCC                             | N/A |        |      |

|    | 61 F7                  |      | P4.5 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 61 | F7                     | 36   | A8                             | ı                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P4.6 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 62 | F8                     | 37   | A7                             | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    | 3 F9 38                |      | P4.7 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 63 |                        | 38   | A6                             | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    | E7                     |      | P5.0 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 64 |                        | 39   | A5                             | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      |                                |                               |                            |                                | P5.1 (RD)                        | 1/0 | LVCMOS | DVCC |

| 65 | E8                     | 40   | A4                             | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.2 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 66 | E9                     | 41   | A3                             | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.3 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 67 | D7                     | 42   | A2                             | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.4 (RD)                      | I/O                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 68 | D8                     | 43   | A1                             | 1/0                           | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.5 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 69 | C8                     | 44   | A0                             | 1/0                           | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.6 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

|    |                        |      | TA2.1                          | 1/0                           | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

| 70 | D9                     | 45   | VREF+                          | 0                             |                            | DVCC                           | N/A                              |     |        |      |

| 70 | Da                     | 45   |                                |                               | Analog                     |                                | _                                |     |        |      |

|    |                        |      | VeREF+                         | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | C1.7                           | 1                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | P5.7 (RD)                      | 1/0                           | LVCMOS                     | DVCC                           | OFF                              |     |        |      |

| 7. |                        |      | TA2.2                          | 1/0                           | LVCMOS                     | DVCC                           | N/A                              |     |        |      |

| 71 | C9                     | 46   | VREF-                          | 0                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | VeREF-                         | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

|    |                        |      | C1.6                           | I                             | Analog                     | DVCC                           | N/A                              |     |        |      |

| 72 | E6                     | 47   | DVSS2                          | -                             | Power                      | N/A                            | N/A                              |     |        |      |

| 73 | C6                     | 48   | DVCC2                          | -                             | Power                      | N/A                            | N/A                              |     |        |      |

Terminal Configuration and Functions

Copyright © 2015–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: MSP432P401R MSP432P401M

Table 4-1. Pin Attributes (continued)

|     | PIN NO.(1) |          | (0) (5)                        | SIGNAL              |                            | POWER                 | RESET                            |        |      |     |

|-----|------------|----------|--------------------------------|---------------------|----------------------------|-----------------------|----------------------------------|--------|------|-----|

| PZ  | ZXH        | RGC      | SIGNAL NAME <sup>(2) (3)</sup> | TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7</sup> |        |      |     |

| 74  | N/A        | N/A      | P9.2 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 14  | N/A        | IN/A     | TA3.3                          | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 7.5 | N1/A       | N1/A     | P9.3 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 75  | N/A        | N/A      | TA3.4                          | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | P6.2 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 76  | A9         | N/A      | UCB1STE                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | C1.5                           | I                   | Analog                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | P6.3 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 77  | В9         | N/A      | UCB1CLK                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | C1.4                           | 1                   | Analog                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | P6.4 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     | 3 A8       |          | UCB1SIMO                       | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 78  |            | N/A      | UCB1SDA                        | I/O                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            | C1.3     | 1                              | Analog              | DVCC                       | N/A                   |                                  |        |      |     |

|     |            |          | P6.5 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     |            |          | 47                             |                     | UCB1SOMI                   | I/O                   | LVCMOS                           | DVCC   | N/A  |     |

| 79  | A7         | A7 N/A   | UCB1SCL                        | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            | C1.2     | I                              | Analog              | DVCC                       | N/A                   |                                  |        |      |     |

|     |            |          | P6.6 (RD)                      | 1/0                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     |            | TA2.3    | 1/0                            | LVCMOS              | DVCC                       | N/A                   |                                  |        |      |     |

| 80  | B8         | 49       | UCB3SIMO                       | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 00  |            | 10       | UCB3SDA                        | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | C1.1                           | 1/0                 | Analog                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | P6.7 (RD)                      | 1/0                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     |            | 7 50     | TA2.4                          | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 81  | B7         |          | UCB3SOMI                       | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 01  | D/         | 30       | UCB3SCL                        | 1/0                 | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | C1.0                           | 1/0                 |                            | DVCC                  | N/A                              |        |      |     |

| 82  | C7         | 51       |                                |                     | Analog                     |                       |                                  |        |      |     |

| 02  | C/         | 31       | DVSS3                          |                     | Power                      | N/A                   | N/A                              |        |      |     |

| 83  | B6         | 52       | RSTn (RD)                      | I                   | LVCMOS                     | DVCC                  | PU                               |        |      |     |

| 0.4 | D0         |          | NMI                            | I                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

| 84  | D6         | 53       | AVSS2                          | -                   | Power                      | N/A                   | N/A                              |        |      |     |

| 85  | A6         | 54       | PJ.2 (RD)                      | 1/0                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     |            |          | HFXOUT                         | 0                   | Analog                     | DVCC                  | N/A                              |        |      |     |

| 86  | A5         | 55       | PJ.3 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

|     |            |          | HFXIN                          | I                   | Analog                     | DVCC                  | N/A                              |        |      |     |

| 87  | D5         | 56       | AVCC2                          | -                   | Power                      | N/A                   | N/A                              |        |      |     |

|     |            |          | P7.0 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 88  | B5         | 57       | PM_SMCLK                       | 0                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | PM_DMAE0                       | 1                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            | P7.1 (RD | P7.1 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 89  | C5         | 58       | PM_C0OUT                       | 0                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | PM_TA0CLK                      | I                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            |          | P7.2 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                              |        |      |     |

| 90  | B4         | 59       | PM_C1OUT                       | 0                   | LVCMOS                     | DVCC                  | N/A                              |        |      |     |

|     |            | 04       |                                | D4                  |                            | PM_TA1CLK             | 1                                | LVCMOS | DVCC | N/A |

Copyright © 2015–2016, Texas Instruments Incorporated

Terminal Configuration and Functions

### Table 4-1. Pin Attributes (continued)

|     | PIN NO. <sup>(1)</sup> |      | (2) (2)                        | SIGNAL              | (5)                        | POWER                 | RESET                             |     |

|-----|------------------------|------|--------------------------------|---------------------|----------------------------|-----------------------|-----------------------------------|-----|

| PZ  | ZXH                    | RGC  | SIGNAL NAME <sup>(2) (3)</sup> | TYPE <sup>(4)</sup> | BUFFER TYPE <sup>(5)</sup> | SOURCE <sup>(6)</sup> | STATE<br>AFTER POR <sup>(7)</sup> |     |

| 91  | A4                     | 60   | P7.3 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

| 91  | A4                     | 00   | PM_TA0.0                       | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

| 92  | В3                     | 61   | PJ.4                           | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

| 92  | БЭ                     | 01   | TDI (RD)                       | I                   | LVCMOS                     | DVCC                  | PU                                |     |

|     |                        |      |                                | PJ.5                | I/O                        | LVCMOS                | DVCC                              | N/A |

| 93  | A3                     | 62   | TDO (RD)                       | 0                   | LVCMOS                     | DVCC                  | N/A                               |     |

|     |                        |      | SWO                            | 0                   | LVCMOS                     | DVCC                  | N/A                               |     |

| 94  | B2                     | 63   | SWDIOTMS                       | I/O                 | LVCMOS                     | DVCC                  | PU                                |     |

| 95  | A2                     | 64   | SWCLKTCK                       | I                   | LVCMOS                     | DVCC                  | PD                                |     |

| 96  | NI/A                   | NI/A | P9.4 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

| 96  | N/A                    | N/A  | UCA3STE                        | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

| 97  |                        | N/A  | P9.5 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

| 91  | N/A                    | IN/A | UCA3CLK                        | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

|     |                        |      | P9.6 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

| 98  | N/A                    | N/A  | UCA3RXD                        | I                   | LVCMOS                     | DVCC                  | N/A                               |     |

|     |                        |      | UCA3SOMI                       | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

|     |                        |      | P9.7 (RD)                      | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

| 99  | N/A                    | N/A  | UCA3TXD                        | 0                   | LVCMOS                     | DVCC                  | N/A                               |     |

|     |                        |      | UCA3SIMO                       | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |

| 100 | NI/A                   | NI/A | P10.0 (RD)                     | I/O                 | LVCMOS                     | DVCC                  | OFF                               |     |

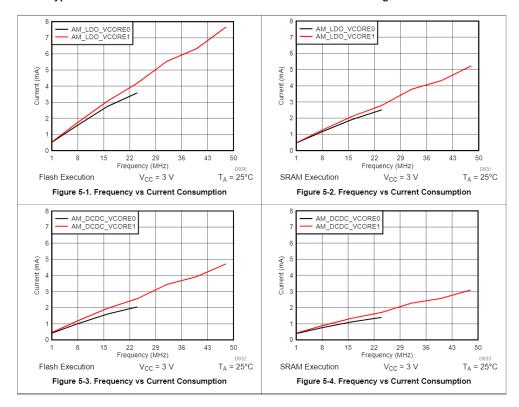

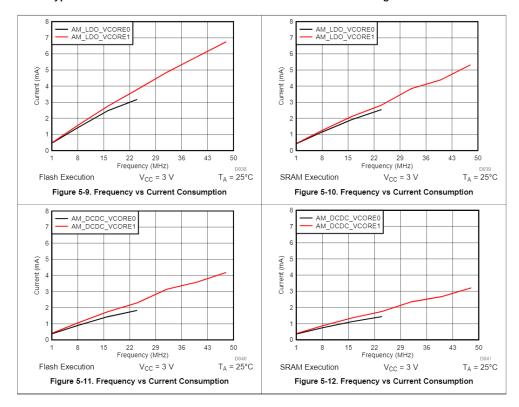

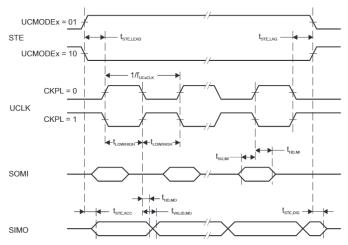

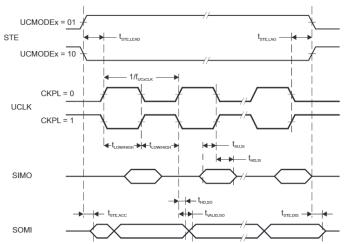

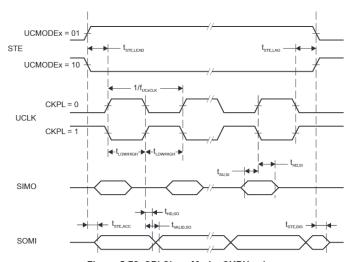

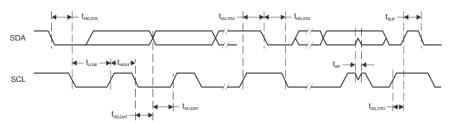

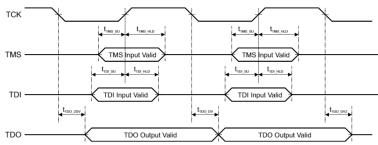

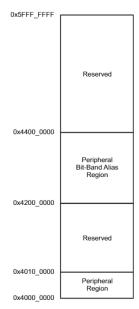

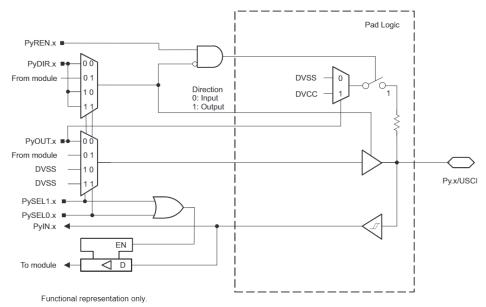

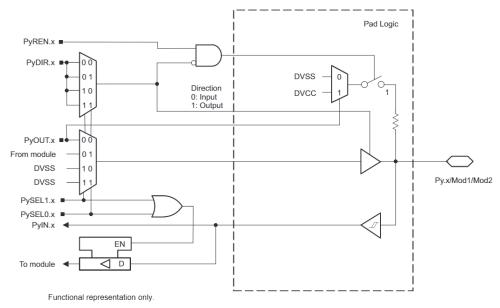

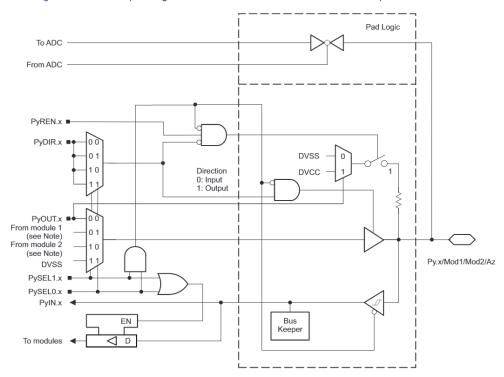

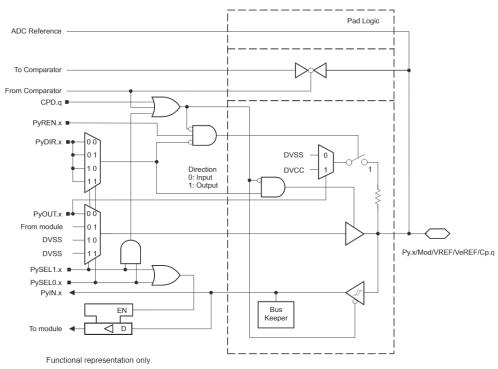

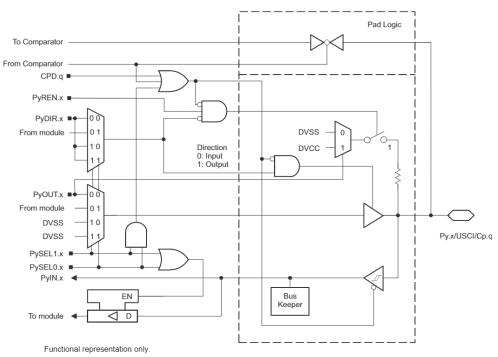

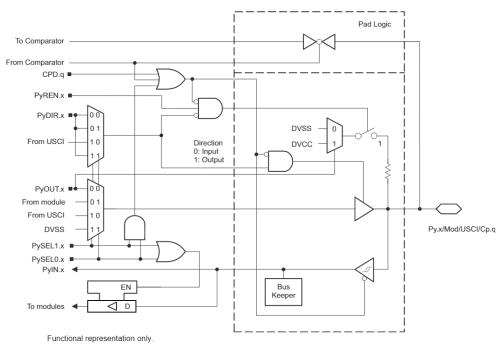

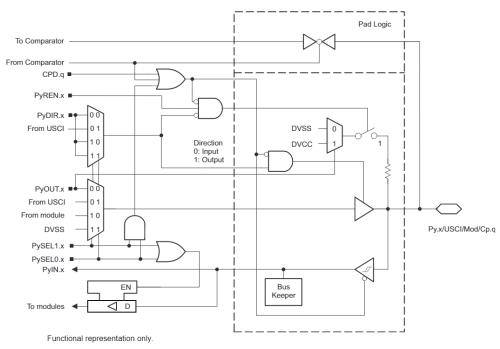

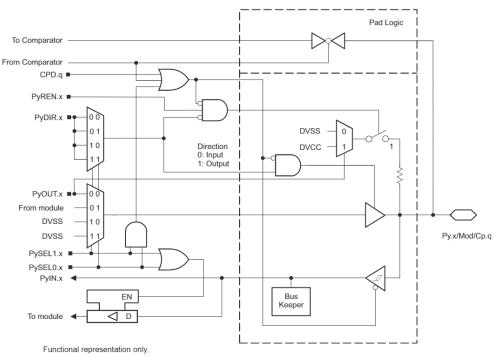

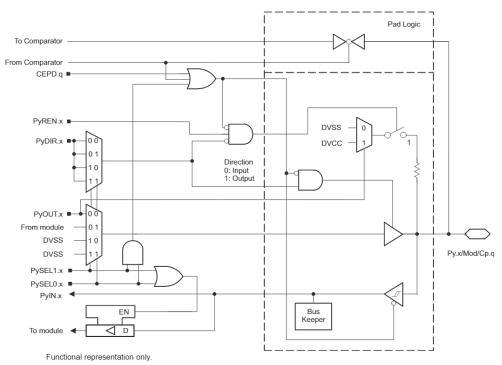

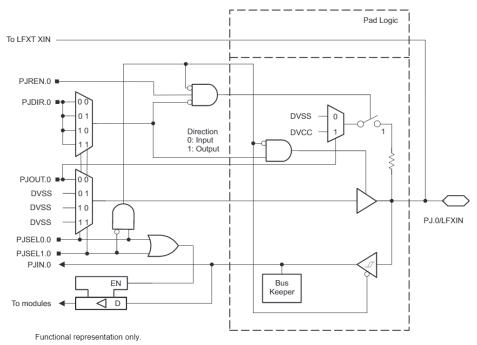

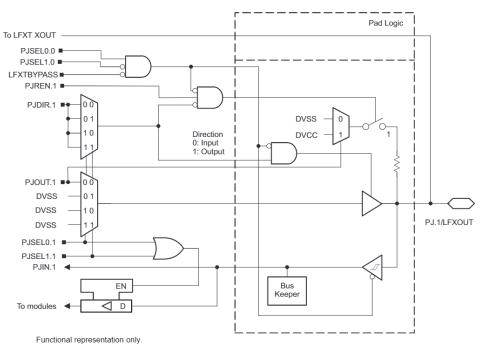

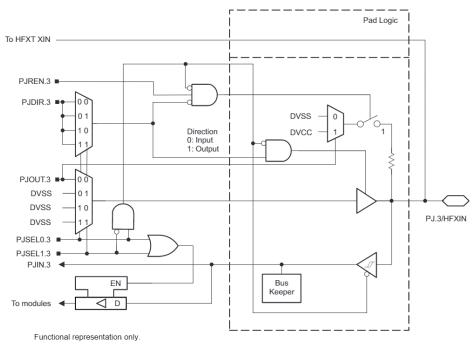

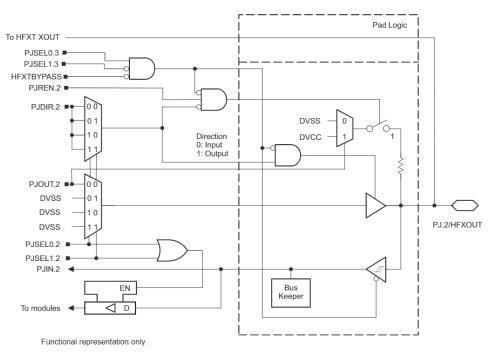

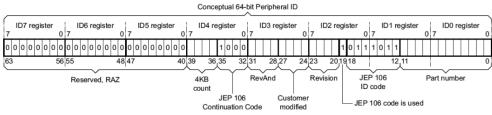

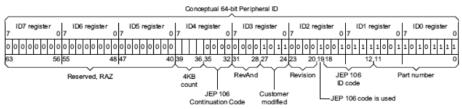

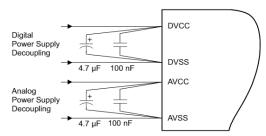

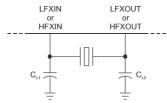

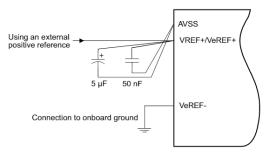

| 100 | N/A                    | N/A  | UCB3STE                        | I/O                 | LVCMOS                     | DVCC                  | N/A                               |     |