### **General Description**

The MAX13041 ±80V fault-protected, high-speed controller area network (CAN) transceiver is ideal for highspeed automotive network applications where high reliability and advanced power management are required. The device links a CAN protocol controller to the physical bus wires of the controller area network and allows communication at speeds up to 1Mbps.

The extended fault-protected voltage range of ±80V on CAN bus lines allows for use in +12V or +42V automotive, and higher voltage +24V and +36V mid-heavy truck applications. Advanced power management features make the MAX13041 ideal for automotive electronic control unit (ECU) modules that are permanently supplied by battery, regardless of the ignition switch position (clamp-30, Type-A modules). The device controls one or more external voltage regulators to provide a low-power sleep mode for an entire clamp-30 node. Wake-on CAN capability allows the MAX13041 to restore power to the node upon detection of CAN bus activity.

The MAX13041 is functionally compatible with the Philips TJA1041A and is a pin-to-pin replacement with improved performance. The MAX13041 is available in a 14-pin SO package, and operates over the -40°C to +125°C automotive temperature range.

### **Applications**

- +12V Automotive—Clamp 30 Modules

- +42V Automotive—Clamp 30 Modules

- +24V Mid-Heavy Truck—Clamp 30 Modules Military and Commercial Aircraft

### **Features**

- **♦** Functionally Compatible Pin-to-Pin Replacement for the Philips TJA1041A

- ♦ ±12kV HBM ESD Protection on CANH, CANL

- **♦** ±80V Fault Protection on CANH, CANL, SPLIT; Up to +76V Operation on VBAT

- ♦ Fully Compatible with the ISO11898 Standard

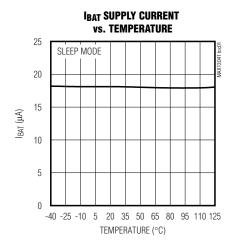

- **♦ Low VBAT Supply Current in Standby and Sleep** Modes (18µA Typical)

- ♦ Voltage Level Translation for Interfacing with +2.8V to +5.5V CAN Protocol Controllers

- **♦** Recessive Bus Stabilization (SPLIT)

- **♦ Allows Implementation of Large Networks**

### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE |

|----------------|-----------------|-------------|

| MAX13041ASD+   | -40°C to +125°C | 14 SO       |

| MAX13041ASD/V+ | -40°C to +125°C | 14 SO       |

+Denotes a lead(Pb)-free/RoHS-compliant package. N Denotes an automotive qualified part.

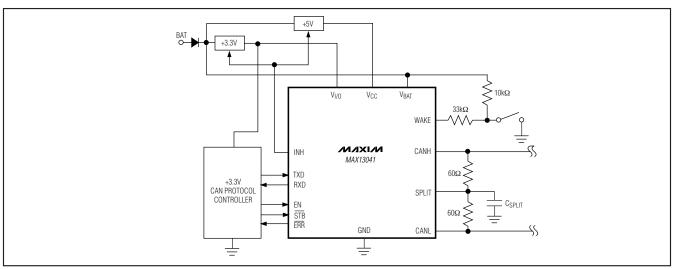

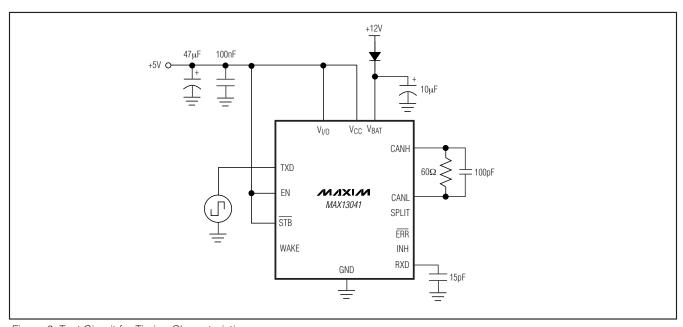

### **Typical Operating Circuit**

Pin Configuration appears at end of data sheet.

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.) |                                   | Continuous Power Dissipation (T <sub>A</sub> = +70°C | 5)             |

|-----------------------------------|-----------------------------------|------------------------------------------------------|----------------|

| VCC, VI/O                         | 0.3V to +6V                       | 14-Pin SO (derate 8.3mW/°C above +70°                | C)667mW        |

| V <sub>BAT</sub>                  | 0.3V to +80V                      | Operating Temperature Range                          | 40°C to +125°C |

| TXD, RXD, STB, EN, ERR            | 0.3V to +6V                       | Storage Temperature Range                            | 65°C to +150°C |

| INH, WAKE                         | 0.3V to (V <sub>BAT</sub> + 0.3V) | Junction Temperature                                 | +150°C         |

| CANH, CANL, SPLIT                 | 0V to ±80V continuous             | Lead Temperature (soldering, 10s)                    | +300°C         |

|                                   |                                   |                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +4.75V \text{ to } +5.25V, V_{I/O} = +2.8V \text{ to } V_{CC}, V_{BAT} = +5V \text{ to } +76V, T_A = T_{MIN} \text{ to } T_{MAX}, R_L = 60\Omega, unless otherwise noted. Typical values are at <math>V_{CC} = +5V, V_{I/O} = +3.3V, V_{BAT} = +12V \text{ and } T_A = +25^{\circ}C.)$  (Notes 1, 2)

| PARAMETER                                                              | SYMBOL                   | CONDITIONS                                                                          | MIN  | TYP | MAX  | UNITS |  |

|------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------|-----|------|-------|--|

| V <sub>CC</sub> Input Voltage                                          | Vcc                      | Operating range                                                                     | 4.75 |     | 5.25 | V     |  |

| V <sub>I/O</sub> Input Voltage                                         | V <sub>I/O</sub>         | Operating range                                                                     | 2.80 |     | 5.25 | V     |  |

| V <sub>BAT</sub> Input Voltage                                         | V <sub>BAT</sub>         | Operating range                                                                     | 5    |     | 76   | V     |  |

| V <sub>CC</sub> Undervoltage Detection<br>Level for Forced Sleep Mode  | V <sub>CC</sub> (SLEEP)  |                                                                                     | 2.75 | 3.3 | 4.50 | V     |  |

| V <sub>I/O</sub> Undervoltage Detection<br>Level for Forced Sleep Mode | V <sub>I</sub> /O(SLEEP) |                                                                                     | 0.5  | 1.5 | 2.0  | V     |  |

| V <sub>BAT</sub> Voltage Level for Failsafe<br>Fallback Mode           | VBAT(STBY)               | V <sub>CC</sub> = +5V (fail-safe)                                                   | 2.75 | 3.3 | 4.50 | V     |  |

| V <sub>BAT</sub> Voltage Level for Setting<br>PWON Flag                | VBAT(PWON)               | V <sub>CC</sub> = 0V                                                                | 2.5  | 3.3 | 4.1  | V     |  |

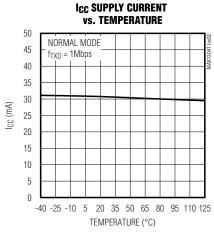

|                                                                        |                          | Normal mode, V <sub>TXD</sub> = 0V (dominant)                                       |      | 55  | 80   |       |  |

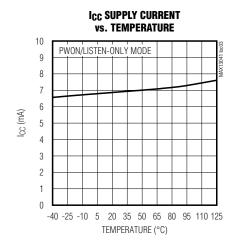

| V <sub>CC</sub> Input Current                                          | Icc                      | Normal or PWON/listen-only mode,<br>V <sub>TXD</sub> = V <sub>I/O</sub> (recessive) |      | 6   | 10   | mA    |  |

|                                                                        |                          | Standby or sleep mode                                                               |      | 1.8 | 8    | μΑ    |  |

|                                                                        |                          | Normal mode, V <sub>TXD</sub> = 0V (dominant)                                       |      | 230 | 700  |       |  |

| V <sub>I/O</sub> Input Current                                         | I <sub>I/O</sub>         | Normal or PWON/listen-only mode,<br>$V_{TXD} = V_{I/O}$ (recessive)                 |      | 1   | 5    | μΑ    |  |

|                                                                        |                          | Standby or sleep mode, V <sub>TXD</sub> = V <sub>I/O</sub>                          |      | 0.7 | 3    |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=+4.75 \text{V to} +5.25 \text{V}, V_{I/O}=+2.8 \text{V to} V_{CC}, V_{BAT}=+5 \text{V to} +76 \text{V}, T_A=T_{MIN} \text{ to} T_{MAX}, R_L=60 \Omega$ , unless otherwise noted. Typical values are at  $V_{CC}=+5 \text{V}, V_{I/O}=+3.3 \text{V}, V_{BAT}=+12 \text{V}$  and  $T_A=+25 ^{\circ} \text{C}.)$  (Notes 1, 2)

| PARAMETER                      | SYMBOL          | CONDITIONS                                                                                                             | MIN                       | TYP                       | MAX                       | UNITS |

|--------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

|                                |                 | Normal or PWON/listen-only mode,<br>VBAT = +5V to +76V                                                                 |                           | 20                        | 40                        |       |

| V <sub>BAT</sub> Input Current | IBAT            | Standby mode, V <sub>INH</sub> = V <sub>WAKE</sub> = V <sub>BAT</sub> = +12V                                           |                           | 18                        | 28                        | μΑ    |

|                                |                 | Sleep mode, V <sub>INH</sub> = V <sub>CC</sub> = V <sub>I/O</sub> = 0V,<br>V <sub>WAKE</sub> = V <sub>BAT</sub> = +12V |                           | 18                        | 28                        |       |

| TRANSMITTER DATA INPUT (       | TXD)            |                                                                                                                        |                           |                           |                           |       |

| High-Level Input Voltage       | VIH             |                                                                                                                        | 0.7 x<br>V <sub>I/O</sub> |                           | V <sub>I/O</sub> + 0.3    | ٧     |

| Low-Level Input Voltage        | VIL             |                                                                                                                        |                           |                           | 0.3<br>V <sub>I/O</sub>   | V     |

| High-Level Input Current       | Iн              | V <sub>TXD</sub> = V <sub>I</sub> /O                                                                                   | -5                        | 0                         | +5                        | μΑ    |

| Low-Level Input Current        | IIL             | $V_{TXD} = 0.3 V_{I/O}$                                                                                                | -70                       | -250                      | -500                      | μΑ    |

| Input Capacitance              | Cl              |                                                                                                                        |                           | 5                         |                           | рF    |

| RECEIVER DATA OUTPUT (R        | XD)             |                                                                                                                        |                           |                           |                           |       |

| High-Level Output Current      | Іон             | $V_{RXD} = V_{I/O} - 0.4V$ , $V_{I/O} = V_{CC}$                                                                        | -1                        | -3                        | -6                        | mA    |

| Low-Level Output Current       | loL             | $V_{RXD} = +0.4V$ , $V_{TXD} = V_{I/O}$ , bus dominant                                                                 | 2                         | 5                         | 12                        | mA    |

| STANDBY AND ENABLE CON         | TROL INPUTS     | (STB AND EN)                                                                                                           |                           |                           |                           |       |

| High-Level Input Voltage       | VIH             |                                                                                                                        | 0.7 x<br>V <sub>I/O</sub> |                           | V <sub>I/O</sub> + 0.3    | V     |

| Low-Level Input Voltage        | VIL             |                                                                                                                        |                           |                           | 0.3<br>V <sub>I/O</sub>   | V     |

| High-Level Input Current       | IIH             | VSTB = VEN = 0.7 VI/O                                                                                                  | 1                         | 4                         | 10                        | μA    |

| Low-Level Input Current        | IIL             | VSTB = VEN = 0V                                                                                                        | -1                        | 0                         | +1                        | μA    |

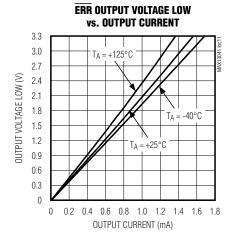

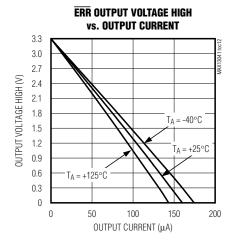

| ERROR AND POWER-ON IND         | ICATION OUTP    | UT (ERR)                                                                                                               | •                         |                           |                           |       |

| High-Level Output Current      | I <sub>OH</sub> | $V_{\overline{ERR}} = V_{I/O} - 0.4V$ , $V_{I/O} = V_{CC}$                                                             | -4                        | -20                       | -50                       | μΑ    |

| Low-Level Output Current       | loL             | VERR = +0.4V                                                                                                           | 0.10                      | 0.2                       | 0.35                      | mA    |

| LOCAL WAKE-UP INPUT (WA        | KE)             |                                                                                                                        |                           |                           |                           |       |

| High-Level Input Current       | Iн              | VWAKE = VBAT - 1.9V                                                                                                    | -1                        | -5                        | -10                       | μΑ    |

| Low-Level Input Current        | lıL             | VWAKE = VBAT - 3.2V                                                                                                    | 1                         | 5                         | 10                        | μΑ    |

| Threshold Voltage              | V <sub>TH</sub> | V <sub>STB</sub> = 0V                                                                                                  | V <sub>BAT</sub> - 3.2    | V <sub>BAT</sub><br>- 2.5 | V <sub>BAT</sub><br>- 1.9 | ٧     |

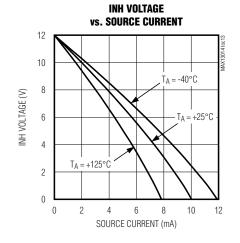

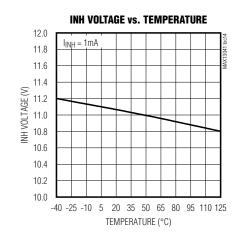

| INHIBIT OUTPUT (INH)           | •               |                                                                                                                        |                           |                           |                           |       |

| High-Level Voltage Drop        | ΔVH             | I <sub>INH</sub> = -0.18mA                                                                                             | 0.05                      | 0.2                       | 0.80                      | V     |

| Leakage Current                | HLI             | Sleep mode                                                                                                             |                           | 0                         | 5                         | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=+4.75V \text{ to } +5.25V, V_{I/O}=+2.8V \text{ to } V_{CC}, V_{BAT}=+5V \text{ to } +76V, T_A=T_{MIN} \text{ to } T_{MAX}, R_L=60\Omega, unless otherwise noted. Typical values are at <math>V_{CC}=+5V, V_{I/O}=+3.3V, V_{BAT}=+12V \text{ and } T_A=+25^{\circ}C.)$  (Notes 1, 2)

| PARAMETER                                                              | SYMBOL                    | CONDITIONS                                                     |                                            | MIN                    | TYP        | MAX                    | UNITS |

|------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------|------------|------------------------|-------|

| BUS LINES (CANH AND CANL)                                              |                           |                                                                |                                            |                        |            |                        |       |

| Deminant Output Valtage                                                | V(a (5 a) t)              | V= 0V                                                          | CANH                                       | 3.00                   | 3.7        | 4.25                   | V     |

| Dominant Output Voltage                                                | V <sub>O</sub> (DOM)      | $V_{TXD} = 0V$                                                 | CANL                                       | 0.50                   | 1.3        | 1.75                   | V     |

| Differential Bus Output Voltage                                        | Vo(DIE)(DI IO)            | $V_{TXD} = 0V, 45\Omega <$                                     | $R_L < 65\Omega$                           | 1.50                   |            | 3.0                    | V     |

| (VCANH - VCANL)                                                        | V <sub>O</sub> (DIF)(BUS) | $V_{TXD} = V_{I/O}$ , no lo                                    | pad                                        | -50                    |            | +50                    | mV    |

| Recessive Output Voltage                                               | V <sub>O(RECES)</sub>     | Normal or PWON/<br>V <sub>TXD</sub> = V <sub>I/O</sub> , no lo | •                                          | 2                      | 2.4        | 3                      | V     |

|                                                                        |                           | Standby or sleep                                               | mode, no load                              | -0.1                   | 0          | +0.1                   | V     |

|                                                                        |                           |                                                                | CANH, V <sub>CANH</sub> = -5V              | -45                    | 66         | -95                    |       |

| Short-Circuit Current                                                  | I <sub>O(SC)</sub>        | V <sub>T</sub> XD = 0V                                         | CANL, V <sub>CANL</sub> = +40V<br>(Note 3) | 45                     | 70         | 100                    | mA    |

| Detectable Short-Circuit Resistance Among Bus Lines VBAT, VCC, and GND | Rsc(Bus)                  | Normal mode                                                    | , ,                                        |                        |            | 50                     | Ω     |

| Recessive Output Current                                               | lo(reces)                 | -40V < VCANH, VC                                               | CANL < +40V                                | -3.1                   |            | +3.1                   | mA    |

| Differential Receiver Threshold                                        |                           | -12V < VCANH, VCANL < +12V,<br>normal or PWON/listen-only mode |                                            | 0.5                    | 0.7        | 0.9                    | V     |

| Voltage                                                                | VDIF(TH)                  | -12V < VCANH, VCANL < +12V,<br>standby or sleep mode           |                                            | 0.50                   | 0.76       | 1.15                   | ٧     |

| Differential Receiver Hysteresis<br>Voltage                            | V <sub>HYS(DIF)</sub>     | Normal or PWON/listen-only mode<br>-12V < VCANH; VCANL < +12V  |                                            |                        | 60         |                        | mV    |

| Input Leakage Current                                                  | ILI                       | V <sub>C</sub> C = 0V; V <sub>C</sub> ANH                      | I = VCANL = +5V                            |                        | 200        | 280                    | μΑ    |

| Common-Mode Input Resistance                                           | R <sub>I</sub> (CM)       | Standby or norma                                               | al mode (Note 4)                           | 15                     | 25         | 35                     | kΩ    |

| Common-Mode Input Resistance<br>Matching                               | R <sub>I</sub> (CM)(M)    | VCANH = VCANL                                                  |                                            | -3                     | 0          | +3                     | %     |

| Differential Input Resistance                                          | R <sub>I(DIF)</sub>       | Standby or norma                                               | al mode                                    | 25                     | 50         | 75                     | kΩ    |

| Common-Mode Input<br>Capacitance                                       | C <sub>I(CM)</sub>        | V <sub>TXD</sub> = V <sub>CC</sub>                             |                                            |                        | 20         |                        | pF    |

| Differential Input Capacitance                                         | C <sub>I(DIF)</sub>       | V <sub>TXD</sub> = V <sub>CC</sub>                             |                                            |                        | 10         |                        | рF    |

| ESD Protection                                                         | , ,                       | Human Body Mod                                                 | del (HBM)                                  |                        | ±12        |                        | kV    |

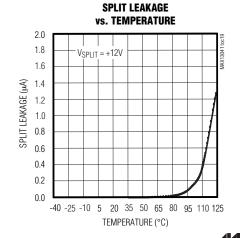

| COMMON-MODE STABILIZATIO                                               | N (SPLIT)                 |                                                                |                                            |                        |            |                        | •     |

| Output Voltage                                                         | Vo                        | Normal or PWON/<br>-500µA < Isplit <                           |                                            | 0.3<br>V <sub>CC</sub> | 0.5<br>VCC | 0.7<br>V <sub>CC</sub> | V     |

| Leakage Current                                                        | HLI                       | Standby or sleep mode<br>-40V < V <sub>SPLIT</sub> < +40V      |                                            |                        | 0          | 5                      | μΑ    |

| THERMAL PROTECTION                                                     |                           |                                                                |                                            |                        |            |                        |       |

| Thermal Shutdown Threshold                                             | T <sub>J(SD)</sub>        |                                                                |                                            |                        | 165        |                        | °C    |

| Thermal Shutdown Hysteresis                                            | T <sub>J</sub> (SD)HYST   |                                                                |                                            | _                      | 10         |                        | °C    |

#### **TIMING CHARACTERISTICS**

$(V_{CC}=+4.75 V~to~+5.25 V,~V_{I/O}=+2.8 V~to~V_{CC},~V_{BAT}=+5 V~to~+76 V,~T_{A}=T_{MIN}~to~T_{MAX},~R_{L}=60 \Omega,~unless~otherwise~noted.~Typical~values~are~at~V_{CC}=+5 V,~V_{I/O}=+3.3 V,~V_{BAT}=+12 V~and~T_{A}=+25 ^{\circ}C.)~(Note~2)$

| PARAMETER                                                                   | SYMBOL                 | CONDITIONS                                                                                     | MIN | TYP | MAX  | UNITS |

|-----------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------|-----|-----|------|-------|

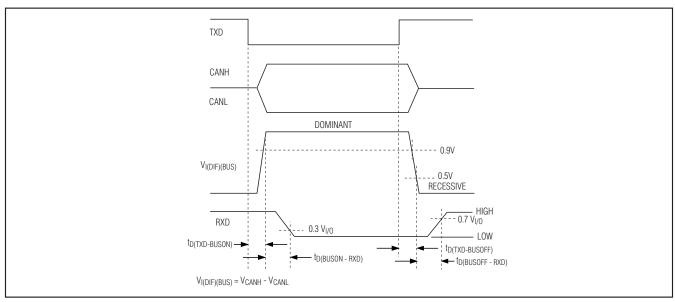

| Delay TXD to Bus Active                                                     | tD(TXD-BUSON)          | Normal mode (Figures 1 and 2)                                                                  |     | 46  | 100  | ns    |

| Delay TXD to Bus Inactive                                                   | tD(TXD-BUSOFF)         | Normal mode (Figures 1 and 2)                                                                  |     | 60  | 100  | ns    |

| Delay Bus Active to RXD                                                     | tD(BUSON-RXD)          | Normal or PWON/listen-only mode (Figures 1 and 2)                                              |     | 59  | 115  | ns    |

| Delay Bus Inactive to RXD                                                   | tD(BUSOFF-RXD)         | Normal or PWON/listen-only mode (Figures 1 and 2)                                              |     | 60  | 160  | ns    |

| Undervoltage Detection Time on V <sub>CC</sub> and V <sub>I/O</sub>         | tuv(vcc),<br>tuv(vi/o) | V <sub>BAT</sub> = +12V                                                                        | 5.0 | 8.4 | 12.5 | ms    |

| TXD Dominant Timeout                                                        | t <sub>DOM(TXD)</sub>  | $V_{TXD} = 0V$                                                                                 | 300 | 610 | 1000 | μs    |

| Bus Dominant Timeout                                                        | tDOM(BUS)              | V <sub>O(DIF)</sub> BUS > 0.9V                                                                 | 300 | 620 | 1000 | μs    |

| Minimum Hold Time of Go-to-Sleep Command                                    | t <sub>H(MIN)</sub>    | V <sub>BAT</sub> = +12V                                                                        | 17  | 34  | 56   | μs    |

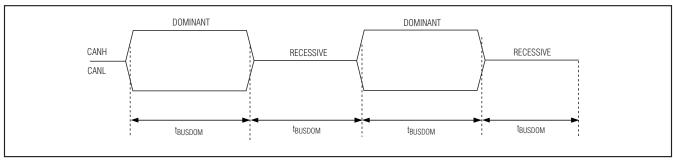

| Dominant Time for Wake-Up<br>Through Bus                                    | tBUSDOM                | Standby or sleep mode, V <sub>BAT</sub> = +12V,<br>CANL = 0V, CANH pulse 0V to +2V<br>(Note 5) | 0.9 | 2   | 5.0  | μs    |

| Minimum Wake-Up Time After<br>Receiving a Falling or Rising<br>Edge on WAKE | twake                  | Standby or sleep mode; V <sub>BAT</sub> = +12V                                                 | 5   | 25  | 50   | μs    |

- Note 1: Positive current flows into the device.

- **Note 2:** Limits over the operating temperature range are tested at worst-case supply voltage and compliant over the complete voltage range.

- Note 3: Current measured at +20V and guaranteed by design up to +40V.

- Note 4: Common-mode voltage range ±40V.

- Note 5: A remote wake-on CAN request is generated upon the detection of two dominant bus cycles, each followed by a recessive bus cycle.

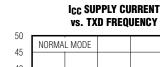

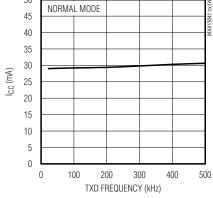

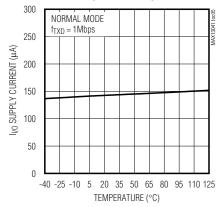

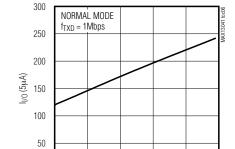

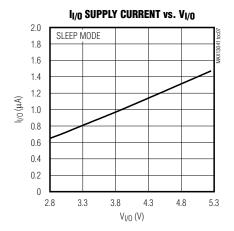

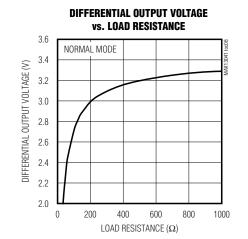

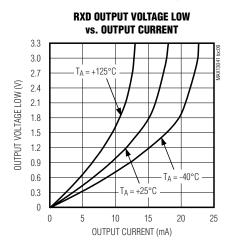

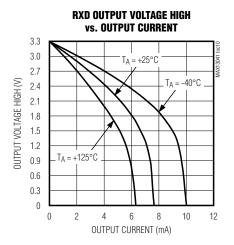

### **Typical Operating Characteristics**

$(V_{CC} = +5V, V_{I/O} = +3.3V, V_{BAT} = +12V, R_L = 60\Omega, C_{SPLIT} = 4700 pF, T_A = +25^{\circ}C, unless otherwise noted.)$

3.8

0

2.8

3.3

II/O SUPPLY CURRENT vs. VI/O

4.3

$V_{I/O}(V)$

4.8

5.3

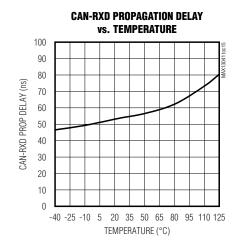

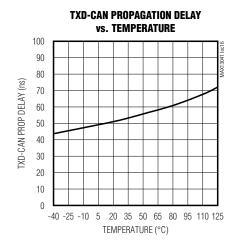

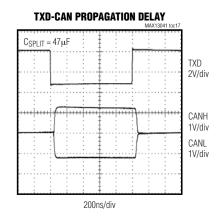

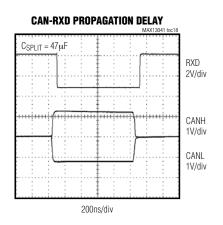

### Typical Operating Characteristics (continued)

$(V_{CC} = +5V, V_{I/O} = +3.3V, V_{BAT} = +12V, R_L = 60\Omega, C_{SPLIT} = 4700pF, T_A = +25^{\circ}C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{CC} = +5V, V_{I/O} = +3.3V, V_{BAT} = +12V, R_L = 60\Omega, C_{SPLIT} = 4700pF, T_A = +25^{\circ}C, unless otherwise noted.)$

### Pin Description

| PIN | NAME             | FUNCTION                                                                                                                                                                                                               |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TXD              | Data Transmit Input, CMOS Compatible. TXD is internally pulled up to V <sub>I/O</sub> .                                                                                                                                |

| 2   | GND              | Ground                                                                                                                                                                                                                 |

| 3   | Vcc              | Supply Voltage +4.75V to +5.25V. Bypass $V_{CC}$ to ground with a 0.1 $\mu$ F ceramic capacitor as close as possible to the device.                                                                                    |

| 4   | RXD              | Data Receive Output, CMOS Compatible                                                                                                                                                                                   |

| 5   | V <sub>I/O</sub> | Supply Voltage for I/O Level Translation, $+2.8V < V_{I/O} < V_{CC}$ (see the <i>Level Shifting</i> section). Bypass $V_{I/O}$ to ground with a 0.1µF ceramic capacitor as close as possible to the device.            |

| 6   | EN               | Enable Input. Control the operating mode by driving EN logic-high or logic-low (see Table 1 and Figure 4.)                                                                                                             |

| 7   | INH              | Inhibit Output. INH controls one or more external voltage regulators.                                                                                                                                                  |

| 8   | ERR              | Error Output, Active Low. ERR indicates errors and displays status of internal flags.                                                                                                                                  |

| 9   | WAKE             | Local Wake-Up Input. Present a voltage transition on WAKE to generate a local wake-up event.                                                                                                                           |

| 10  | VBAT             | Battery Voltage Input. Bypass $V_{\text{BAT}}$ to ground with a 0.1 $\mu$ F ceramic capacitor as close as possible to the device.                                                                                      |

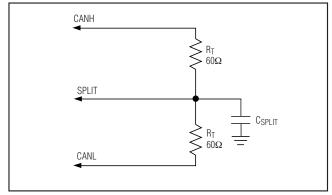

| 11  | SPLIT            | Split Termination Voltage Output. Connect SPLIT to the center node of two $60\Omega$ termination resistors to provide common-mode voltage stabilization (see Figure 3). SPLIT outputs a voltage of V <sub>CC</sub> /2. |

| 12  | CANL             | Low-Level CAN Differential Bus Line                                                                                                                                                                                    |

| 13  | CANH             | High-Level CAN Differential Bus Line                                                                                                                                                                                   |

| 14  | STB              | Standby Input, Active Low. Drive STB logic-high or logic-low to control the operating mode (see Table 1 and Figure 4.)                                                                                                 |

### **Timing Diagrams**

Figure 1. Timing Diagram

Figure 2. Test Circuit for Timing Characteristics

### **Detailed Description**

The MAX13041 ±80V fault-protected, high-speed CAN transceiver is intended for high-speed industrial and automotive network applications where high reliability and advanced power management are required. The device links a CAN protocol controller to the physical bus wires of the controller area network (CAN) and allows communication at speeds up to 1Mbps. Built-in level shifting allows for direct connection to protocol controllers operating from lower voltages. The extended fault-protected voltage range of ±80V on CAN bus lines allows for use in +12V or +42V automotive, and higher voltage +24V and +36V heavy-duty truck applications.

Advanced power management features make the MAX13041 ideal for automotive electronic control unit (ECU) modules that are permanently supplied by battery, regardless of the ignition switch position (clamp-30, type-A modules). The device controls one or more external voltage regulators to provide a low-power sleep mode for an entire clamp-30 node. Wake-on CAN capability allows the MAX13041 to restore power to the node upon detection of CAN bus activity. The MAX13041 is functionally compatible with the Philips TJA1041A and is a pin-to-pin replacement with improved performance.

#### **CAN Interface**

The ISO11898 specification describes the physical layer of a controller area network (CAN). A CAN implementation is comprised of multiple transceiver modules linked by a pair of bus wires. Communication between modules occurs through transmission and reception of differential logic states on the bus lines. Two complimentary logic states are defined by ISO11898. A dominant state results when the differential voltage on the CAN bus lines is greater than 0.9V. A recessive bus state results when the differential voltage is less than 0.5V (Figure 1). The CAN bus exhibits a wired-AND characteristic, meaning the bus is only recessive when all connected transmitters are recessive. Any transmitter asserting a dominant logic state forces the entire CAN bus dominant.

The MAX13041 accepts logic-level data from the CAN protocol controller on TXD. Drive TXD low to assert a dominant state on the CAN bus. Drive TXD high to release the CAN bus to a recessive state. TXD is internally pulled up to V<sub>I/O</sub>. The state of the CAN bus is presented to the protocol controller as a logic level on RXD. The MAX13041 receiver remains active during transmission to allow for the bit-wise arbitration scheme specified by the CAN protocol.

#### **Level Shifting**

The MAX13041 provides level shifting on TXD, RXD, EN,  $\overline{\text{STB}}$ , WAKE and  $\overline{\text{ERR}}$  for compatibility with lower-voltage protocol controllers. Set the interface logic levels for TXD, RXD, EN,  $\overline{\text{STB}}$ , WAKE, and  $\overline{\text{ERR}}$  by connecting V<sub>I/O</sub> to the supply voltage of a CAN protocol controller, or another voltage from +2.8V to +5.25V.

#### Split-Termination and Common-Mode Voltage Stabilization

The CAN bus specification requires a total bus load resistance of  $60\Omega$ . Each end of the bus should be terminated with  $120\Omega$ , the characteristic impedance of the bus line. Electromagnetic emission (EME) is reduced by a split-termination method, whereby each end of the bus line is terminated by  $120\Omega$  split into two  $60\Omega$  resistors in series (see Figure 3). A bypass capacitor shunts noise to ground from the node connecting the  $60\Omega$  resistors.

When the CAN bus is recessive, the common-mode voltage is pulled low by the leakage current from inactive modules. When the CAN bus subsequently goes dominant, the proper common-mode voltage is restored by the transmitting device. A common-mode voltage step results, generating excessive EME. To mitigate this problem, the common-mode voltage of the bus is forced to VCC/2 by biasing the split-termination node (see Figure 3). During normal and PWON/listen-only modes, a stabilized DC voltage of VCC/2 is present on SPLIT. Connect SPLIT to the node connecting the two  $60\Omega$  termination resistors to stabilize the common-mode voltage of the bus and prevent EME from common-mode voltage steps.

#### **Power-Management Operating Modes**

The MAX13041 provides advanced power management for a clamp-30 node by controlling one or more external voltage regulators. Five operating modes provide different functionality to minimize power consumption.

Figure 3. Biased Split Termination

In the lowest-power mode, the MAX13041 disables external voltage regulators to provide a sleep mode for the entire node. The MAX13041 restores power to the node upon a logic transition on WAKE or detection of CAN bus activity.

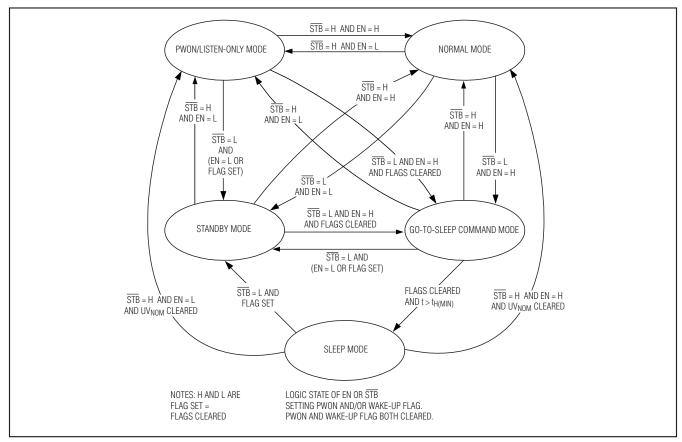

The operating mode is determined by an internal state machine controlled by EN and STB, as well as several internal flags (see Table 1 and Figure 4).

#### Normal Mode

The MAX13041 provides full bidirectional CAN communication in normal mode. Drive TXD to transmit data on the differential CAN bus lines CANH and CANL. The CAN bus state is presented on RXD, a level-shifted logic output. SPLIT is biased to VCC/2 to allow CAN bus common-mode stabilization. INH is logic-high, enabling one or more external voltage regulators (see Table 1).

#### PWON/Listen-Only Mode

In PWON/listen-only mode, the CAN transmitter is disabled. The CAN receiver remains active and the CAN bus state is presented on RXD, a level-shifted logic output. As in normal mode, SPLIT is biased to  $V_{\rm CC}/2$  to allow CAN bus common-mode stabilization. INH is logic-high, enabling one or more external voltage regulators (see Table 1).

#### Standby Mode

Standby mode is the first low-power operating mode. The CAN transmitter and receiver are disabled, and a low-power receiver is enabled to monitor the CAN bus for activity. To reduce power consumption, common-mode stabilization is disabled. SPLIT becomes high impedance, and CANH and CANL are biased to ground by the termination resistors. INH remains logichigh, enabling one or more external voltage regulators (see Table 1).

#### Go-to-Sleep Command Mode

Go-to-sleep command mode is part of the controlled sequence for entering sleep mode. The MAX13041 remains in go-to-sleep command mode for a hold time of 56µs (max), and subsequently enters sleep mode if no wake events are detected. During the hold time, if the state of EN or STB changes, or if the UVBAT, PWON, or wake-up flags are set, the go-to-sleep sequence is aborted. During go-to-sleep command mode, functionality is the same as in standby mode.

#### Sleep Mode

Sleep mode is the lowest-power operating mode. The CAN transmitter and receiver are disabled, and a low-power receiver is enabled to monitor the CAN bus for

**Table 1. Operating Modes**

| CONTR | OL PINS      |                   | INTERNA | L FLAGS               | OPERATING MODE                                        | INH      |

|-------|--------------|-------------------|---------|-----------------------|-------------------------------------------------------|----------|

| STB   | EN           | UV <sub>NOM</sub> | UVBAT   | PWON, WAKE-UP         | OPERATING MODE                                        | INFI     |

|       |              | SET               | Χ       | X                     | SLEEP (Notes 6, 7)                                    | FLOATING |

| X     | Χ            | CLEAR             | SET     | EITHER FLAG SET       | STANDBY                                               | Н        |

|       |              | CLEAR             | SET     | BOTH FLAGS CLEAR      | STANDBY FROM ANY OTHER MODE                           | Н        |

|       | L L CLEAR CL |                   |         | EITHER FLAG SET       | STANDBY                                               | Н        |

| L     |              |                   | CLEAR   | LEAR BOTH FLAGS CLEAR | NO CHANGE FROM SLEEP MODE                             | FLOATING |

|       |              |                   |         | BOTH FLAGS CLEAR      | STANDBY FROM ANY OTHER MODE                           | Н        |

|       |              |                   |         | EITHER FLAG SET       | R FLAG SET STANDBY                                    |          |

|       |              |                   | OLEAD   |                       | NO CHANGE FROM SLEEP MODE                             | FLOATING |

| L     | Н            | CLEAR             | CLEAR   | BOTH FLAGS CLEAR      | GO-TO-SLEEP COMMAND MODE FROM ANY OTHER MODE (Note 7) | Н        |

| Н     | L            | CLEAR             | CLEAR   | Х                     | X PWON/LISTEN-ONLY                                    |          |

| Н     | Н            | CLEAR             | CLEAR   | X                     | NORMAL (Note 9)                                       | Н        |

- Note 6: Setting the PWON or wake-up flags clears UVNOM flag.

- Note 7: The MAX13041 enters sleep mode from any other mode when UVNOM is set. INH becomes high impedance.

- **Note 8**: When go-to-sleep command mode is selected for longer than tH(MIN), the MAX13041 enters sleep mode. INH becomes high impedance.

- Note 9: PWON and wake-up flags are cleared upon entering normal mode.

Figure 4. State Diagram

activity. To reduce power consumption, common-mode stabilization is disabled. SPLIT becomes high impedance, and CANH and CANL are biased to ground by the termination resistors. INH goes high impedance, disabling one or more external voltage regulators (see Table 1.)

#### Flag Signaling

The MAX13041 uses a set of seven internal flags for system diagnosis and to indicate faults. Five of the flags are available at different times to the CAN protocol controller on  $\overline{\text{ERR}}$ . A logic-low on  $\overline{\text{ERR}}$  indicates a set flag or a fault (see Table 3.) Allow  $\overline{\text{ERR}}$  to stabilize for at least 8µs after changing operating modes.

#### Supply Undervoltage: UVNOM

UV<sub>NOM</sub> is set when supply voltage on V<sub>CC</sub> drops below V<sub>CC</sub>(SLEEP) for longer than t<sub>UV</sub>(V<sub>CC</sub>), or when voltage on V<sub>I/O</sub> drops below V<sub>I/O</sub>(SLEEP) for longer than t<sub>UV</sub>(V<sub>I/O</sub>). When UV<sub>NOM</sub> is set, the MAX13041 enters low-power sleep mode to reduce power consumption. The device

remains in sleep mode for a minimum waiting time before allowing the UV<sub>NOM</sub> flag to be cleared. This waiting time is determined by the same timer used for setting UV<sub>NOM</sub> (t<sub>UV</sub>(vCC) or t<sub>UV</sub>(vIO).) UV<sub>NOM</sub> is cleared by a local wake-up request triggered by a level change on WAKE or by a wake-on-CAN event. UV<sub>NOM</sub> is also cleared by setting the PWON flag.

#### VBAT Undervoltage: UVBAT

UVBAT is set when the voltage on VBAT drops below VBAT(STB). When UVBAT is set, the MAX13041 enters standby mode to reduce power consumption. UVBAT is cleared when the voltage on VBAT is restored and exceeds VBAT(STB). Upon clearing UVBAT, the MAX13041 returns to the operating mode determined by EN and  $\overline{\rm STB}$ .

#### Power-On Flag: PWON

PWON indicates the MAX13041 is in a power-on state. PWON is set when V<sub>BAT</sub> has dropped below V<sub>BAT</sub>(STB) and has subsequently recovered. This condition occurs

### Table 2. Flag Signaling on $\overline{\mathsf{ERR}}$

| INTERNAL FLAG     | FLAG AVAILABLE ON ERR                                                                                        | CONDITIONS TO CLEAR FLAG                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| UV <sub>NOM</sub> | No                                                                                                           | Set PWON or wake-up flags                                                                                     |

| UV <sub>BAT</sub> | No                                                                                                           | Recovery of V <sub>BAT</sub>                                                                                  |

| PWON              | In PWON/listen-only mode (changing from standby, go-to-sleep command, or sleep modes)                        | Entering normal mode                                                                                          |

| Wake-Up           | In standby, go-to-sleep command, and sleep modes (provided V <sub>I/O</sub> and V <sub>CC</sub> are present) | Entering normal mode or setting PWON or UV <sub>NOM</sub> flag                                                |

| Wake-Up Source    | In normal mode (before the fourth dominant to recessive edge on TXD, Note 10)                                | Leaving normal mode or setting PWON flag                                                                      |

| Bus Failure       | In normal mode (after the fourth dominant to recessive edge on TXD, Note 10)                                 | Re-entering normal mode                                                                                       |

| Local Failure     | In PWON/listen-only mode (coming from normal mode)                                                           | Entering normal mode or whenever RXD is dominant while TXD is recessive (and all local failures are resolved) |

Note 10: Allow for a dominant time of at least 4µs per dominant-recessive cycle.

Figure 5. Wake-On-CAN Timing

when battery voltage is first applied to V<sub>BAT</sub>. When the PWON flag is set, UV<sub>NOM</sub> is cleared and sleep mode is disabled. The primary function of the PWON flag is to prevent the MAX13041 from entering sleep mode (and thereby disabling external voltage regulators) before the protocol controller establishes control through EN and STB. The PWON flag is externally indicated as a logic-low on ERR when the MAX13041 is placed into PWON/listen-only mode from standby mode, go-to-sleep command mode, or sleep mode. The PWON flag is cleared when the MAX13041 enters normal mode.

#### Wake-Up Flag

The wake-up flag is set when a local or remote wake-up request is detected. A local wake-up request is generated when the logic level on WAKE changes and remains stable for twake. A remote wake-on CAN request is generated upon the detection of two dominant bus cycles, each followed by a recessive bus

cycle (see Figure 5.) Each bus cycle must exceed tBUS(DOM). The wake-up flag can only be set in standby mode, go-to-sleep command mode, or sleep mode. Setting the wake-up flag resets UV<sub>NOM</sub>, and wake-up requests are not detected during the UV<sub>NOM</sub> flag waiting time immediately after UV<sub>NOM</sub> has been set. The wake-up flag is immediately available as a logic-low on ERR and RXD, provided that V<sub>I/O</sub> and V<sub>CC</sub> are both present. The wake-up flag is cleared when the MAX13041 enters normal mode.

#### Wake-Up Source Flag

The wake-up source flag is set concurrently with the wake-up source flag when a local wake-up event is detected. The wake-up source flag can only be set after the PWON flag has been cleared. The flag is cleared when the MAX13041 leaves normal mode and during initial power-on. The wake-up source flag is externally indicated on ERR when the MAX13041 is in

normal mode, prior to the fourth dominant-to-recessive transition on TXD. A low level on  $\overline{\text{ERR}}$  indicates a local wake-up has occurred.

#### Bus Failure Flag

The bus failure flag is set when the MAX13041 detects a CAN bus short-circuit to  $V_{BAT}$ ,  $V_{CC}$ , or GND for four consecutive dominant-recessive cycles on TXD. The flag is cleared when the MAX13041 leaves normal mode. The bus failure flag is externally indicated as a logic low on  $\overline{ERR}$  in normal mode, after the fourth dominant-to-recessive transition on TXD.

#### Local Failure Flag

The local failure flag indicates five separate local failure conditions (see *Fault Protection & Fail-Safes* section). When one or more local failure conditions have occurred, the local failure flag is set. The flag is cleared when the MAX13041 enters normal mode or when RXD goes logic-low while TXD is logic-high. The local failure flag is externally indicated as a logic-low on ERR when the MAX13041 is placed into PWON/listen-only mode from normal mode.

#### Wake-On CAN

The MAX13041 provides wake-on-CAN capability from sleep mode. When the MAX13041 detects two dominant bus states, each followed by a recessive state (Figure 5), the MAX13041 sets the wake-up flag and enters an operating mode determined by the state of EN and STB. Each CAN logic state must be at least 5µs in duration. This wake-up detection criterion serves to prevent unintentional wake-up events due to bus faults such as VBAT to CANH or an open circuit on CANL. At higher data rates (>125kbit/s), wake-up can not be guaranteed for a single, arbitrary CAN data frame. Two or more consecutive arbitrary CAN data frames may be required to ensure a successful wake-on-CAN event.

#### **External-Voltage Regulator Control**

MAX13041 controls one or more external voltage regulators through INH, a VBAT-referenced, open-drain output. When INH is logic-high, any external voltage regulators are active and power is supplied to the node. When INH is high-impedance, the typical pull-down characteristic of the voltage-regulator inhibit input pulls INH to a logic-low and disables the external voltage regulator(s).

#### Fault Protection & Fail-Safes

The MAX13041 features ±80V tolerance on CAN bus lines CANH, CANL, and SPLIT. Up to +76V operation is possible on VBAT, allowing for use in +42V automotive applications. Additionally, the device detects local and remote bus failures and features fail-safe modes to

prevent damage to the device or interference with CAN bus communication.

The MAX13041 detects five different local faults. When any local fault is detected, the local failure flag is set. Additionally, for faults other than bus dominant clamping, the transmitter is disabled to prevent possible damage to the device. The transmitter remains disabled until the local failure flag is cleared.

#### TXD Dominant Clamping

An extended logic-low level on TXD due to hardware or software failure would ordinarily clamp the CAN bus to a dominant state, blocking communication on the entire bus. This condition is prevented by the TXD dominant time-out feature. If TXD is held low for longer than tDOM(TXD), the local failure flag is set and the transmitter is disabled until the local failure flag is cleared. The TXD time-out value limits the minimum allowable bit rate to 40kbps.

#### RXD Recessive Clamping

If a hardware failure clamps RXD to a logic-high level, the protocol controller assumes the CAN bus is in a recessive state at all times. This has the undesirable effect that the protocol controller assumes the bus is clear and may initiate messages that would interfere with ordinary communication. This local failure is detected by checking the state of RXD when the CAN bus is in a dominant state. If RXD does not reflect the state of the CAN bus, the local failure flag is set and the transmitter is disabled until the local failure flag is cleared.

#### TXD-to-RXD Short-Circuit Detection

A short-circuit between TXD and RXD forces the bus into a permanent dominant state upon the first transmission of a dominant bit because normally the low-side driver of RXD is stronger than the microcontroller high-side driver of TXD. The MAX13041 detects this condition and prevents the resulting bus failure by setting the local failure flag and disabling the transmitter. The transmitter remains disabled until the local failure flag is cleared.

#### **Bus Dominant Clamping**

A short-circuit fault from the CAN bus to V<sub>BAT</sub>, V<sub>CC</sub>, or GND could produce a differential voltage between CANH and CANL greater than the receiver threshold, resulting in a dominant bus state. If the bus state is clamped dominant for longer than t<sub>DOM(BUS)</sub>, the local failure flag is set. The transmitter is not disabled by this fault and the local failure flag is cleared as soon as the bus state becomes recessive.

#### Thermal Shutdown Fault

The local failure flag is set when the junction temperature (T<sub>J</sub>) exceeds the shutdown junction temperature threshold, T<sub>J</sub>(SD). The transmitter is disabled to prevent excessive current dissipation from damaging the device. The transmitter remains disabled until T<sub>J</sub> drops T<sub>J</sub>(SD)HYST degrees, and the local failure flag is cleared.

#### **Recovering from Local Faults**

The local failure flag is cleared and the transmitter is reenabled whenever RXD is dominant while TXD is recessive. This situation occurs normally when the MAX13041 is receiving CAN bus data in the absence of a bus failure. In PWON/listen-only mode,  $\overline{ERR}$  changes to a logic-high to reflect the change in the local failure flag. If there is no activity on the CAN bus, the local failure flag can also be cleared by switching to normal mode from another operating mode. A typical method involves switching to PWON/listen-only mode and reading the local failure flag on  $\overline{ERR}$ . Subsequently, switch back to normal mode to clear the flag. This sequence is then repeated to verify that the failure has been resolved.

#### **ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic discharges encountered during handling and assembly. The CANH and CANL lines are further protected by advanced ESD structures to guard these pins from damage caused by ESD of up to ±12kV as measured by the Human Body Model (HBM). Protection structures prevent damage caused by ESD events in all operating modes, and when the device is unpowered.

#### ESD Models

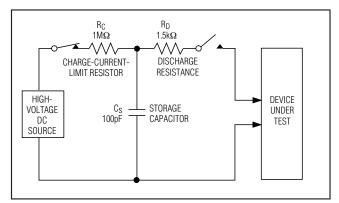

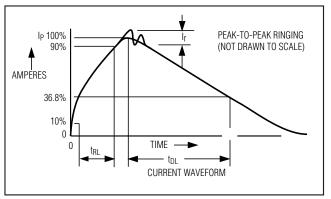

Several ESD testing standards exist for gauging the robustness of ESD structures. The ESD protection of the MAX13041 is characterized for the human body model (HBM). Figure 6 shows the model used to simulate an ESD event resulting from contact with the human body. The model consists of a 100pF storage capacitor that is charged to a high voltage, and subsequently discharged through a 1.5k $\Omega$  resistor. Figure 7 shows the current waveform when the storage capacitor is discharged into a low impedance.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Please contact Maxim for a reliability report documenting test setup, methodology, and results.

### **Applications Information**

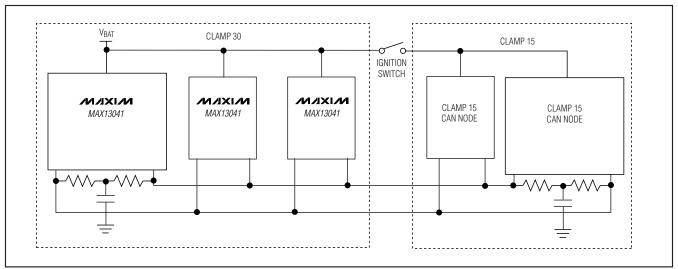

#### Clamp-30, Type-A CAN Modules

The MAX13041 is primarily intended for automotive ECU applications where battery power is permanently supplied to the node (see Figure 8.) This type of application is referred to as a clamp-30 node. ECU modules, which are supplied by the battery only when the ignition switch is closed, are referred to as clamp-15 modules. Because clamp-30 modules are permanently supplied by battery voltage, low power consumption is an essential design requirement. The MAX13041 provides advanced power management to the entire node by controlling one or more external voltage regulators. While CAN transceivers, such as the MAX13041, operate from a supply voltage of +5V, many microprocessors are supplied by voltages of +3.3V and lower. By controlling the supply voltage regulator for the microprocessor, the MAX13041 can force a low-power sleep mode for the entire node.

#### **EMC Considerations**

In multidrop CAN applications, it is important to maintain a direct point-to-point wiring scheme. A single pair of wires should connect each transceiver on the CAN bus, and the bus wires should be properly split-terminated with two  $60\Omega$  resistors at each end as described in Figure 3 . For best EMC performance, do not use a star topology. Any deviation from the point-to-point wiring scheme results in a stub. High-speed edges of the CAN signal reflect from the unterminated stub ends, interfering with communication on the bus. To minimize the effect of these reflections, care should be taken to minimize the length of stubs.

#### **Power-Supply Decoupling**

Bypass V<sub>CC</sub>, V<sub>BAT</sub>, and V<sub>I/O</sub> to ground with  $0.1\mu F$  ceramic capacitors. Place all capacitors as close as possible to the device.

Figure 7. Human Body Model Current Waveform

Figure 8. Typical ECU Architecture with Clamp-30 and Clamp-15 Modules

#### **Pin Configuration** TOP VIEW TXD 1 14 STB 13 CANH GND 2 12 CANL V<sub>CC</sub> 3 RXD 4 MAX13041 11 SPLIT V<sub>I/0</sub> 5 10 V<sub>BAT</sub> EN 6 9 WAKE INH 7 8 ERR so

\_Chip Information

PROCESS: BICMOS

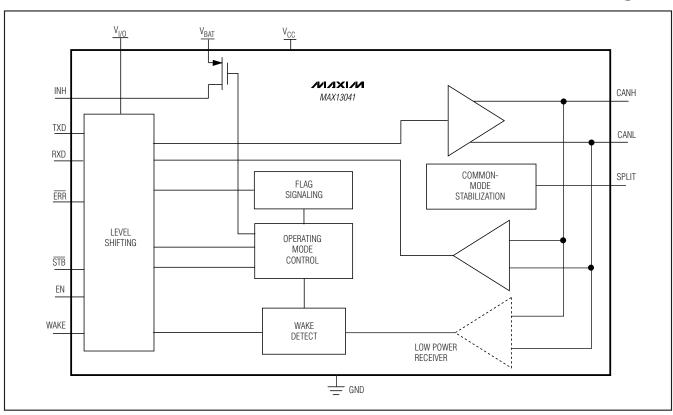

### Functional Diagram

#### **Package Information**

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |

|--------------|--------------|--------------|

| 14 SO        | S14M-7       | 21-0041      |

### Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                              | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------------------------------|------------------|

| 1                  | 11/07            | Changed Absolute Maximum Ratings and Electrical Characteristics sections | 2, 4, 5, 12      |

| 2                  | 12/08            | Added automotive part number                                             | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.