# **Twin SLIC Protector**

Subscriber Line Interface Circuits (SLIC) are highly susceptible to transient voltages, such as lightning and power cross conditions. To minimize this threat, Littelfuse provides this dual-chip, fixed-voltage SLIC protector device.

For specific design criteria, see details in Figure 3.29.

#### **Electrical Parameters**

| Part     | V <sub>DRM</sub><br>Volts | V <sub>S</sub><br>Volts | Vτ    | VF    | I <sub>DRM</sub> | ls    | Ιτ   | lμ    | co |

|----------|---------------------------|-------------------------|-------|-------|------------------|-------|------|-------|----|

| Number * | Pins 1-2, 3-2             |                         | Volts | Volts | μAmps            | mAmps | Amps | mAmps | pF |

| P0641CA2 | 58                        | 77                      | 4     | 5     | 5                | 800   | 1    | 120   | 60 |

| P0721CA2 | 65                        | 88                      | 4     | 5     | 5                | 800   | 1    | 120   | 60 |

| P0901CA2 | 75                        | 98                      | 4     | 5     | 5                | 800   | 1    | 120   | 60 |

| P1101CA2 | 95                        | 130                     | 4     | 5     | 5                | 800   | 1    | 120   | 60 |

| P1701CA2 | 160                       | 200                     | 4     | 5     | 5                | 800   | 1    | 120   | 70 |

<sup>\*</sup> For surge ratings, see table below.

#### General Notes:

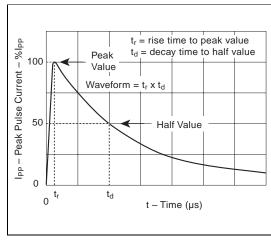

- All measurements are made at an ambient temperature of 25 °C. IPP applies to -40 °C through +85 °C temperature range.

- $\ensuremath{\mathsf{I}_{PP}}$  is a repetitive surge rating and is guaranteed for the life of the product.

- V<sub>DRM</sub> is measured at I<sub>DRM</sub>.

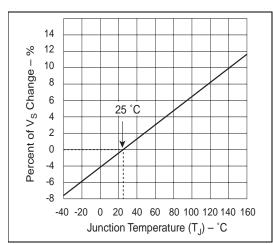

- $V_S$  and  $V_F$  are measured at 100 V/ $\mu s$ .

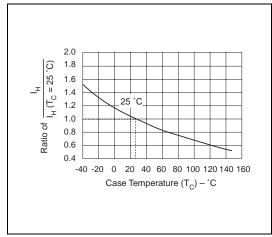

- Special voltage (V<sub>S</sub> and V<sub>DRM</sub>) and holding current (I<sub>H</sub>) requirements are available upon request.

- Off-state capacitance (C<sub>O</sub>) is measured across pins 1-2 or 3-2 at 1 MHz with a 2 V bias. Capacitance across pins 1-3 is approximately half.

- Parallel capacitive loads may affect electrical parameters.

- Compliance with GR 1089 or UL 60950 power cross tests may require special design considerations. Contact the factory for further information

## Surge Ratings (Preliminary Data)

|   | Series | l <sub>PP</sub><br>2x10 μs<br>Amps | I <sub>PP</sub><br>8x20 μs<br>Amps | I <sub>PP</sub><br>10x160 μs<br>Amps | I <sub>PP</sub><br>10x560 μs<br>Amps | I <sub>PP</sub><br>10x1000 μs<br>Amps | I <sub>TSM</sub><br>60 Hz<br>Amps | di/dt<br>Amps/µs |

|---|--------|------------------------------------|------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------|-----------------------------------|------------------|

| ı | Α      | 150                                | 150                                | 90                                   | 50                                   | 45                                    | 20                                | 500              |

### **Thermal Considerations**

| Package           | Symbol        | Parameter                               | Value       | Unit |

|-------------------|---------------|-----------------------------------------|-------------|------|

| Modified DO-214AA | TJ            | Operating Junction Temperature Range    | -40 to +150 | °C   |

| Pin 3             | Ts            | Storage Temperature Range               | -65 to +150 | °C   |

| Pin 1             | $R_{	hetaJA}$ | Thermal Resistance: Junction to Ambient | 85          | °C/W |

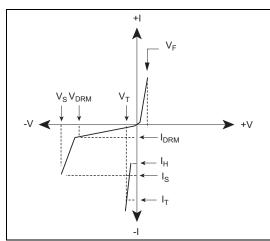

V-I Characteristics

Normalized V<sub>S</sub> Change versus Junction Temperature

$t_{\rm r} \ x \ t_{\rm d}$  Pulse Wave-form

Normalized DC Holding Current versus Case Temperature