## Integrated Device Technology, Inc.

## ICS1893CY-10

Document Type: Data Sheet

Document Stage: Preliminary Release

# 3.3-V 10Base-T/100Base-TX Integrated PHYceiver™

#### General

The ICS1893CY-10 is a low-power, physical-layer device (PHY) that supports the ISO/IEC 10Base-T and 100Base-TX Carrier-Sense Multiple Access/Collision Detection (CSMA/CD) Ethernet standards. The ICS1893CY-10 supports managed or unmanaged node, repeater, and switch applications.

The ICS1893CY-10 is intended for MII, Node applications that require the Auto-MIDIX feature that automatically corrects crossover errors in plant wiring.

The ICS1893CY-10 incorporates digital signal processing (DSP) in its Physical Medium Dependent (PMD) sublayer. As a result, it can transmit and receive data on unshielded twisted-pair (UTP) category 5 cables with attenuation in excess of 24 dB at 100 MHz. With this ICS-patented technology, the ICS1893CY-10 can virtually eliminate errors from killer packets.

The ICS1893CY-10 provides a Serial Management Interface for exchanging command and status information with a Station Management (STA) entity.

The ICS1893CY-10 Media Dependent Interface (MDI) can be configured to provide either half- or full-duplex operation at data rates of 10 MHz or 100 MHz. The MDI configuration can be established manually (with input pins or control register settings) or automatically (using the Auto-Negotiation features). When the ICS1893CY-10 Auto-Negotiation sublayer is enabled, it exchanges technology capability data with its remote link partner and automatically selects the highest-performance operating mode they have in common.

#### **Features**

- Supports category 5 cables with attenuation in excess of 24 dB at 100 MHz

- Fully integrated, DSP-based PMD includes:

- Adaptive equalization and baseline wander correction

- Transmit wave shaping and stream cipher scrambler

- MLT-3 encoder and NRZ/NRZI encoder

- Low-power, 0.35-micron CMOS (typically 400 mW)

- Power-down mode typically 21mW

- Single 3.3-V power supply.

- Single-chip, fully integrated PHY provides PCS, PMA, PMD, and AUTONEG sublayers of IEEE standard

- 10Base-T and 100Base-TX IEEE 802.3 compliant

- Highly configurable design supports:

- Node, repeater, and switch applications

- Managed and unmanaged applications

- 10M or 100M half- and full-duplex modes

- Parallel detection

- Auto-negotiation, with Next Page capabilities

- Auto-MDI/MDIX crossover correction

- MAC/Repeater Interface can be configured as:

- 10M or 100M Media Independent Interface

- 100M Symbol Interface (bypasses the PCS)

- 10M 7-wire Serial Interface

- Clock and crystal supported

- Small Footprint 64-pin Thin Quad Flat Pack (TQFP)

- Available in Industrial Temperature and Lead-Free

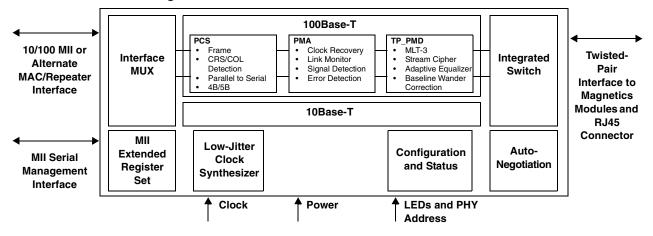

#### ICS1893CY-10 Block Diagram

ICS1893CY-10

Rev 1/07

IDT reserves the right to make changes in the device data identified in this publication without further notice. IDT advises its customers to obtain the latest version of all device data to verify that any information being relied upon by the customer is current and accurate.

| <u>Section</u> | <u>Title</u>                                  |    |

|----------------|-----------------------------------------------|----|

| Revision Hi    | istory                                        | 9  |

| Chapter 1      | Abbreviations and Acronyms                    | 10 |

| Chapter 2      | Conventions and Nomenclature                  | 12 |

| Chapter 3      | Overview of the ICS1893CY-10                  | 14 |

| 3.1            | 100Base-TX Operation                          | 15 |

| 3.2            | 10Base-T Operation                            | 15 |

| Chapter 4      | Operating Modes Overview                      |    |

| 4.1            | Reset Operations                              |    |

| 4.1.1          | General Reset Operations                      |    |

| 4.1.2          | Specific Reset Operations                     |    |

| 4.2            | Power-Down Operations                         |    |

| 4.3            | Automatic Power-Saving Operations             |    |

| 4.4            | Auto-Negotiation Operations                   |    |

| 4.5            | 100Base-TX Operations                         |    |

| 4.6            | 10Base-T Operations                           |    |

| 4.7            | Half-Duplex and Full-Duplex Operations        |    |

| 4.8            | Auto-MDI/MDIX Crossover                       | 22 |

| Chapter 5      | Interface Overviews                           | 23 |

| 5.1            | MII Data Interface                            |    |

| 5.2            | 100M Symbol Interface                         |    |

| 5.3            | 10M Serial Interface                          |    |

| 5.4            | Serial Management Interface                   |    |

| 5.5            | Twisted-Pair Interface                        |    |

| 5.5.1          | Twisted-Pair Interface                        |    |

| 5.6            | Clock Reference Interface                     |    |

| 5.7            | Configuration Interface                       | 33 |

| 5.8            | Status Interface                              | 34 |

| Chapter 6      | Functional Blocks                             | 36 |

| 6.1            | Functional Block: Media Independent Interface |    |

| 6.2            | Functional Block: Auto-Negotiation            |    |

| 6.2.1          | Auto-Negotiation General Process              |    |

| 6.2.2          | Auto-Negotiation: Parallel Detection          |    |

| 6.2.3          | Auto-Negotiation: Remote Fault Signaling      |    |

| 6.2.4          | Auto-Negotiation: Reset and Restart           | 40 |

| 625            | Auto-Negotiation: Progress Monitor            | 41 |

| <u>Section</u> | <u>Title</u>                                              | <u>Page</u> |

|----------------|-----------------------------------------------------------|-------------|

| 6.3            | Functional Block: 100Base-X PCS and PMA Sublayers         | 42          |

| 6.3.1          | PCS Sublayer                                              | 42          |

| 6.3.2          | PMA Sublayer                                              | 43          |

| 6.3.3          | PCS/PMA Transmit Modules                                  | 43          |

| 6.3.4          | PCS/PMA Receive Modules                                   | 44          |

| 6.3.5          | PCS Control Signal Generation                             | 45          |

| 6.3.6          | 4B/5B Encoding/Decoding                                   |             |

| 6.4            | Functional Block: 100Base-TX TP-PMD Operations            |             |

| 6.4.1          | 100Base-TX Operation: Stream Cipher Scrambler/Descrambler | 46          |

| 6.4.2          | 100Base-TX Operation: MLT-3 Encoder/Decoder               |             |

| 6.4.3          | 100Base-TX Operation: DC Restoration                      | 46          |

| 6.4.4          | 100Base-TX Operation: Adaptive Equalizer                  |             |

| 6.4.5          | 100Base-TX Operation: Twisted-Pair Transmitter            | 47          |

| 6.4.6          | 100Base-TX Operation: Twisted-Pair Receiver               |             |

| 6.5            | Functional Block: 10Base-T Operations                     |             |

| 6.5.1          | 10Base-T Operation: Manchester Encoder/Decoder            |             |

| 6.5.2          | 10Base-T Operation: Clock Synthesis                       |             |

| 6.5.3          | 10Base-T Operation: Clock Recovery                        |             |

| 6.5.4          | 10Base-T Operation: Idle                                  |             |

| 6.5.5          | 10Base-T Operation: Link Monitor                          |             |

| 6.5.6          | 10Base-T Operation: Smart Squelch                         |             |

| 6.5.7          | 10Base-T Operation: Carrier Detection                     |             |

| 6.5.8          | 10Base-T Operation: Collision Detection                   |             |

| 6.5.9          | 10Base-T Operation: Jabber                                |             |

| 6.5.10         | 10Base-T Operation: SQE Test                              |             |

| 6.5.11         | 10Base-T Operation: Twisted-Pair Transmitter              |             |

| 6.5.12         | 10Base-T Operation: Twisted-Pair Receiver                 |             |

| 6.5.13         | 10Base-T Operation: Auto Polarity Correction              |             |

| 6.5.14         | 10Base-T Operation: Isolation Transformer                 |             |

| 6.6            | Functional Block: Management Interface                    |             |

| 6.6.1          | Management Register Set Summary                           |             |

| 6.6.2          | Management Frame Structure                                | 53          |

| <u>Section</u> | <u>Title</u>                              |    |

|----------------|-------------------------------------------|----|

| Chapter 7      | Management Register Set                   | 56 |

| 7.1            | Introduction to Management Register Set   |    |

| 7.1.1          | Management Register Set Outline           |    |

| 7.1.2          | Management Register Bit Access            |    |

| 7.1.3          | Management Register Bit Default Values    |    |

| 7.1.4          | Management Register Bit Special Functions | 59 |

| 7.2            | Register 0: Control Register              | 60 |

| 7.2.1          | Reset (bit 0.15)                          | 60 |

| 7.2.2          | Loopback Enable (bit 0.14)                | 61 |

| 7.2.3          | Data Rate Select (bit 0.13)               | 61 |

| 7.2.4          | Auto-Negotiation Enable (bit 0.12)        | 61 |

| 7.2.5          | Low Power Mode (bit 0.11)                 | 62 |

| 7.2.6          | Isolate (bit 0.10)                        |    |

| 7.2.7          | Restart Auto-Negotiation (bit 0.9)        | 62 |

| 7.2.8          | Duplex Mode (bit 0.8)                     |    |

| 7.2.9          | Collision Test (bit 0.7)                  |    |

| 7.2.10         | IEEE Reserved Bits (bits 0.6:0)           | 63 |

| 7.3            | Register 1: Status Register               | 64 |

| 7.3.1          | 100Base-T4 (bit 1.15)                     | 64 |

| 7.3.2          | 100Base-TX Full Duplex (bit 1.14)         | 65 |

| 7.3.3          | 100Base-TX Half Duplex (bit 1.13)         | 65 |

| 7.3.4          | 10Base-T Full Duplex (bit 1.12)           |    |

| 7.3.5          | 10Base-T Half Duplex (bit 1.11)           | 65 |

| 7.3.6          | IEEE Reserved Bits (bits 1.10:7)          |    |

| 7.3.7          | MF Preamble Suppression (bit 1.6)         |    |

| 7.3.8          | Auto-Negotiation Complete (bit 1.5)       | 66 |

| 7.3.9          | Remote Fault (bit 1.4)                    |    |

| 7.3.10         | Auto-Negotiation Ability (bit 1.3)        | 67 |

| 7.3.11         | Link Status (bit 1.2)                     |    |

| 7.3.12         | Jabber Detect (bit 1.1)                   |    |

| 7.3.13         | Extended Capability (bit 1.0)             | 68 |

| 7.4            | Register 2: PHY Identifier Register       | 69 |

| <u>Section</u> | <u>Title</u>                                                         | <u>Page</u> |

|----------------|----------------------------------------------------------------------|-------------|

| 7.5            | Register 3: PHY Identifier Register                                  | 71          |

| 7.5.1          | OUI bits 19-24 (bits 3.15:10)                                        | 71          |

| 7.5.2          | Manufacturer's Model Number (bits 3.9:4)                             | 71          |

| 7.5.3          | Revision Number (bits 3.3:0)                                         | 72          |

| 7.6            | Register 4: Auto-Negotiation Register                                |             |

| 7.6.1          | Next Page (bit 4.15)                                                 |             |

| 7.6.2          | IEEE Reserved Bit (bit 4.14)                                         |             |

| 7.6.3          | Remote Fault (bit 4.13)                                              |             |

| 7.6.4          | IEEE Reserved Bits (bits 4.12:10)                                    |             |

| 7.6.5          | Technology Ability Field (bits 4.9:5)                                |             |

| 7.6.6          | Selector Field (Bits 4.4:0)                                          | 75          |

| 7.7            | Register 5: Auto-Negotiation Link Partner Ability Register           |             |

| 7.7.1          | Next Page (bit 5.15)                                                 |             |

| 7.7.2          | Acknowledge (bit 5.14)                                               | //          |

| 7.7.3          | Remote Fault (bit 5.13)                                              | //          |

| 7.7.4          | Technology Ability Field (bits 5.12:5)                               |             |

| 7.7.5          | Selector Field (bits 5.4:0)                                          | //          |

| 7.8            | Register 6: Auto-Negotiation Expansion Register                      |             |

| 7.8.1          | IEEE Reserved Bits (bits 6.15:5)                                     |             |

| 7.8.2          | Parallel Detection Fault (bit 6.4)                                   |             |

| 7.8.3<br>7.8.4 | Link Partner Next Page Able (bit 6.3)  Next Page Able (bit 6.2)      |             |

| 7.8.4<br>7.8.5 | Page Received (bit 6.1)                                              |             |

| 7.8.6          | Link Partner Auto-Negotiation Able (bit 6.0)                         |             |

| 7.9            | Register 7: Auto-Negotiation Next Page Transmit Register             | 80          |

| 7.9.1          | Next Page (bit 7.15)                                                 |             |

| 7.9.2          | IEEE Reserved Bit (bit 7.14)                                         |             |

| 7.9.3          | Message Page (bit 7.13)                                              |             |

| 7.9.4          | Acknowledge 2 (bit 7.12)                                             |             |

| 7.9.5          | Toggle (bit 7.11)                                                    |             |

| 7.9.6          | Message Code Field / Unformatted Code Field (bits 7.10:0)            |             |

| 7.10           | Register 8: Auto-Negotiation Next Page Link Partner Ability Register | 82          |

| 7.10.1         | Next Page (bit 8.15)                                                 |             |

| 7.10.2         | IEEE Reserved Bit (bit 8.14)                                         |             |

| 7.10.3         | Message Page (bit 8.13)                                              |             |

| 7.10.4         | Acknowledge 2 (bit 8.12)                                             |             |

| 7.10.5         | Message Code Field / Unformatted Code Field (bits 8.10:0)            |             |

| <u>Section</u> | <u>Title</u>                                      | <u>Page</u> |

|----------------|---------------------------------------------------|-------------|

| 7.11           | Register 16: Extended Control Register            | 84          |

| 7.11.1         | Command Override Write Enable (bit 16.15)         |             |

| 7.11.2         | ICS Reserved (bits 16.14:11)                      | 85          |

| 7.11.3         | PHY Address (bits 16.10:6)                        |             |

| 7.11.4         | Stream Cipher Scrambler Test Mode (bit 16.5)      | 85          |

| 7.11.5         | ICS Reserved (bit 16.4)                           |             |

| 7.11.6         | NRZ/NRZI Encoding (bit 16.3)                      | 85          |

| 7.11.7         | Invalid Error Code Test (bit 16.2)                | 86          |

| 7.11.8         | ICS Reserved (bit 16.1)                           | 86          |

| 7.11.9         | Stream Cipher Disable (bit 16.0)                  | 86          |

| 7.12           | Register 17: Quick Poll Detailed Status Register  |             |

| 7.12.1         | Data Rate (bit 17.15)                             | 88          |

| 7.12.2         | Duplex (bit 17.14)                                |             |

| 7.12.3         | Auto-Negotiation Progress Monitor (bits 17.13:11) |             |

| 7.12.4         | 100Base-TX Receive Signal Lost (bit 17.10)        |             |

| 7.12.5         | 100Base PLL Lock Error (bit 17.9)                 |             |

| 7.12.6         | False Carrier (bit 17.8)                          |             |

| 7.12.7         | Invalid Symbol (bit 17.7)                         |             |

| 7.12.8         | Halt Symbol (bit 17.6)                            |             |

| 7.12.9         | Premature End (bit 17.5)                          |             |

| 7.12.10        | Auto-Negotiation Complete (bit 17.4)              |             |

| 7.12.11        | 100Base-TX Signal Detect (bit 17.3)               |             |

| 7.12.12        | Jabber Detect (bit 17.2)                          |             |

| 7.12.13        | Remote Fault (bit 17.1)                           |             |

| 7.12.14        | Link Status (bit 17.0)                            | 91          |

| 7.13           | Register 18: 10Base-T Operations Register         |             |

| 7.13.1         | Remote Jabber Detect (bit 18.15)                  |             |

| 7.13.2         | Polarity Reversed (bit 18.14)                     |             |

| 7.13.3         | ICS Reserved (bits 18.13:6)                       |             |

| 7.13.4         | Jabber Inhibit (bit 18.5)                         |             |

| 7.13.5         | ICS Reserved (bit 18.4)                           |             |

| 7.13.6         | Auto Polarity Inhibit (bit 18.3)                  |             |

| 7.13.7         | SQE Test Inhibit (bit 18.2)                       |             |

| 7.13.8         | Link Loss Inhibit (bit 18.1)                      |             |

| 7.13.9         | Sauelch Inhibit (bit 18.0)                        | 94          |

| <u>Section</u>               | <u>Title</u>                                                  | <u>Page</u> |

|------------------------------|---------------------------------------------------------------|-------------|

| 7.14                         | Register 19: Extended Control Register 2                      | 95          |

| 7.14.1                       | Node/Repeater Configuration (bit 19.15)                       | 96          |

| 7.14.2                       | Hardware/Software Priority Status (bit 19.14)                 |             |

| 7.14.3                       | Remote Fault (bit 19.13)                                      |             |

| 7.14.4                       | ICS Reserved (bits 19.12:8)                                   |             |

| 7.14.5                       | Auto-MDI/MDIX (bits 19. 9:8) (New)                            |             |

| 7.14.6                       | Twisted Pair Tri-State Enable, TPTRI (bit 19.7)               |             |

| 7.14.7                       | ICS Reserved (bits 19.6:1)                                    |             |

| 7.14.8                       | Automatic 100Base-TX Power-Down (bit 19.0)                    |             |

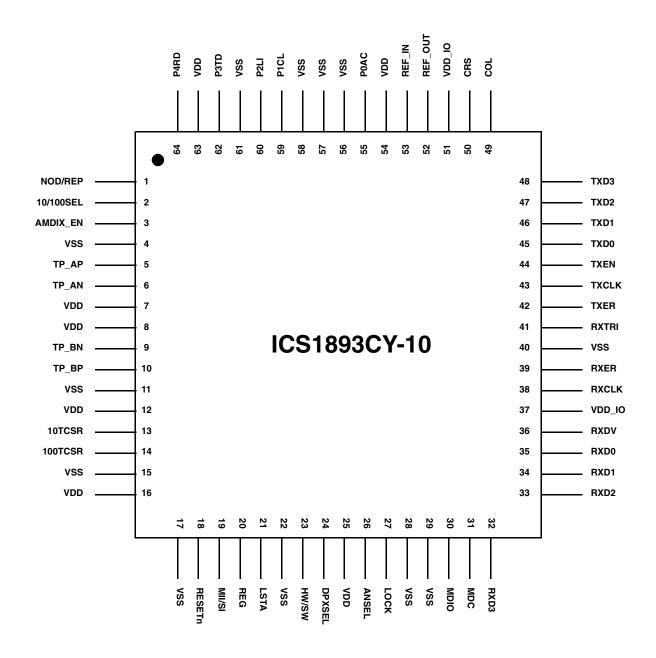

| Chapter 8                    | Pin Diagram, Listings, and Descriptions                       |             |

| 8.1                          | ICS1893CY-10 Pin Diagram                                      |             |

| 8.2                          | ICS1893CY-10 Pin Listings                                     |             |

| 8.3                          | ICS1893CY-10 Pin Descriptions                                 |             |

| 8.3.1<br>8.3.2               | Transformer Interface Pins                                    |             |

| 8.3.3                        | Configuration Pins                                            |             |

| 8.3.4                        | MAC/Repeater Interface Pins                                   |             |

| 8.3.5                        | Reserved Pins                                                 |             |

| 8.3.6                        | Ground and Power Pins                                         |             |

| <b>Chapter 9</b> 9.1 9.2 9.3 | DC and AC Operating Conditions                                | 115<br>115  |

| 9.4                          | DC Operating Characteristics                                  |             |

| 9.4.1                        | DC Operating Characteristics for Supply Current               |             |

| 9.4.2                        | DC Operating Characteristics for TTL Inputs and Outputs       |             |

| 9.4.3                        | DC Operating Characteristics for REF_IN                       |             |

| 9.4.4                        | DC Operating Characteristics for Media Independent Interface  |             |

| 9.5                          | Timing Diagrams                                               |             |

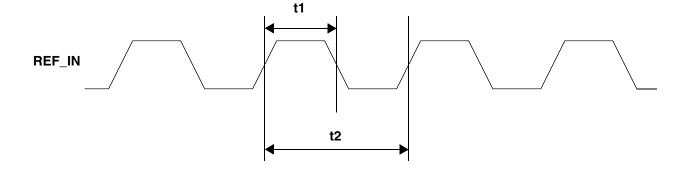

| 9.5.1                        | Timing for Clock Reference In (REF_IN) Pin                    |             |

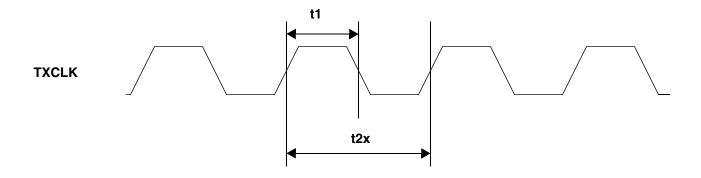

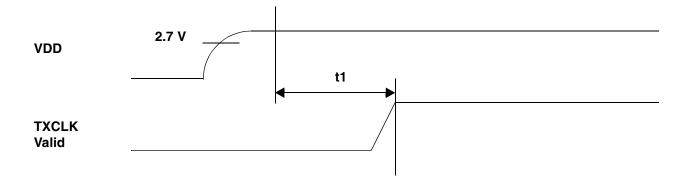

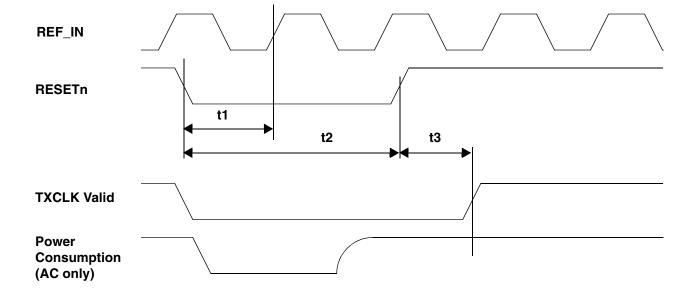

| 9.5.2                        | Timing for Transmit Clock (TXCLK) Pins                        |             |

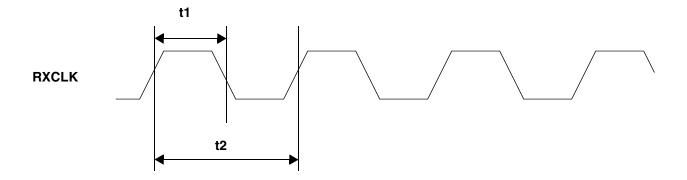

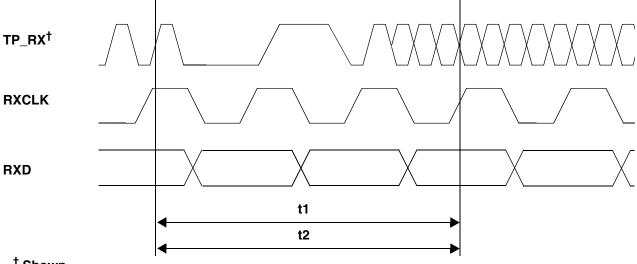

| 9.5.3                        | Timing for Receive Clock (RXCLK) Pins                         | 121         |

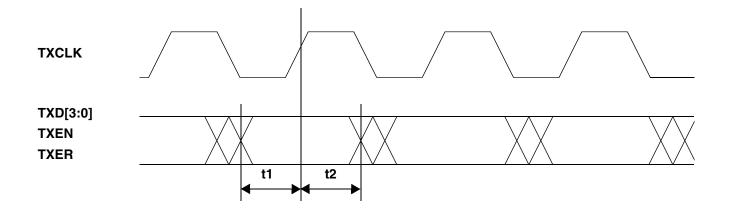

| 9.5.4                        | 100M MII / 100M Stream Interface: Synchronous Transmit Timing | 122         |

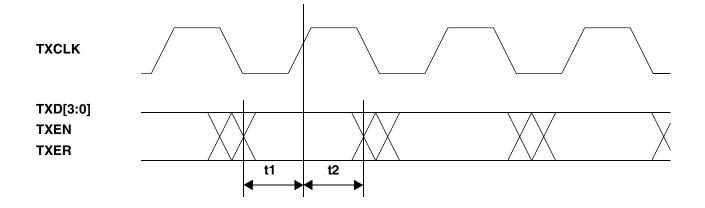

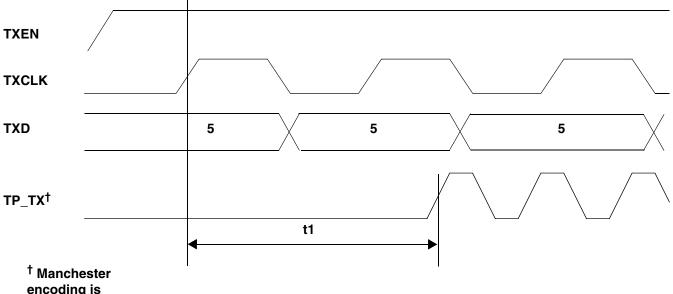

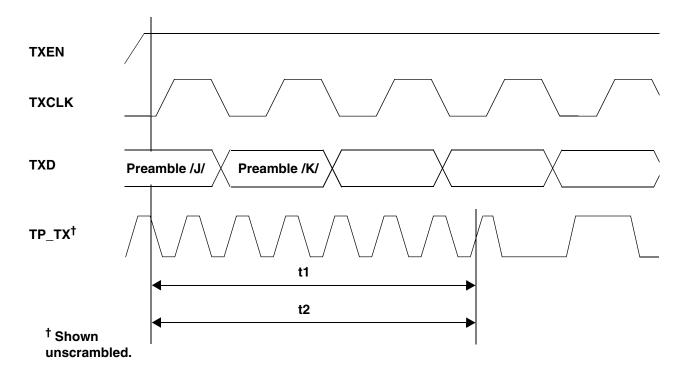

| 9.5.5                        | 10M MII: Synchronous Transmit Timing                          |             |

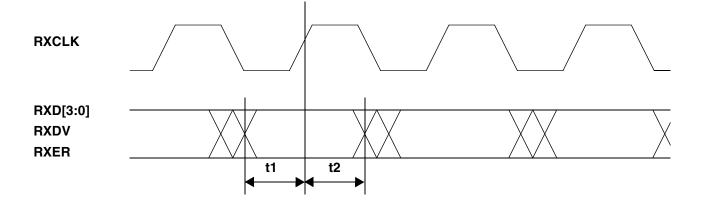

| 9.5.6                        | MII / 100M Stream Interface: Synchronous Receive Timing       |             |

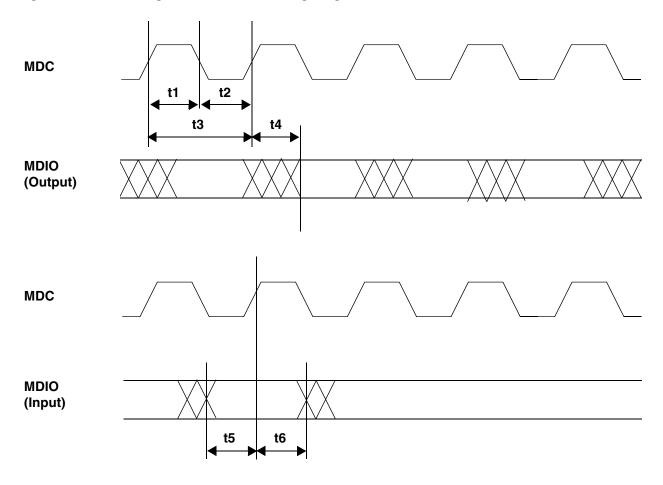

| 9.5.7                        | MII Management Interface Timing                               |             |

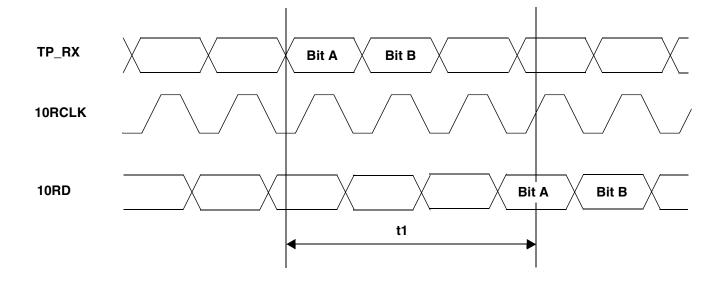

| 9.5.8                        | 10M Serial Interface: Receive Latency                         | 126         |

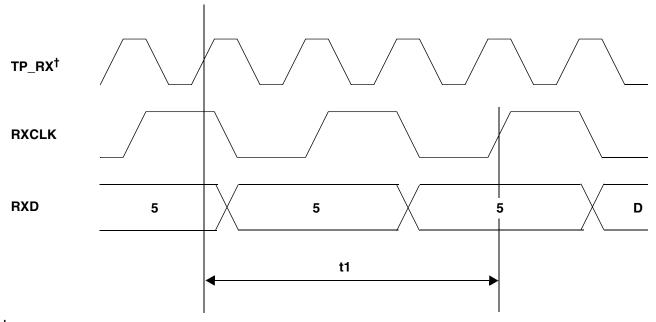

| 9.5.9                        | 10M Media Independent Interface: Receive Latency              | 127         |

| <b>Section</b> | <u>Title</u>                                                            | <u>Page</u> |

|----------------|-------------------------------------------------------------------------|-------------|

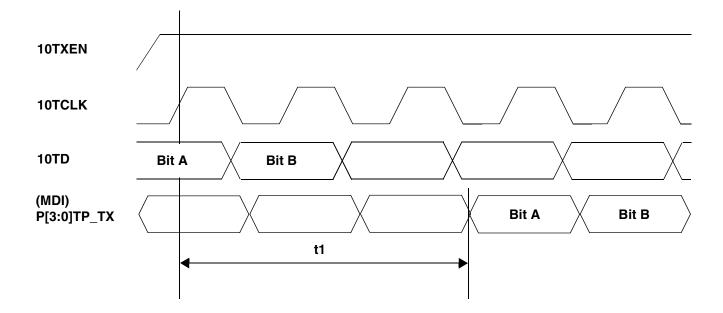

| 9.5.10         | 10M Serial Interface: Transmit Latency                                  | 128         |

| 9.5.11         | 10M Media Independent Interface: Transmit Latency                       | 129         |

| 9.5.12         | MII / 100M Stream Interface: Transmit Latency                           |             |

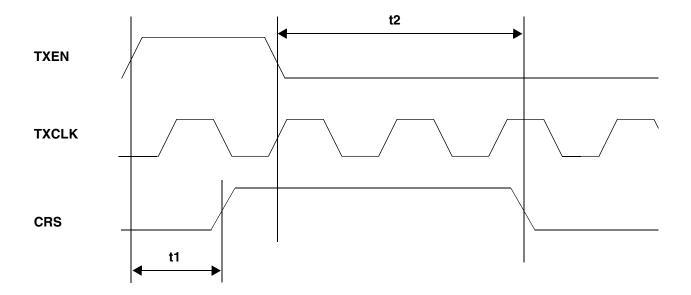

| 9.5.13         | 100M MII: Carrier Assertion/De-Assertion (Half-Duplex Transmission)     | 131         |

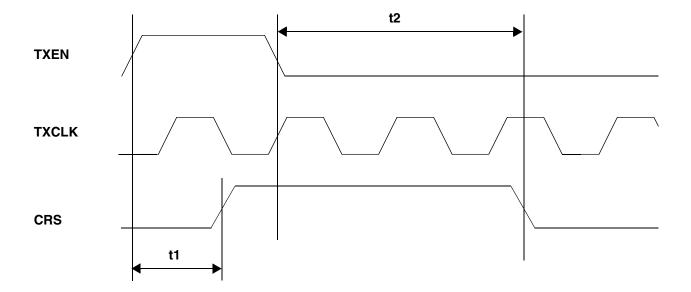

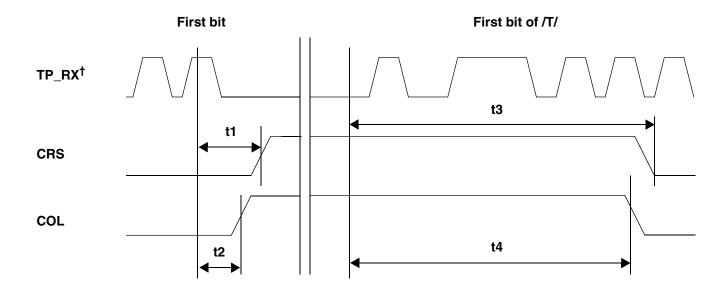

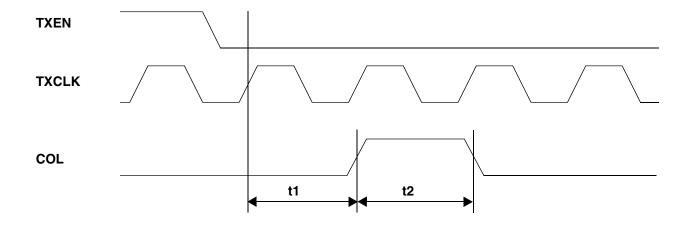

| 9.5.14         | 10M MII: Carrier Assertion/De-Assertion (Half-Duplex Transmission)      | 132         |

| 9.5.15         | 100M MII / 100M Stream Interface: Receive Latency                       | 133         |

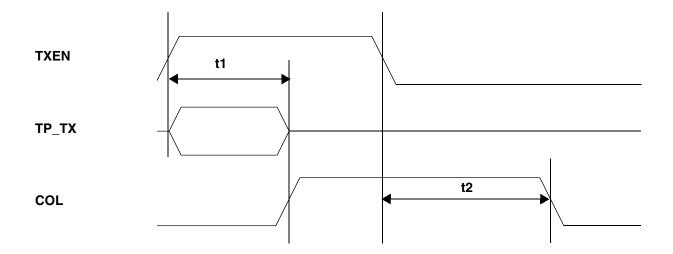

| 9.5.16         | 100M Media Dependent Interface: Input-to-Carrier Assertion/De-Assertion | 134         |

| 9.5.17         | Reset: Power-On Reset                                                   | 135         |

| 9.5.18         | Reset: Hardware Reset and Power-Down                                    | 136         |

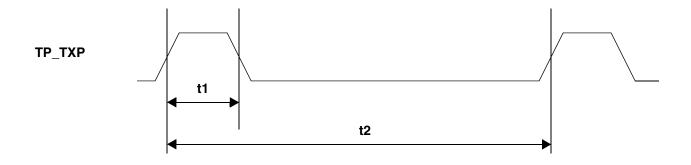

| 9.5.19         | 10Base-T: Heartbeat Timing (SQE)                                        | 137         |

| 9.5.20         | 10Base-T: Jabber Timing                                                 |             |

| 9.5.21         | 10Base-T: Normal Link Pulse Timing                                      | 139         |

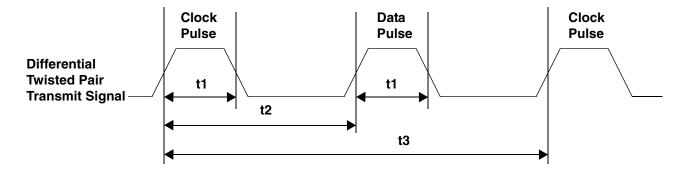

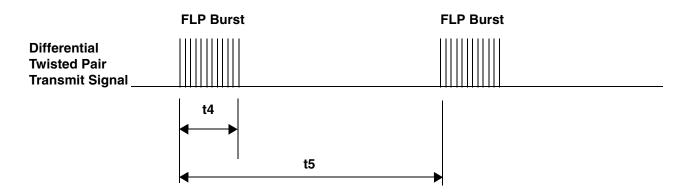

| 9.5.22         | Auto-Negotiation Fast Link Pulse Timing                                 | 140         |

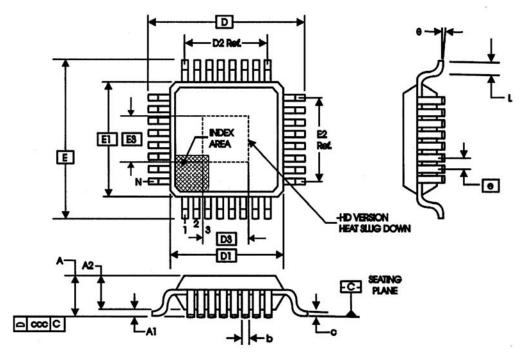

| Chapter 10     | Physical Dimensions of ICS1893CY-10 Package                             | 141         |

| Chapter 11     | Ordering Information                                                    | 142         |

# **Revision History**

- The initial release of this document, Rev A, is dated November 2006

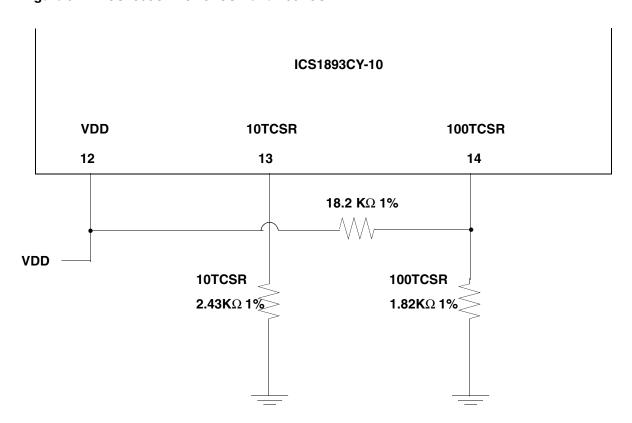

- Rev 1/07 changed resistor values on Figure 9-1.

# **Chapter 1 Abbreviations and Acronyms**

Table 1-1 lists and interprets the abbreviations and acronyms used throughout this data sheet.

Table 1-1. Abbreviations and Acronyms

| Abbreviation /<br>Acronym | Interpretation                                                                      |  |

|---------------------------|-------------------------------------------------------------------------------------|--|

| 4B/5B                     | 4-Bit / 5-Bit Encoding/Decoding                                                     |  |

| ANSI                      | American National Standards Institute                                               |  |

| CMOS                      | complimentary metal-oxide semiconductor                                             |  |

| CSMA/CD                   | Carrier Sense Multiple Access with Collision Detection                              |  |

| CW                        | Command Override Write                                                              |  |

| DSP                       | digital signal processing                                                           |  |

| ESD                       | End-of-Stream Delimiter                                                             |  |

| FDDI                      | Fiber Distributed Data Interface                                                    |  |

| FLL                       | frequency-locked loop                                                               |  |

| FLP                       | Fast Link Pulse                                                                     |  |

| IDL                       | A 'dead' time on the link following a 10Base-T packet, not to be confused with idle |  |

| IEC                       | International Electrotechnical Commission                                           |  |

| IEEE                      | Institute of Electrical and Electronic Engineers                                    |  |

| ISO                       | International Standards Organization                                                |  |

| LH                        | Latching High                                                                       |  |

| LL                        | Latching Low                                                                        |  |

| LMX                       | Latching Maximum                                                                    |  |

| MAC                       | Media Access Control                                                                |  |

| Max.                      | maximum                                                                             |  |

| Mbps                      | Megabits per second                                                                 |  |

| MDI                       | Media Dependent Interface                                                           |  |

| MF                        | Management Frame                                                                    |  |

| MII                       | Media Independent Interface                                                         |  |

| Min.                      | minimum                                                                             |  |

| MLT-3                     | Multi-Level Transition Encoding (3 Levels)                                          |  |

| N/A                       | Not Applicable                                                                      |  |

| NLP                       | Normal Link Pulse                                                                   |  |

| No.                       | Number                                                                              |  |

| NRZ                       | Not Return to Zero                                                                  |  |

| NRZI                      | Not Return to Zero, Invert on one                                                   |  |

| OSI                       | Open Systems Interconnection                                                        |  |

# ICS1893CY-10 - Release

Table 1-1. Abbreviations and Acronyms (Continued)

| Abbreviation /<br>Acronym | Interpretation                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OUI                       | Organizationally Unique Identifier                                                                                                                                                                                                                                                                                                                                                                                     |  |

| PCS                       | Physical Coding sublayer                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PHY                       | The ICS1893CY-10 is a physical-layer device, also referred to as a 'PHY' or 'PHYceiver'.                                                                                                                                                                                                                                                                                                                               |  |

| PLL                       | phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| PMA                       | Physical Medium Attachment                                                                                                                                                                                                                                                                                                                                                                                             |  |

| PMD                       | Physical Medium Dependent                                                                                                                                                                                                                                                                                                                                                                                              |  |

| ppm                       | parts per million                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| QFP                       | quad flat pack                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| RO                        | read only                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| R/W                       | read/write                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| R/W0                      | read/write zero                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| SC                        | self-clearing                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SF                        | Special Functions                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SFD                       | Start-of-Frame Delimiter                                                                                                                                                                                                                                                                                                                                                                                               |  |

| SI                        | Stream Interface, Serial Interface, or Symbol Interface.  With reference to the MII/SI pin, the acronym 'SI' has multiple meanings.  • Generically, SI means 'Stream Interface', and is documented as such in this data sheet.  • However, when the MAC/Repeater Interface is configured for:  – 10M operations, SI is an acronym for 'Serial Interface'.  – 100M operations, SI is an acronym for 'Symbol Interface'. |  |

| SQE                       | Signal Quality Error                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| SSD                       | Start-of-Stream Delimiter                                                                                                                                                                                                                                                                                                                                                                                              |  |

| STA                       | Station Management Entity                                                                                                                                                                                                                                                                                                                                                                                              |  |

| STP                       | shielded twisted pair                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TAF                       | Technology Ability Field                                                                                                                                                                                                                                                                                                                                                                                               |  |

| TP-PMD                    | Twisted-Pair Physical Layer Medium Dependent                                                                                                                                                                                                                                                                                                                                                                           |  |

| Тур.                      | typical                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| UTP                       | unshielded twisted pair                                                                                                                                                                                                                                                                                                                                                                                                |  |

# **Chapter 2 Conventions and Nomenclature**

Table 2-1 lists and explains the conventions and nomenclature used throughout this data sheet.

Table 2-1. Conventions and Nomenclature

| Item                  | Convention / Nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bits                  | <ul> <li>A bit in a register is identified using the format 'register.bit'. For example, bit 0.15 is bit 15 of register 0.</li> <li>When a colon is used with bits, it indicates the range of bits. For example, bits 1.15:11 are bits 15, 14, 13, 12, and 11 of register 1.</li> <li>For a range of bits, the order is always from the most-significant bit to the least-significant bit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Code groups           | Within this table, see the item 'Symbols'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Colon (:)             | Within this table, see these items:  • 'Bits'  • 'Pin (or signal) names'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Numbers               | <ul> <li>As a default, all numbers use the decimal system (that is, base 10) unless followed by a lowercase letter. A string of numbers followed by a lowercase letter:         <ul> <li>A 'b' represents a binary (base 2) number</li> <li>An 'h' represents a hexadecimal (base 16) number</li> <li>An 'o' represents an octal (base 8) number</li> </ul> </li> <li>All numerical references to registers use decimal notation (and not hexadecimal).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Pin (or signal) names | <ul> <li>All pin or signal names are provided in capital letters.</li> <li>A pin name that includes a forward slash '/' is a multi-function, configuration pin. These pins provide the ability to select between two ICS1893CY-10 functions. The name provided: <ul> <li>Before the '/' indicates the pin name and function when the signal level on the pin is logic zero.</li> <li>After the '/' indicates the pin name and function when the signal level on the pin is logic one.</li> </ul> </li> <li>For example, the HW/SW pin selects between Hardware (HW) mode and Software (SW) mode. When the signal level on the HW/SW pin is logic: <ul> <li>Zero, the ICS1893CY-10 Hardware mode is selected.</li> <li>One, the ICS1893CY-10 Software mode is selected.</li> </ul> </li> <li>An 'n' appended to the end of a pin name or signal name (such as RESETn) indicates an active-low operation.</li> <li>When a colon is used with pin or signal names, it indicates a range. For example, TXD[3:0] represents pins/signals TXD3, TXD2, TXD1, and TXD0.</li> <li>When pin name abbreviations are spelled out, words in parentheses indicate additional description that is not part of the pin name abbreviation.</li> </ul> |  |  |

| Registers             | <ul> <li>A bit in a register is identified using the format 'register.bit'. For example, bit 0.15 is bit 15 of register 0.</li> <li>All numerical references to registers use decimal notation (and not hexadecimal).</li> <li>When register name abbreviations are spelled out, words in parentheses indicate additional description that is not part of the register name abbreviation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

# ICS1893CY-10 - Release

Table 2-1. Conventions and Nomenclature (Continued)

| Item                                        | Convention / Nomenclature                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal references                           | <ul> <li>When referring to signals, the terms: <ul> <li>'FALSE', 'low', or 'zero' represent signals that are logic zero.</li> <li>'TRUE', 'high', or 'one' represent signals that are logic one.</li> </ul> </li> <li>Chapter 9, "DC and AC Operating Conditions" defines the electrical specifications for 'logic zero' and 'logic one' signals.</li> </ul> |  |

| Symbols                                     | <ul> <li>In this data sheet, code group names are referred to as 'symbols' and they are shown between '/' (slashes). For example, the symbol /J/ represents the first half of the Start-of-Stream Delimiter (SSD1).</li> <li>Symbol sequences are shown in succession. For example, /I/J/K/ represents an IDLE followed by the SSD.</li> </ul>               |  |

| Terms: 'set', 'active', 'asserted',         | The terms 'set', 'active', and 'asserted' are synonymous. They do not necessarily infer logic one. (For example, an active-low signal can be set to logic zero.)                                                                                                                                                                                             |  |

| Terms: 'cleared', 'de-asserted', 'inactive' | The terms 'cleared', 'inactive', and 'de-asserted' are synonymous.  They do not necessarily infer logic zero.                                                                                                                                                                                                                                                |  |

| Terms:<br>'twisted-pair receiver'           | In reference to the ICS1893CY-10, the term 'Twisted-Pair Receiver' refers to the set of Twisted-Pair Receive output pins (TP_RXP and TP_RXN).                                                                                                                                                                                                                |  |

| Terms: 'twisted-pair transmitter'           | In reference to the ICS1893CY-10, the term 'Twisted-Pair Transmitter' refers to the set of Twisted-Pair Transmit output pins (TP_TXP and TP_TXN).                                                                                                                                                                                                            |  |

# Chapter 3 Overview of the ICS1893CY-10

The ICS1893CY-10 is a stream processor. During data transmission, it accepts sequential nibbles from its MAC (Media Access Control)/Repeater Interface, converts them into a serial bit stream, encodes them, and transmits them over the medium through an external isolation transformer. When receiving data, the ICS1893CY-10 converts and decodes a serial bit stream (acquired from an isolation transformer that interfaces with the medium) into sequential nibbles. It subsequently presents these nibbles to its MAC/Repeater Interface.

The ICS1893CY-10 implements the OSI model's physical layer, consisting of the following, as defined by the ISO/IEC 8802-3 standard:

- Physical Coding sublayer (PCS)

- Physical Medium Attachment sublayer (PMA)

- Physical Medium Dependent sublayer (PMD)

- Auto-Negotiation sublayer

The ICS1893CY-10 is transparent to the next layer of the OSI model, the link layer. The link layer has two sublayers: the Logical Link Control sublayer and the MAC sublayer. The ICS1893CY-10 can interface directly to the MAC and offers multiple, configurable modes of operation. Alternately, this configurable interface can be connected to a repeater, which extends the physical layer of the OSI model.

The ICS1893CY-10 transmits framed packets acquired from its MAC/Repeater Interface and receives encapsulated packets from another PHY, which it translates and presents to its MAC/Repeater Interface.

**Note:** As per the ISO/IEC standard, the ICS1893CY-10 does not affect, nor is it affected by, the underlying structure of the MAC/repeater frame it is conveying.

### 3.1 100Base-TX Operation

During 100Base-TX data transmission, the ICS1893CY-10 accepts packets from a MAC/repeater and inserts Start-of-Stream Delimiters (SSDs) and End-of-Stream Delimiters (ESDs) into the data stream. The ICS1893CY-10 encapsulates each MAC/repeater frame, including the preamble, with an SSD and an ESD. As per the ISO/IEC Standard, the ICS1893CY-10 replaces the first octet of each MAC preamble with an SSD and appends an ESD to the end of each MAC/repeater frame.

When receiving data from the medium, the ICS1893CY-10 removes each SSD and replaces it with the pre-defined preamble pattern before presenting the nibbles to its MAC/Repeater Interface. When the ICS1893CY-10 encounters an ESD in the received data stream, signifying the end of the frame, it ends the presentation of nibbles to its MAC/Repeater Interface. Therefore, the local MAC/repeater receives an unaltered copy of the transmitted frame sent by the remote MAC/repeater.

During periods when MAC frames are being neither transmitted nor received, the ICS1893CY-10 signals and detects the IDLE condition on the Link Segment. In the 100Base-TX mode, the ICS1893CY-10 transmit channel sends a continuous stream of scrambled ones to signify the IDLE condition. Similarly, the ICS1893CY-10 receive channel continually monitors its data stream and looks for a pattern of scrambled ones. The results of this signaling and monitoring provide the ICS1893CY-10 with the means to establish the integrity of the Link Segment between itself and its remote link partner and inform its Station Management Entity (STA) of the link status.

For 100M data transmission, the ICS1893CY-10 MAC/Repeater Interface can be configured to provide either a 100M Media Independent Interface (MII) or a 100M Symbol Interface. With the Symbol Interface configuration, the data stream bypasses the ICS1893CY-10 Physical Coding sublayer (PCS). In addition:

- 1. The ICS1893CY-10 shifts the responsibility of performing the 4B/5B translation to the MAC/repeater. As a result, the requirement is for a 5-bit data path between the MAC/repeater and the ICS1893CY-10.

- 2. The latency through the ICS1893CY-10 is reduced. (The ICS1893CY-10 provides this 100M Symbol Interface primarily for repeater applications for which latency is a critical performance parameter.)

### 3.2 10Base-T Operation

During 10Base-T data transmission, the ICS1893CY-10 inserts only the IDL delimiter into the data stream. The ICS1893CY-10 appends the IDL delimiter to the end of each MAC frame. However, since the 10Base-T preamble already has a Start-of-Frame delimiter (SFD), it is not required that the ICS1893CY-10 insert an SSD-like delimiter.

When receiving data from the medium (such as a twisted-pair cable), the ICS1893CY-10 uses the preamble to synchronize its receive clock. When the ICS1893CY-10 receive clock establishes lock, it presents the preamble nibbles to its MAC/Repeater Interface. The 10M MAC/Repeater Interface can be configured as either a 10M MII, a 10M Serial Interface, or a Link Pulse Interface.

In 10M operations, during periods when MAC frames are being neither transmitted nor received, the ICS1893CY-10 signals and detects Normal Link Pulses. This action allows the integrity of the Link Segment with the remote link partner to be established and then reported to the ICS1893CY-10's STA.

# Chapter 4 Operating Modes Overview

The ICS1893CY-10 operating modes and interfaces are configurable with one of two methods. The HW/SW (hardware/software) pin determines which method the ICS1893CY-10 is to use, either its hardware pins or its register bits. When the HW/SW bit is logic zero the ICS1893CY-10 is in hardware mode. In hardware mode, the hardware pins have priority over the internal registers for establishing the configuration settings of the ICS1893CY-10. When the HW/SW bit is logic one the ICS1893CY-10 is in software mode. In software mode, the internal register bits have priority over the hardware pins for establishing the configuration settings of the ICS1893CY-10. The register bits are typically controlled from software.

The ICS1893CY-10 register bits are accessible through a standard MII (Media Independent Interface) Serial Management Port. Even when the ICS1893CY-10 MAC/Repeater Interface is not supporting the standard MII Data Interface, access to the Serial Management Port is provided (that is, operation of the Serial Management Port is independent of the MAC/Repeater Interface configuration).

The ICS1893CY-10 provides a number of configuration functions to support a variety of operations. For example, the MAC/Repeater Interface can be configured to operate as a 10M MII, a 100M MII, a 100M Symbol Interface, a 10M Serial Interface. The protocol on the Medium Dependent Interface (MDI) can be configured to support either 10M or 100M operations in either half-duplex or full-duplex modes.

The ICS1893CY-10 is fully compliant with the ISO/IEC 8802-3 standard, as it pertains to both 10Base-T and 100Base-TX operations. The feature-rich ICS1893CY-10 allows easy migration from 10-Mbps to 100-Mbps operations as well as from systems that require support of both 10M and 100M links.

This chapter is an overview of the following ICS1893CY-10 modes of operation:

- Section 4.1, "Reset Operations"

- Section 4.2, "Power-Down Operations"

- Section 4.3, "Automatic Power-Saving Operations"

- Section 4.4, "Auto-Negotiation Operations"

- Section 4.5, "100Base-TX Operations"

- Section 4.6, "10Base-T Operations"

- Section 4.7, "Half-Duplex and Full-Duplex Operations"

- Section 4.8, "Auto-MDI/MDIX Crossover (New)"

### 4.1 Reset Operations

This section first discusses reset operations in general and then specific ways in which the ICS1893CY-10 can be configured for various reset options.

### 4.1.1 General Reset Operations

The following reset operations apply to all the specific ways in which the ICS1893CY-10 can be reset, which are discussed in Section 4.1.2, "Specific Reset Operations".

#### 4.1.1.1 Entering Reset

When the ICS1893CY-10 enters a reset condition (either through hardware, power-on reset, or software), it does the following:

- 1. Isolates the MAC/Repeater Interface input pins

- 2. Drives all MAC/Repeater Interface output pins low

- 3. Tri-states the signals on its Twisted-Pair Transmit pins (TP\_TXP and TP\_TXN)

- 4. Initializes all its internal modules and state machines to their default states

- 5. Enters the power-down state

- 6. Initializes all internal latching low (LL), latching high (LH), and latching maximum (LMX) Management Register bits to their default values

#### 4.1.1.2 Exiting Reset

When the ICS1893CY-10 exits a reset condition, it does the following:

- 1. Exits the power-down state

- 2. Latches the Serial Management Port Address of the ICS1893CY-10 into the Extended Control Register, bits 16.10:6. [See Section 7.11.3, "PHY Address (bits 16.10:6)".]

- 3. Enables all its internal modules and state machines

- 4. Sets all Management Register bits to either (1) their default values or (2) the values specified by their associated ICS1893CY-10 input pins, as determined by the HW/SW pin

- 5. Enables the Twisted-Pair Transmit pins (TP TXP and TP TXN)

- 6. Resynchronizes both its Transmit and Receive Phase-Locked Loops, which provide its transmit clock (TXCLK) and receive clock (RXCLK)

- 7. Releases all MAC/Repeater Interface pins, which takes a maximum of 640 ns after the reset condition is removed

#### 4.1.1.3 Hot Insertion

As with the ICS189X products, the ICS1893CY-10 reset design supports 'hot insertion' of its MII. (That is, the ICS1893CY-10 can connect its MAC/Repeater Interface to a MAC/repeater while power is already applied to the MAC/repeater.)

#### 4.1.2 Specific Reset Operations

This section discusses the following specific ways that the ICS1893CY-10 can be reset:

- Hardware reset (using the RESETn pin)

- Power-on reset (applying power to the ICS1893CY-10)

- Software reset (using Control Register bit 0.15)

**Note:** At the completion of a reset (either hardware, power-on, or software), the ICS1893CY-10 sets all registers to their default values.

#### 4.1.2.1 Hardware Reset

#### Entering Hardware Reset

Holding the active-low RESETn pin low for a minimum of five REF\_IN clock cycles initiates a hardware reset (that is, the ICS1893CY-10 enters the reset state). During reset, the ICS1893CY-10 executes the steps listed in Section 4.1.1.1, "Entering Reset".

#### Exiting Hardware Reset

After the signal on the RESETn pin transitions from a low to a high state, the ICS1893CY-10 completes in 640 ns (that is, in 16 REF\_IN clocks) steps 1 through 5, listed in Section 4.1.1.2, "Exiting Reset". After the first five steps are completed, the Serial Management Port is ready for normal operations, but this action does not signify the end of the reset cycle. The reset cycle completes when the transmit clock (TXCLK) and receive clock (RXCLK) are available, which is typically 53 ms after the RESETn pin goes high. [For details on this transition, see Section 9.5.18, "Reset: Hardware Reset and Power-Down".]

#### Note:

- 1. The MAC/Repeater Interface is not available for use until the TXCLK and RXCLK are valid.

- 2. The Control Register bit 0.15 does not represent the status of a hardware reset. It is a self-clearing bit that is used to initiate a software reset.

#### 4.1.2.2 Power-On Reset

#### Entering Power-On Reset

When power is applied to the ICS1893CY-10, it waits until the potential between VDD and VSS achieves a minimum voltage before entering reset and executing the steps listed in Section 4.1.1.1, "Entering Reset". After entering reset from a power-on condition, the ICS1893CY-10 remains in reset for approximately 20 µs. (For details on this transition, see Section 9.5.17, "Reset: Power-On Reset".)

#### Exiting Power-On Reset

The ICS1893CY-10 automatically exits reset and performs the same steps as for a hardware reset. (See Section 4.1.1.2, "Exiting Reset".)

**Note:** The only difference between a hardware reset and a power-on reset is that during a power-on reset, the ICS1893CY-10 isolates its RESETn input pin. All other functionality is the same. As with a hardware reset, Control Register bit 0.15 does not represent the status of a power-on reset.

#### 4.1.2.3 Software Reset

#### **Entering Software Reset**

Initiation of a software reset occurs when a management entity writes a logic one to Control Register bit 0.15. When this write occurs, the ICS1893CY-10 enters the reset state for two REF IN clock cycles.

**Note:** Entering a software reset is nearly identical to entering a hardware reset or a power-on reset, except that during a software-initiated reset, the ICS1893CY-10 does not enter the power-down state.

#### Exiting Software Reset

At the completion of a reset (either hardware, power-on, or software), the ICS1893CY-10 sets all registers to their default values. This action automatically clears (that is, sets equal to logic zero) Control Register bit 0.15, the software reset bit. Therefore, for a software reset (only), bit 0.15 is a self-clearing bit that indicates the completion of the reset process.

#### Note:

- 1. The RESETn pin is active low but Control Register bit 0.15 is active high.

- Exiting a software reset is nearly identical to exiting a hardware reset or a power-on reset, except that

upon exiting a software-initiated reset, the ICS1893CY-10 does not re-latch its Serial Management Port

Address into the Extended Control Register. [For information on the Serial Management Port Address,

see Section 7.11.3, "PHY Address (bits 16.10:6)".]

- 3. The Control Register bit 0.15 does not represent the status of a hardware reset. It is a self-clearing bit that is used to initiate a software reset. During a hardware or power-on reset, Control Register bit 0.15 does not get set to logic one. As a result, this bit 0.15 cannot be used to indicate the completion of the reset process for hardware or power-on resets.

## 4.2 Power-Down Operations

The ICS1893CY-10 enters the power-down state whenever either (1) the RESETn pin is low or (2) Control Register bit 0.11 (the Power-Down bit) is logic one. In the power-down state, the ICS1893CY-10 disables all internal functions and drives all MAC/Repeater Interface output pins to logic zero except for those that support the MII Serial Management Port. In addition, the ICS1893CY-10 tri-states its Twisted-Pair Transmit pins (TP\_TXP and TP\_TXN) to achieve an additional reduction in power.

There is one significant difference between entering the power-down state by setting Control Register bit 0.11 as opposed to entering the power-down state during a reset. When the ICS1893CY-10 enters the power-down state:

- By setting Control Register bit 0.11, the ICS1893CY-10 maintains the value of all Management Register bits except for the latching low (LL), latching high (LH), and latching maximum (LMX) status bits. Instead, these LL, LH, and LMX Management Register bits are re-initialized to their default values.

- During a reset, the ICS1893CY-10 sets all of its Management Register bits to their default values. It does

not maintain the state of any Management Register bit.

For more information on power-down operations, see the following:

- Section 7.14, "Register 19: Extended Control Register 2"

- Section 9.4, "DC Operating Characteristics", which has tables that specify the ICS1893CY-10 power consumption while in the power-down state

### 4.3 Automatic Power-Saving Operations

The ICS1893CY-10 has power-saving features that automatically minimize its total power consumption while it is operating. Table 4-1 lists the ICS1893CY-10 automatic power-saving features for the various modes.

Table 4-1. Automatic Power-Saving Features, 10Base-T and 100Base-TX Modes

| Power-                                                      | Mode for ICS1893CY-10                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Saving<br>Feature                                           | 10Base-T Mode                                                                                                                                                                                                                                                                                                   | 100Base-TX Mode                                                                                                                                                                                                                                                                                                 |

| Disable Inter-<br>nal Modules                               | In 10Base-T mode, the ICS1893CY-10 disables all its internal 100Base-TX modules.                                                                                                                                                                                                                                | In 100Base-TX mode, the ICS1893CY-10 disables all its internal 10Base-T modules.                                                                                                                                                                                                                                |

| STA Control<br>of Automatic<br>Power-<br>Saving<br>Features | When an STA sets the state of the ICS1893CY-10 Extended Control Register 2, bit 19.0 to logic:  • Zero, the 100Base-TX modules always remain enabled, even during 10Base-T operations.  • One, the ICS1893CY-10 automatically disables 100Base-TX modules while the ICS1893CY-10 is operating in 10Base-T mode. | When an STA sets the state of the ICS1893CY-10 Extended Control Register 2, bit 19.1 to logic:  • Zero, the 10Base-T modules always remain enabled, even during 100Base-TX operations.  • One, the ICS1893CY-10 automatically disables 10Base-T modules while the ICS1893CY-10 is operating in 100Base-TX mode. |

### 4.4 Auto-Negotiation Operations

The ICS1893CY-10 has an Auto-Negotiation sublayer and provides both an input pin, ANSEL (Auto-Negotiation Select) and a Control Register bit (bit 0.12) to determine whether its Auto-Negotiation sublayer is enabled or disabled. The ICS1893CY-10 HW/SW input pin exclusively selects whether the ANSEL pin (which is used for the hardware mode) or Control Register bit 0.12 (which is used for the software mode) controls its Auto-Negotiation sublayer.

When enabled, the ICS1893CY-10 Auto-Negotiation sublayer exchanges technology capability data with its remote link partner and automatically selects the highest-performance operating mode it has in common with its remote link partner. For example, if the ICS1893CY-10 supports 100Base-TX and 10Base-T modes – but its link partner supports 100Base-TX and 100Base-T4 modes – the two devices automatically select 100Base-TX as the highest-performance common operating mode. For details regarding initialization and control of the auto-negotiation process, see Section 6.2, "Functional Block: Auto-Negotiation".

### 4.5 100Base-TX Operations

The ICS1893CY-10 100Base-TX mode provides 100Base-TX physical layer (PHY) services as defined in the ISO/IEC 8802-3 standard. In the 100Base-TX mode, the ICS1893CY-10 is a 100M translator between a MAC/repeater and the physical transmission medium. As such, the ICS1893CY-10 has two interfaces, both of which are fully configurable: one to the MAC/repeater and one to the Link Segment. In 100Base-TX mode, the ICS1893CY-10 provides the following functions:

- Data conversion from both parallel-to-serial and serial-to-parallel formats

- Data encoding/decoding (4B/5B, NRZ/NRZI, and MLT-3)

- Data scrambling/descrambling

- Data transmission/reception over a twisted-pair medium

To accurately transmit and receive data, the ICS1893CY-10 employs DSP-based wave shaping, adaptive equalization, and baseline wander correction. In addition, in 100Base-TX mode, the ICS1893CY-10 provides a variety of control and status means to assist with Link Segment management. For more information on 100Base-TX, see Section 6.4, "Functional Block: 100Base-TX TP-PMD Operations".

## 4.6 10Base-T Operations

The ICS1893CY-10 10Base-T mode provides 10Base-T physical layer (PHY) services as defined in the ISO/IEC 8802-3 standard. In the 10Base-T mode, the ICS1893CY-10 is a 10M translator between a MAC/repeater and the physical transmission medium. As such, the ICS1893CY-10 has two interfaces, both of which are fully configurable: one to the MAC/repeater and one to the Link Segment. In 10Base-T mode, the ICS1893CY-10 provides the following functions:

- Data conversion from both parallel-to-serial and serial-to-parallel formats

- Manchester data encoding/decoding

- Data transmission/reception over a twisted-pair medium

In addition, in 10Base-T mode, the ICS1893CY-10 provides a variety of control and status means to assist with Link Segment management. For more information on 10Base-T, see Section 6.5, "Functional Block: 10Base-T Operations".

### 4.7 Half-Duplex and Full-Duplex Operations

The ICS1893CY-10 supports half-duplex and full-duplex operations for both 10Base-T and 100Base-TX applications. Full-duplex operation allows simultaneous transmission and reception of data, which effectively doubles the Link Segment throughput to either 20 Mbps (for 10Base-T operations) or 200 Mbps (for 100Base-TX operations).

As per the ISO/IEC standard, full-duplex operations differ slightly from half-duplex operations. These differences are necessary, as during full-duplex operations a PHY actively uses both its transmit and receive data paths simultaneously.

- In 10Base-T full-duplex operations, the ICS1893CY-10 disables its loopback function (that is, it does not automatically loop back data from its transmitter to its receiver) and disables its SQE Test function.

- In both 10Base-T and 100Base-TX full-duplex operations, the ICS1893CY-10 asserts its CRS signal only

in response to receive activity while its COL signal always remains inactive.

For more information on half-duplex and full-duplex operations, see the following sections:

- Section 7.2, "Register 0: Control Register"

- Section 7.2.8, "Duplex Mode (bit 0.8)"

- Section 7.3, "Register 1: Status Register"

- Section 7.6, "Register 4: Auto-Negotiation Register"

### 4.8 Auto-MDI/MDIX Crossover (New)

The ICS1893CY-10 includes the auto-MDI/MDIX crossover feature. In a typical CAT 5 Ethernet installation the transmit twisted pair signal pins of the RJ45 connector are crossed over in the CAT 5 wiring to the partners receive twisted pair signal pins and receive twisted pair to the partners transmit twisted pair. This is usually accomplished in the wiring plant. Hubs generally wire the RJ45 connector crossed to accomplish the crossover. Two types of CAT 5 cables (straight and crossed) are available to achieve the correct connection. The Auto-MDI/MDIX feature automatically corrects for miss-wired installations by automatically swapping transmit and receive signal pairs at the PHY when no link results. Auto-MDI/MDIX is automatic, but may be disabled for test purposes using the AMDIX\_EN pin or by writing MDIO register 19 Bits 9:8 in the MDIO register. The Auto-MDI/MDIX function is independent of Auto-Negotiation and preceeds Auto-Negotiation when enabled. The Auto-MDI/MDIX function is defaulted ON at reset.

# **Chapter 5** Interface Overviews

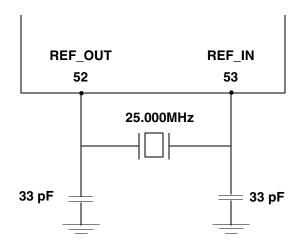

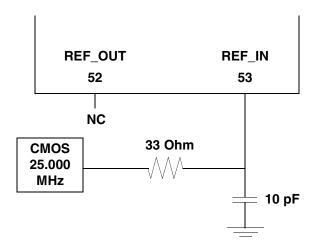

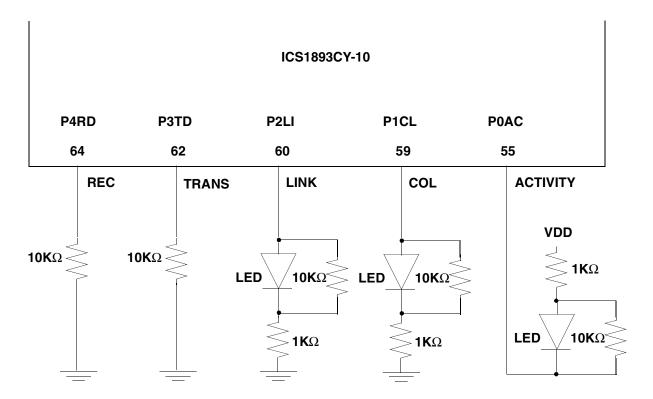

The ICS1893CY-10 MAC/Repeater Interface is fully configurable, thereby allowing it to accommodate many different applications.