# **Quad Channel Combination Regulator**

#### **■ FEATURES**

- Operating temperature range -40 to 125°C

- · Including four regulators;

Ch.1: Wide input range 1.2A buck converter.

Ch.2: Low voltage 0.6A synchronous buck converter.

Ch.3: Selectable regulator.

Low voltage 0.6A synchronous buck converter / Low voltage 0.3A LDO

Ch.4: Low voltage 0.3A LDO

e.g.) Ta=85 °C, fosc=2MHz

DC-DC Ch.1: 12V → 3.3V/1000mA

(Included supply for Ch.2, 3, 4)

Ch.2: 3.3V → 1.8V/500mA Ch.3: 3.3V → 1.2V/500mA

Ch.4: 3.3V → 2.8V/200mA

· Wide operating input voltage range

3.9V(UVLO ON: 3.35V) to 40V (Ch.1)

2.4V to 5.5V (Ch.2, Ch.3, Ch.4)

• Free power-on sequence

LDO

- Individual Power-Good Function

(High precision -7%, + 15%)

- Individual Standby Function

- · Protection function

- UVLO (Under Voltage Lockout)

- Over current protection function for more safety operation (Hiccup or Latch)

- Thermal shutdown

- · Oscillating frequency

280kHz to 2.4MHz

- External clock synchronization

- Anti-phase operation between Ch.1 and Ch.2 / 3

- · Current mode control buck converters

- · Built-in compensation circuit

- Soft start function

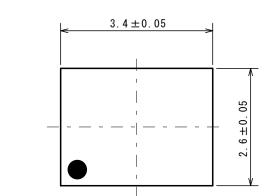

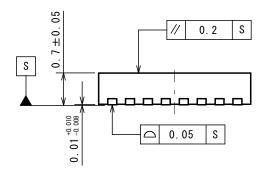

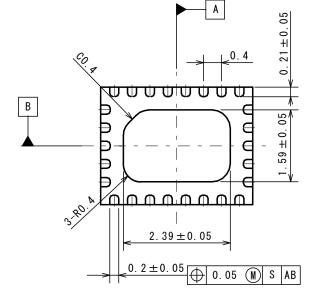

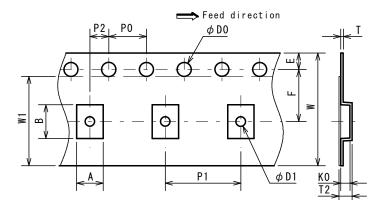

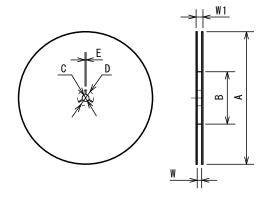

#### **PACKAGE**

EQFN26-HH

3.4mm x 2.6mm

#### **■ GENERAL DESCRIPTION**

The NJW4750 is guad channel combination regulator including one wide input range buck converter and three secondary synchronous buck converter / LDO. Ch.3 can be selectable to the synchronous buck converter mode or LDO mode. Therefore, the NJW4750 expands the choices when building power supply block suitable for various applications.

The NJW4750 is operated anti-phase operation between Ch.1 and Ch.2 / 3 in order to reduce EMI noise.

Every regulator has individual enable pin and power-good pin. Therefore, flexible power-on sequence configuration is available.

The NJW4750 has two types of over-current protection according to application demand.

Furthermore, it adopts a new overcurrent detection method which is more safety and contributes to miniaturization of the inductor.

Small package: 3.4mm × 2.6mm QFN is adopted suitable for small application such as camera module.

#### ■ TARGET APPLICATION

- Camera Module

- Photoelectric sensor

- Small Application and other.

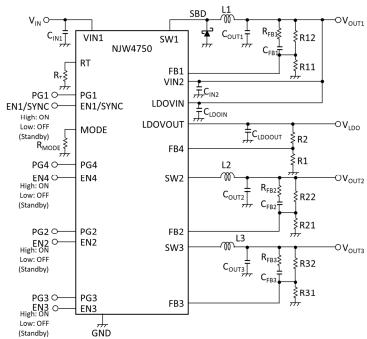

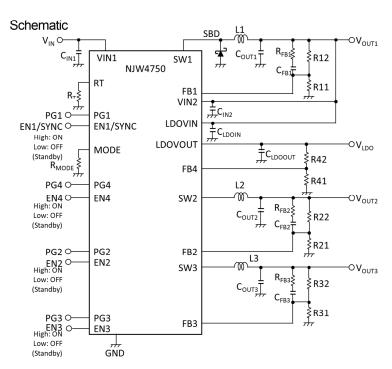

### ■ APPLICATION

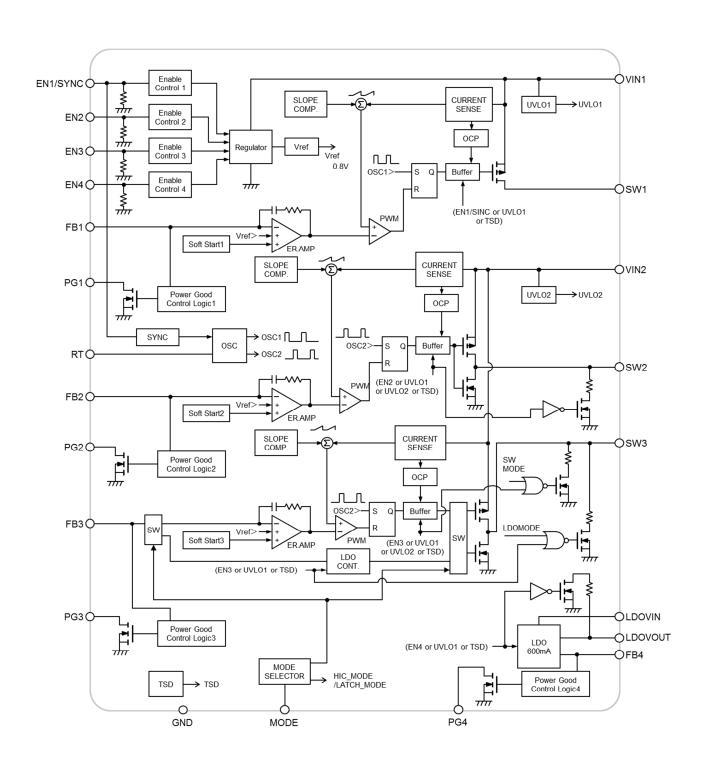

#### **BLOCK DIAGRAM**

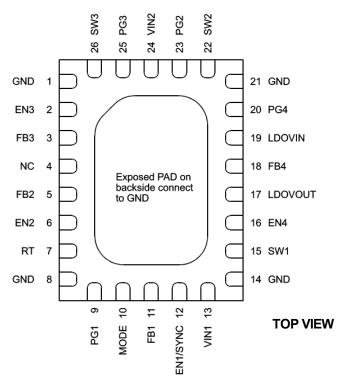

#### **■ PIN CONFIGURATION**

| PIN NO. | SYMBOL   | DESCRIPTION                           | PIN NO. | SYMBOL  | DESCRIPTION                   |

|---------|----------|---------------------------------------|---------|---------|-------------------------------|

| 1       | GND      | Ground                                | 14      | GND     | Ground                        |

| 2       | EN3      | Ch.3 Enable input                     | 15      | SW1     | Ch.1 Output                   |

| 3       | FB3      | Ch.3 Voltage feedback input           | 16      | EN4     | Ch.4 Enable input             |

| 4       | NC       | NC                                    | 17      | LDOVOUT | Ch.4 Output                   |

| 5       | FB2      | Ch.2 Voltage feedback input           | 18      | FB4     | Ch.4 Voltage feedback input   |

| 6       | EN2      | Ch.2 Enable input                     | 19      | LDOVIN  | Ch.4 Power supply input       |

| 7       | RT       | Oscillation frequency setting         | 20      | PG4     | Ch.4 Power-good output        |

| 8       | GND      | Ground                                | 21      | GND     | Ground                        |

| 9       | PG1      | Ch.1 Power-good output                | 22      | SW2     | Ch.2 Output                   |

| 10      | MODE     | Ch.3 Mode select / OCP setting        | 23      | PG2     | Ch.2 Power-good output        |

| 11      | FB1      | Ch.1 Voltage feedback input           | 24      | VIN2    | Ch.2, Ch.3 Power supply input |

| 12      | EN1/SYNC | Ch.1 Enable input /External CLK input | 25      | PG3     | Ch.3 Power-good output        |

| 13      | VIN1     | Ch.1 Power supply input               | 26      | SW3     | Ch.3 Output                   |

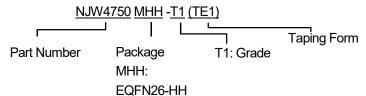

#### **■ PRODUCT NAME INFORMATION**

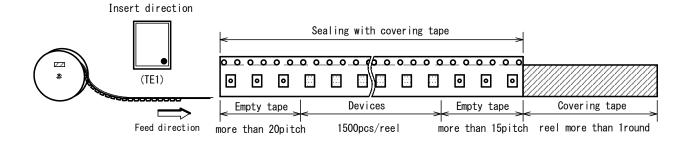

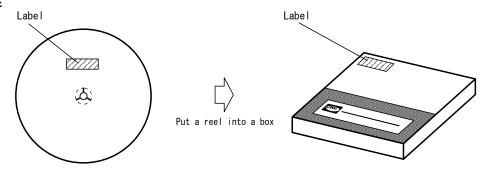

## **■ ORDERING INFORMATION**

| PRODUCT NAME       | PACKAGE   | RoHS | HALOGEN<br>FREE | TERMINAL<br>FINISH | MARKING | WEIGHT (mg) | MOQ<br>(pcs) |

|--------------------|-----------|------|-----------------|--------------------|---------|-------------|--------------|

| NJW4750MHH-T1(TE1) | EQFN26-HH | yes  | yes             | Sn2Bi              | 4750T   | 18          | 1500         |

New Japan Radio Co., Ltd. - www.njr.com

## ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER                          | SYMBOL                                        | MAXIMUM RATING             | UNIT |

|------------------------------------|-----------------------------------------------|----------------------------|------|

| Supply \/altaga                    | V <sub>VIN1</sub>                             | -0.3 to +45                | V    |

| Supply Voltage                     | $V_{VIN2}, V_{LDOVIN}$                        | -0.3 to +7                 | V    |

| Voltage between pins<br>VIN1 - SW1 | V <sub>VIN1-SW1</sub>                         | +45                        | V    |

| SW2/SW3 pin Voltage                | $V_{SW2}$ $V_{SW3}$                           | +7                         | V    |

| EN/SYNC pin Voltage                | V <sub>EN1/SYNC</sub>                         | -0.3 to +45                | V    |

| EN pin Voltage                     | $V_{EN2}, V_{EN3}$                            | -0.3 to +7                 | V    |

|                                    | V <sub>EN4</sub>                              | -0.3 to +45                | V    |

| FB pin Voltage                     | $V_{FB1}$ , $V_{FB2}$ , $V_{FB3}$ , $V_{FB4}$ | -0.3 to +7                 | V    |

| PG pin Voltage                     | $V_{PG1}$ , $V_{PG2}$ , $V_{PG3}$ , $V_{PG4}$ | -0.3 to +7                 | V    |

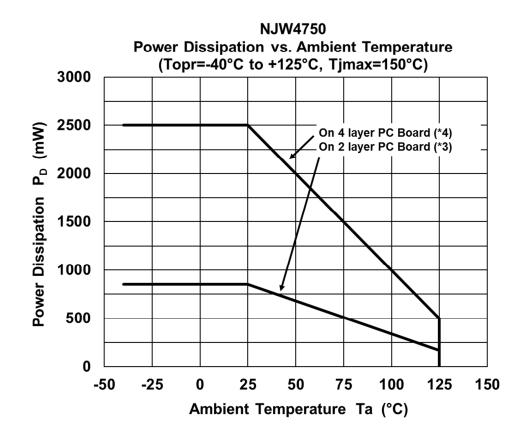

| Power Dissipation(Ta=25°C)         | P <sub>D</sub>                                | EQFN26-HH 850 (1) 2500 (2) | mW   |

| Junction Temperature               | Tj                                            | -40 to +150                | °C   |

| Operating Temperature              | T <sub>opr</sub>                              | -40 to +125                | °C   |

| Storage Temperature                | T <sub>stg</sub>                              | -50 to +150                | °C   |

<sup>(1):</sup> Mounted on glass epoxy board.

(101.5×114.5×1.6mm:based on EIA/JEDEC standard,2layers, with Exposed Pad)

(101.5×114.5×1.6mm:based on EIA/JEDEC standard,4layers, with Exposed Pad)

(For 4Layers: Applying 99.5×99.5mm inner Cu area and a thermal via holes to a board based on JEDEC standard JESD51-5)

## ■ RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL                                           | VALUE                                                                 | UNIT |

|-----------------------|--------------------------------------------------|-----------------------------------------------------------------------|------|

| Supply Voltage        | $V_{VIN1}$                                       | 3.9 to 40                                                             | V    |

| Supply Voltage        | $V_{VIN2}, V_{LDOVIN}$                           | 2.4 to 5.5                                                            | V    |

| EN/SYNC pin Voltage   | V <sub>EN1/SYNC</sub>                            | 0 to 40                                                               | V    |

| EN pin Voltage        | $V_{\text{EN2}}, V_{\text{EN3}}, V_{\text{EN4}}$ | 0 to 5.5                                                              | V    |

| PG pin Voltage        | $V_{PG1},V_{PG2},V_{PG3},V_{PG4}$                | 0 to 5.5                                                              | V    |

| Timing Resistor       | R <sub>T</sub>                                   | 1.8 to 27                                                             | kΩ   |

| Oscillating Frequency | f <sub>OSC</sub>                                 | 280 to 2400                                                           | kHz  |

| External Clock Input  | f <sub>SYNC</sub>                                | f <sub>OSC</sub> ×0.9 to f <sub>OSC</sub> ×1.7<br>Upper limit 2800kHz | kHz  |

<sup>(2):</sup> Mounted on glass epoxy board.

(Unless otherwise noted,  $V_{VIN1}=V_{EN1/SYNC}=12V$ ,  $R_T=6.8k\Omega$ ,  $Ta=25^{\circ}C$ )

# Ch.1 (Wide input range buck converter)

| PARAMETER                   | SYMBOL              | TEST CONDITION                                   | MIN.  | TYP. | MAX.  | UNIT |

|-----------------------------|---------------------|--------------------------------------------------|-------|------|-------|------|

| Under Voltage Lock Out Circ | uit Block           |                                                  |       |      |       |      |

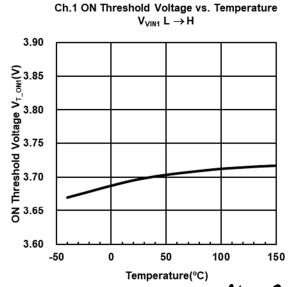

|                             |                     | $V_{VIN1}=L \rightarrow H$                       | 3.60  | 3.75 | 3.90  |      |

| ON Threshold Voltage        | $V_{T\_ON1}$        | $V_{VIN1}=L \rightarrow H$ Ta=-40°C to +125°C    | 3.60  | _    | 3.90  | V    |

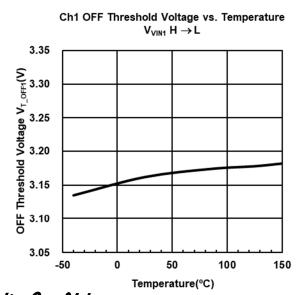

|                             |                     | $V_{VIN1}=H \rightarrow L$                       | 3.05  | 3.20 | 3.35  |      |

| OFF Threshold Voltage       | V <sub>T_OFF1</sub> | $V_{VIN1}$ =H $\rightarrow$ L Ta=-40°C to +125°C | 3.05  | _    | 3.35  | V    |

| Hysteresis Voltage          | V <sub>HYS1</sub>   |                                                  | 500   | 550  | _     | mV   |

| Soft Start Block            |                     |                                                  |       |      |       |      |

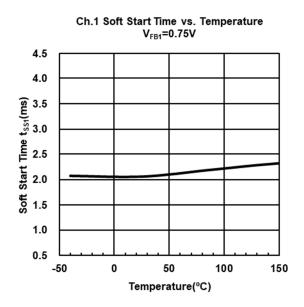

|                             |                     | V <sub>FB1</sub> =0.75V                          | 1.0   | 2.5  | 4.0   |      |

| Soft Start Time             | t <sub>ss1</sub>    | V <sub>FB1</sub> =0.75V<br>Ta=-40°C to +125°C    | 0.5   | _    | 4.5   | ms   |

| Oscillator Block            |                     |                                                  |       |      |       |      |

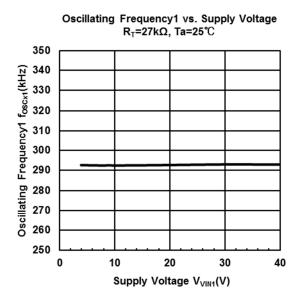

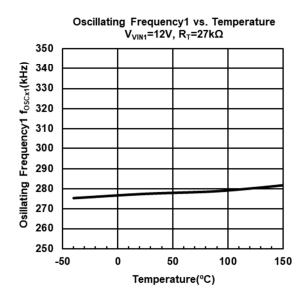

|                             |                     | $R_T$ =27k $\Omega$                              | 250   | 280  | 310   |      |

| Oscillating Frequency 1     | f <sub>OSC11</sub>  | $R_T$ =27k $\Omega$<br>Ta=-40°C to +125°C        | 250   | _    | 310   | kHz  |

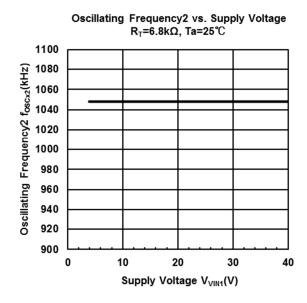

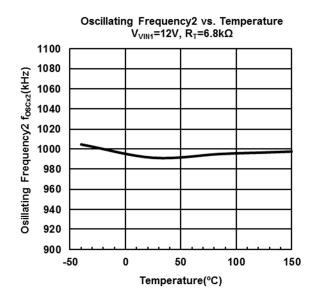

|                             |                     | R <sub>T</sub> =6.8kΩ                            | 900   | 1000 | 1100  |      |

| Oscillating Frequency 2     | f <sub>OSC12</sub>  | $R_T$ =6.8k $\Omega$<br>Ta=-40°C to +125°C       | 900   | _    | 1100  | kHz  |

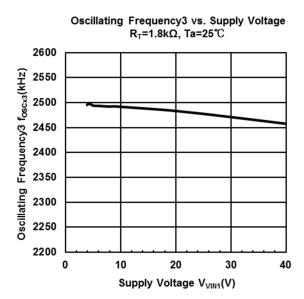

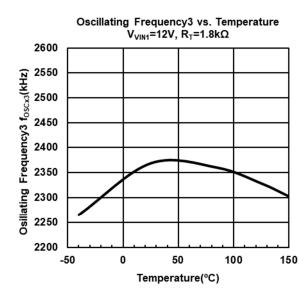

|                             |                     | R <sub>T</sub> =1.8kΩ                            | 2200  | 2400 | 2600  |      |

| Oscillating Frequency 3     | f <sub>OSC13</sub>  | $R_T$ =1.8kΩ<br>Ta=-40°C to +125°C               | 2200  | _    | 2600  | kHz  |

| Error Amplifier Block       |                     |                                                  |       |      |       |      |

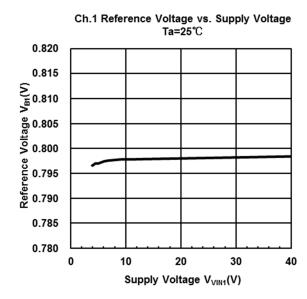

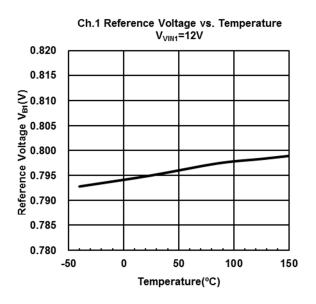

| Peference Voltage           | \/                  |                                                  | -1.0% | 0.8  | +1.0% | V    |

| Reference Voltage           | V <sub>B1</sub>     | Ta=-40°C to +125°C                               | -2.0% | _    | +2.0% | V    |

| Input Bias Current          | I <sub>B1</sub>     |                                                  | -0.1  | _    | 0.1   | μΑ   |

| par bido Garroni            | וטי                 | Ta=-40°C to +125°C                               | -0.1  | -    | 0.1   | μι   |

(Unless otherwise noted,  $V_{VIN1}=V_{EN1/SYNC}=12V$ ,  $R_T=6.8k\Omega$ ,  $Ta=25^{\circ}C$ )

# Ch.1 (Wide input range buck converter)

| PARAMETER                   | SYMBOL                    | TEST CONDITION                                                                       | MIN. | TYP. | MAX. | UNIT |

|-----------------------------|---------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| PWM Comparator Block        |                           |                                                                                      |      |      |      |      |

|                             |                           | V <sub>FB1</sub> =0.7V                                                               | 100  | _    | _    |      |

| Maximum Duty Cycle          | $M_{AX}D_{UTY1}$          | V <sub>FB1</sub> =0.7V<br>Ta=-40°C to +125°C                                         | 100  | _    | _    | %    |

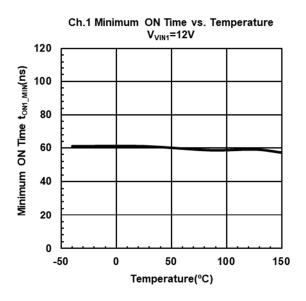

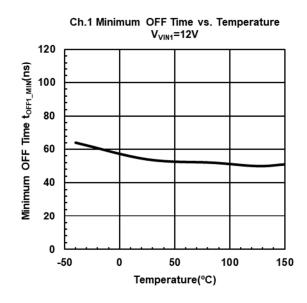

| Minimum OFF Time            | t <sub>OFF1-min</sub>     |                                                                                      | _    | 55   | -    | ns   |

| Minimum ON Time             | t <sub>ON1-min</sub>      |                                                                                      | _    | 60   | _    | ns   |

| Over Current Protection Cir | cuit Block                |                                                                                      |      |      |      |      |

| Cool Down Time              | t <sub>COOL1</sub>        | $R_{MODE}$ =36kΩ or 10 kΩ                                                            | _    | 75   | _    | ms   |

| Output Block                |                           |                                                                                      |      |      |      |      |

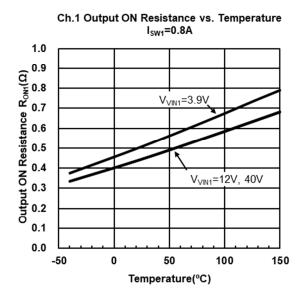

| Output ON Resistance        | R <sub>ON1</sub>          | I <sub>SW1</sub> =0.8A                                                               | _    | 0.5  | 0.8  | Ω    |

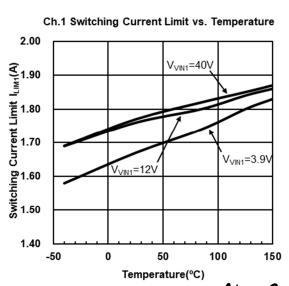

| Switching Current Limit     | I <sub>LIM1</sub>         |                                                                                      | 1.4  | 1.7  | 2.0  | Α    |

| Switching Leak Current      | I <sub>LEAK1</sub>        | $V_{\text{EN1/SYNC}}=0V, V_{\text{VIN1}}=40V$ $V_{\text{SW1}}=0V$ Ta=-40°C to +125°C | _    | _    | 4    | μА   |

| Enable Control / Sync Block | (EN1/SYNC)                |                                                                                      |      |      |      |      |

|                             |                           | $V_{EN1/SYNC}=L \rightarrow H$                                                       | 1.6  | _    | 40.0 |      |

| High Threshold Voltage      | V <sub>THH_EN1/SYNC</sub> | $V_{\text{EN1/SYNC}}=L \rightarrow H$ Ta=-40°C to +125°C                             | 1.6  | _    | 40.0 | V    |

|                             |                           | $V_{EN1/SYNC}=H \rightarrow L$                                                       | 0    | _    | 0.4  |      |

| Low Threshold Voltage       | V <sub>THL_EN1/SYNC</sub> | $V_{\text{EN1/SYNC}}=H \rightarrow L$ Ta=-40°C to +125°C                             | 0    | _    | 0.4  | V    |

|                             |                           | V <sub>EN1/SYNC</sub> =5V                                                            | _    | 1    | 3    |      |

| Input Bias Current          | I <sub>EN1/SYNC</sub>     | V <sub>EN1/SYNC</sub> =5V<br>Ta=-40°C to +125°C                                      | _    | _    | 5    | μΑ   |

(Unless otherwise noted,  $V_{VIN1}=V_{EN1/SYNC}=12V$ ,  $R_T=6.8k\Omega$ ,  $Ta=25^{\circ}C$ )

# Ch.1 (Wide input range buck converter)

| PARAMETER                 | SYMBOL                | TEST CONDITION                               | MIN.  | TYP. | MAX.  | UNIT |  |  |

|---------------------------|-----------------------|----------------------------------------------|-------|------|-------|------|--|--|

| Power Good Block(PG1)     |                       |                                              |       |      |       |      |  |  |

| High Level Detection      | V                     | Rising                                       | 0.836 | _    | 0.924 | V    |  |  |

| Reference Voltage         | V <sub>THH_PG1</sub>  | Rising, Ta=-40°C to +125°C                   | 0.836 | _    | 0.924 | V    |  |  |

| Low Level Detection       | V                     | Rising                                       | 0.745 | _    | 0.775 | V    |  |  |

| Reference Voltage         | $V_{THL\_PG1}$        | Rising, Ta=-40°C to +125°C                   | 0.745 | _    | 0.775 | V    |  |  |

| Hysteresis Voltage        | V <sub>HYS_PG1</sub>  |                                              | _     | 16   | _     | mV   |  |  |

| Power Good ON Resistance  | R <sub>ON_PG1</sub>   | I <sub>PG1</sub> =10mA                       | _     | 100  | _     | Ω    |  |  |

|                           |                       | V <sub>PG1</sub> =5.5V                       | _     | _    | 0.1   |      |  |  |

| Leak Current at OFF State | I <sub>LEAK_PG1</sub> | V <sub>PG1</sub> =5.5V<br>Ta=-40°C to +125°C | _     | _    | 0.1   | μΑ   |  |  |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN2}$ =3.3V,  $R_T$ =6.8k $\Omega$ , Ta=25°C)

Ch.2 (Low voltage synchronous buck converter)

| PARAMETER                  | SYMBOL             | TEST CONDITION                                   | MIN.  | TYP. | MAX.  | UNIT  |

|----------------------------|--------------------|--------------------------------------------------|-------|------|-------|-------|

| Under Voltage Lock Out Cir | cuit Block         |                                                  |       |      |       |       |

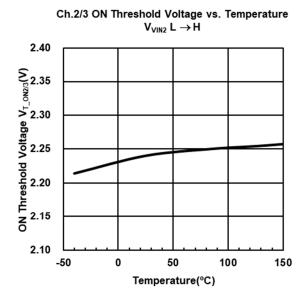

|                            |                    | $V_{VIN2}=L \rightarrow H$                       | 2.10  | 2.25 | 2.40  |       |

| ON Threshold Voltage       | V <sub>T_ON2</sub> | $V_{VIN2}$ =L $\rightarrow$ H Ta=-40°C to +125°C | 2.10  | _    | 2.40  | V     |

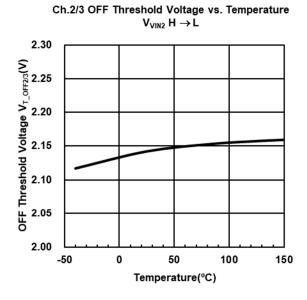

|                            |                    | $V_{VIN2}=H \rightarrow L$                       | 2.00  | 2.15 | 2.30  |       |

| OFF Threshold Voltage      | $V_{T\_OFF2}$      | $V_{VIN2}$ =H $\rightarrow$ L Ta=-40°C to +125°C | 2.00  | -    | 2.30  | V     |

| Hysteresis Voltage         | V <sub>HYS2</sub>  |                                                  | 50    | 100  | _     | mV    |

| Soft Start Block           |                    |                                                  |       |      |       |       |

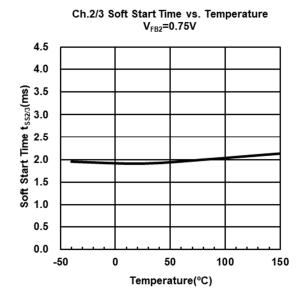

| Soft Start Time            |                    | V <sub>FB2</sub> =0.75V                          | 1.0   | 2.5  | 4.0   |       |

|                            | t <sub>SS2</sub>   | V <sub>FB2</sub> =0.75V<br>Ta=-40°C to +125°C    | 0.5   | _    | 4.5   | ms    |

| Oscillator Block           |                    |                                                  |       |      |       |       |

|                            |                    | $R_T$ =27k $\Omega$                              | 250   | 280  | 310   |       |

| Oscillating Frequency 1    | f <sub>OSC21</sub> | $R_T$ =27k $\Omega$<br>Ta=-40°C to +125°C        | 250   | _    | 310   | kHz   |

|                            |                    | $R_T$ =6.8k $\Omega$                             | 900   | 1000 | 1100  |       |

| Oscillating Frequency 2    | f <sub>OSC22</sub> | $R_T$ =6.8k $\Omega$<br>Ta=-40°C to +125°C       | 900   | _    | 1100  | kHz   |

|                            |                    | $R_T$ =1.8k $\Omega$                             | 2200  | 2400 | 2600  |       |

| Oscillating Frequency 3    | f <sub>OSC23</sub> | $R_T$ =1.8k $\Omega$<br>Ta=-40°C to +125°C       | 2200  | -    | 2600  | kHz   |

| Error Amplifier Block      |                    |                                                  |       |      |       |       |

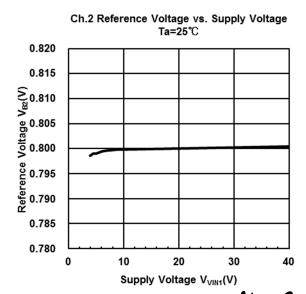

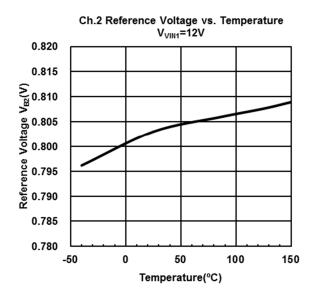

| D. C                       |                    |                                                  | -1.0% | 8.0  | +1.0% |       |

| Reference Voltage          | $V_{B2}$           | Ta=-40°C to +125°C                               | -2.0% | _    | +2.0% | V     |

| Input Bias Current         | ı                  |                                                  | -0.1  | _    | 0.1   | , . Λ |

| input bias Culterit        | I <sub>B2</sub>    | Ta=-40°C to +125°C                               | -0.1  | _    | 0.1   | μΑ    |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN2}$ =3.3V,  $R_T$ =6.8k $\Omega$ , Ta=25°C)

# Ch.2 (Low voltage synchronous buck converter)

| PARAMETER                     | SYMBOL                | TEST CONDITION                                                         | MIN. | TYP. | MAX. | UNIT |

|-------------------------------|-----------------------|------------------------------------------------------------------------|------|------|------|------|

| PWM Comparator Block          |                       |                                                                        |      |      |      |      |

|                               |                       | V <sub>FB2</sub> =0.7V                                                 | 100  | _    | _    |      |

| Maximum Duty Cycle            | $M_{AX}D_{UTY2}$      | V <sub>FB2</sub> =0.7V<br>Ta=-40°C to +125°C                           | 100  | _    | _    | %    |

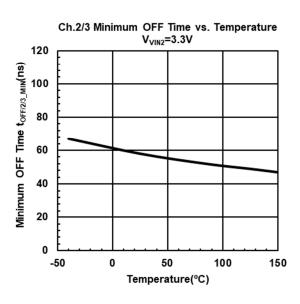

| Minimum OFF Time              | t <sub>OFF2-min</sub> |                                                                        | _    | 55   | _    | ns   |

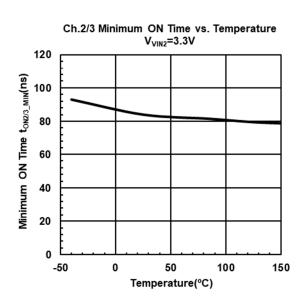

| Minimum ON Time               | t <sub>ON2-min</sub>  |                                                                        | _    | 80   | _    | ns   |

| Over Current Protection Circu | it Block              |                                                                        |      |      |      |      |

| Cool Down Time                | t <sub>COOL2</sub>    | $R_{MODE}$ =36k $\Omega$ or 10 k $\Omega$                              | _    | 75   | _    | ms   |

| Output Block                  |                       |                                                                        |      |      |      |      |

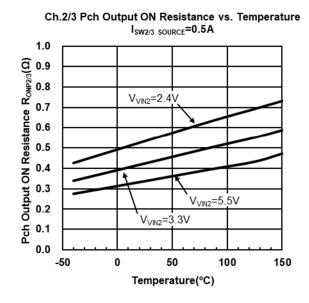

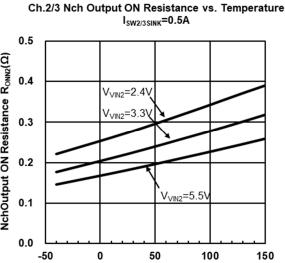

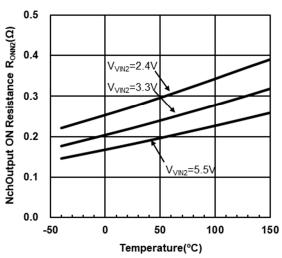

| Pch Output ON Resistance      | R <sub>ONP2</sub>     | I <sub>SW2SOURCE</sub> =0.5A                                           | _    | 0.5  | 0.8  | Ω    |

| Nch Output ON Resistance      | R <sub>ONN2</sub>     | I <sub>SW2SINK</sub> =0.5A                                             | _    | 0.3  | 0.5  | Ω    |

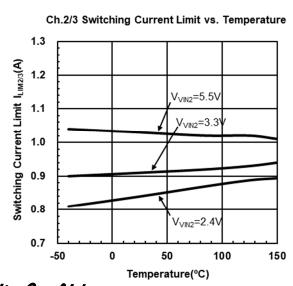

| Switching Current Limit       | I <sub>LIM2</sub>     |                                                                        | 0.7  | 1.0  | 1.3  | Α    |

| Switching Leak Current        | I <sub>LEAK2</sub>    | $V_{EN2}$ =0V, $V_{V N2}$ =5.5V<br>$V_{SW2}$ =0V<br>Ta=-40°C to +125°C | -    | _    | 4    | μΑ   |

| Enable Control Block (EN2)    |                       |                                                                        |      |      |      |      |

|                               |                       | $V_{EN2}=L \rightarrow H$                                              | 1.0  | _    | 5.5  |      |

| High Threshold Voltage        | $V_{THH\_EN2}$        | $V_{EN2}$ =L $\rightarrow$ H Ta=-40°C to +125°C                        | 1.0  | _    | 5.5  | V    |

|                               |                       | $V_{EN2}=H \rightarrow L$                                              | 0    | _    | 0.4  |      |

| Low Threshold Voltage         | $V_{THL\_EN2}$        | $V_{EN2}$ =H $\rightarrow$ L Ta=-40°C to +125°C                        | 0    | _    | 0.4  | V    |

|                               |                       | V <sub>EN2</sub> =3.3V                                                 | _    | 7    | 14   |      |

| Input Bias Current            | I <sub>EN2</sub>      | V <sub>EN2</sub> =3.3V<br>Ta=-40°C to +125°C                           | _    | _    | 14   | μΑ   |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN2}$ =3.3V,  $R_T$ =6.8k $\Omega$ , Ta=25°C)

# Ch.2 (Low voltage synchronous buck converter)

| PARAMETER                 | SYMBOL              | TEST CONDITION             | MIN.  | TYP. | MAX.  | UNIT |  |  |

|---------------------------|---------------------|----------------------------|-------|------|-------|------|--|--|

| Power Good Block (PG2)    |                     |                            |       |      |       |      |  |  |

| High Level Detection      | V                   | Rising                     | 0.836 | _    | 0.924 | V    |  |  |

| Reference Voltage         | $V_{THH\_PG2}$      | Rising, Ta=-40°C to +125°C | 0.836 | _    | 0.924 | V    |  |  |

| Low Level Detection       | \/                  | Rising                     | 0.745 | _    | 0.775 | V    |  |  |

| Reference Voltage         | $V_{THL\_PG2}$      | Rising, Ta=-40°C to +125°C | 0.745 | _    | 0.775 | V    |  |  |

| Hysteresis Voltage        | $V_{HYS\_PG2}$      |                            | _     | 16   | _     | mV   |  |  |

| Power Good ON Resistance  | R <sub>ON_PG2</sub> | I <sub>PG2</sub> =10mA     | _     | 100  | _     | Ω    |  |  |

|                           |                     | V <sub>PG2</sub> =5.5V     | _     | _    | 0.1   |      |  |  |

| Leak Current at OFF State | $I_{LEAK\_PG2}$     | V <sub>PG2</sub> =5.5V     | _     | _    | 0.1   | μΑ   |  |  |

|                           |                     | Ta=-40°C to +125°C         | _     | _    | 0.1   |      |  |  |

(Unless otherwise noted, V<sub>VIN1</sub>=12V, V<sub>VIN2</sub>=V<sub>EN3</sub>=3.3V, R<sub>T</sub>=6.8k $\Omega$  , Ta=25°C)

Ch.3 (Selectable regulator: SW Reg. MODE and LDO MODE can share the same table.)

| PARAMETER                  | SYMBOL                | TEST CONDITION                                  | MIN.  | TYP. | MAX.  | UNIT |

|----------------------------|-----------------------|-------------------------------------------------|-------|------|-------|------|

| Enable Control Block (EN3) |                       |                                                 |       |      |       |      |

|                            |                       | $V_{EN3}=L \rightarrow H$                       | 1.0   | _    | 5.5   |      |

| High Threshold Voltage     | $V_{THH\_EN3}$        | $V_{EN3}$ =L $\rightarrow$ H Ta=-40°C to +125°C | 1.0   | -    | 5.5   | V    |

|                            |                       | $V_{EN3}$ =H $\rightarrow$ L                    | 0     | _    | 0.4   |      |

| Low Threshold Voltage      | $V_{THL\_EN3}$        | $V_{EN3}$ =H $\rightarrow$ L Ta=-40°C to +125°C | 0     | _    | 0.4   | V    |

| Input Bias Current         |                       | V <sub>EN3</sub> =3.3V                          | _     | 7    | 14    |      |

|                            | I <sub>EN3</sub>      | V <sub>EN3</sub> =3.3V<br>Ta=-40°C to +125°C    | _     | _    | 14 μΑ | μА   |

| Power Good Block (PG3)     |                       |                                                 |       |      |       |      |

| High Level Detection       | V                     | Rising                                          | 0.836 | _    | 0.924 | V    |

| Reference Voltage          | $V_{THH\_PG3}$        | Rising, Ta=-40°C to +125°C                      | 0.836 | _    | 0.924 | V    |

| Low Level Detection        | V                     | Rising                                          | 0.745 | _    | 0.775 | V    |

| Reference Voltage          | $V_{THL\_PG3}$        | Rising, Ta=-40°C to +125°C                      | 0.745 | _    | 0.775 | V    |

| Hysteresis Voltage         | $V_{HYS\_PG3}$        |                                                 | _     | 16   | _     | mV   |

| Power Good ON Resistance   | $R_{ON\_PG3}$         | I <sub>PG3</sub> =10mA                          | _     | 100  | _     | Ω    |

|                            |                       | V <sub>PG3</sub> =5.5V                          | _     | _    | 0.1   |      |

| Leak Current at OFF State  | I <sub>LEAK_PG3</sub> | V <sub>PG3</sub> =5.5V<br>Ta=-40°C to +125°C    | _     | _    | 0.1   | μΑ   |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN3}$ =3.3V,  $R_T$ =6.8k $\Omega$ ,  $R_{MODE}$ = 82k $\Omega$  or 36k $\Omega$ , Ta=25°C)

Ch.3 (Selectable regulator: SW Reg. MODE)

| PARAMETER                  | SYMBOL             | TEST CONDITION                                   | MIN.  | TYP. | MAX.  | UNIT |

|----------------------------|--------------------|--------------------------------------------------|-------|------|-------|------|

| Under Voltage Lock Out Cir | cuit Block         |                                                  |       |      |       |      |

|                            |                    | $V_{VIN2}=L \rightarrow H$                       | 2.10  | 2.25 | 2.40  |      |

| ON Threshold Voltage       | V <sub>T_ON3</sub> | $V_{VIN2}$ =L $\rightarrow$ H Ta=-40°C to +125°C | 2.10  | _    | 2.40  | V    |

|                            |                    | $V_{VIN2}=H \rightarrow L$                       | 2.00  | 2.15 | 2.30  |      |

| OFF Threshold Voltage      | $V_{T\_OFF3}$      | $V_{VIN2}$ =H $\rightarrow$ L Ta=-40°C to +125°C | 2.00  | -    | 2.30  | V    |

| Hysteresis Voltage         | V <sub>HYS3</sub>  |                                                  | 50    | 100  | _     | mV   |

| Soft Start Block           |                    |                                                  |       |      |       |      |

| Soft Start Time            |                    | V <sub>FB3</sub> =0.75V                          | 1.0   | 2.5  | 4.0   |      |

|                            | t <sub>ss3</sub>   | V <sub>FB3</sub> =0.75V<br>Ta=-40°C to +125°C    | 0.5   | _    | 4.5   | ms   |

| Oscillator Block           |                    |                                                  |       |      |       |      |

|                            |                    | $R_T$ =27k $\Omega$                              | 250   | 280  | 310   |      |

| Oscillating Frequency 1    | f <sub>OSC31</sub> | $R_T$ =27kΩ Ta=-40°C to +125°C                   | 250   | _    | 310   | kHz  |

|                            |                    | $R_T$ =6.8k $\Omega$                             | 900   | 1000 | 1100  |      |

| Oscillating Frequency 2    | f <sub>OSC32</sub> | $R_T$ =6.8k $\Omega$<br>Ta=-40°C to +125°C       | 900   | _    | 1100  | kHz  |

|                            |                    | $R_T$ =1.8 $k\Omega$                             | 2200  | 2400 | 2600  |      |

| Oscillating Frequency 3    | f <sub>OSC33</sub> | $R_T$ =1.8k $\Omega$<br>Ta=-40°C to +125°C       | 2200  | _    | 2600  | kHz  |

| Error Amplifier Block      |                    |                                                  |       |      |       |      |

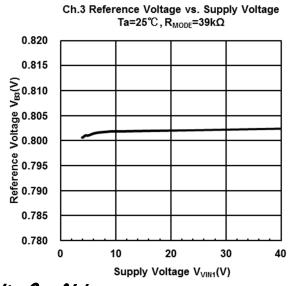

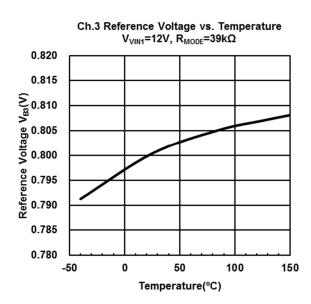

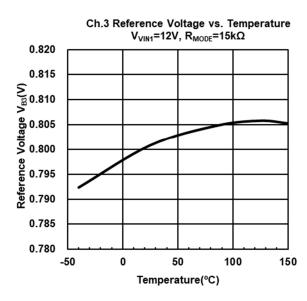

| D. C                       |                    |                                                  | -1.0% | 0.8  | +1.0% |      |

| Reference Voltage          | $V_{B3}$           | Ta=-40°C to +125°C                               | -2.0% | -    | +2.0% | V    |

| Input Bias Current         | I                  |                                                  | -0.1  | _    | 0.1   | ^    |

| input bias Culterit        | I <sub>B3</sub>    | Ta=-40°C to +125°C                               | -0.1  | _    | 0.1   | μΑ   |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN3}$ =3.3V,  $R_T$ =6.8k $\Omega$ ,  $R_{MODE}$ = 82k $\Omega$  or 36k $\Omega$ , Ta=25°C)

Ch.3 (Selectable regulator: SW Reg. MODE)

| PARAMETER                             | SYMBOL                | TEST CONDITION                                                         | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------|-----------------------|------------------------------------------------------------------------|------|------|------|------|

| PWM Comparator Block                  |                       |                                                                        |      |      |      |      |

|                                       |                       | V <sub>FB3</sub> =0.7V                                                 | 100  | _    | _    |      |

| Maximum Duty Cycle                    | $M_{AX}D_{UTY3}$      | V <sub>FB3</sub> =0.7V<br>Ta=-40°C to +125°C                           | 100  | _    | -    | %    |

| Minimum OFF Time                      | t <sub>OFF3-min</sub> |                                                                        | _    | 55   | _    | ns   |

| Minimum ON Time                       | t <sub>ON3-min</sub>  |                                                                        | _    | 80   | _    | ns   |

| Over Current Protection Circuit Block |                       |                                                                        |      |      |      |      |

| Cool Down Time                        | t <sub>COOL3</sub>    | $R_{MODE}$ =36k $\Omega$                                               | _    | 75   | 1    | ms   |

| Output Block                          |                       |                                                                        |      |      |      |      |

| Pch Output ON Resistance              | R <sub>ONP3</sub>     | I <sub>SW3SOURCE</sub> =0.5A                                           | _    | 0.5  | 0.8  | Ω    |

| Nch Output ON Resistance              | R <sub>ONN3</sub>     | I <sub>SW3SINK</sub> =0.5A                                             | _    | 0.3  | 0.5  | Ω    |

| Switching Current Limit               | I <sub>LIM3</sub>     |                                                                        | 0.7  | 1.0  | 1.3  | Α    |

| Switching Leak Current                | I <sub>LEAK3</sub>    | $V_{EN3}$ =0V, $V_{VIN2}$ =5.5V<br>$V_{SW3}$ =0V<br>Ta=-40°C to +125°C | _    | _    | 4    | μΑ   |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{VIN2}$ = $V_{EN3}$ =3.3V,  $R_T$ =6.8k $\Omega$ ,  $R_{MODE}$ = OPEN or 10k $\Omega$ , Ta=25°C)

Ch.3 (Selectable regulator: LDO MODE)

| PARAMETER                                         | SYMBOL                    | TEST CONDITION                                                           | MIN.    | TYP.      | MAX.  | UNIT   |

|---------------------------------------------------|---------------------------|--------------------------------------------------------------------------|---------|-----------|-------|--------|

| Error Amplifier Block                             |                           |                                                                          |         |           |       |        |

| Deference Voltage                                 | V                         |                                                                          | -1.0%   | -1.0% 0.8 | +1.0% | V      |

| Reference Voltage                                 | $V_{B3}$                  | Ta=-40°C to +125°C                                                       | -2.0%   | _         | +2.0% |        |

|                                                   |                           | V <sub>OUT3</sub> ×0.9                                                   | 300     | 600       | _     |        |

| Output Current                                    | I <sub>ОUТЗ</sub>         | V <sub>ОUТ3</sub> ×0.9<br>Та=-40°С to +125°С                             | 300     | _         | _     | mA     |

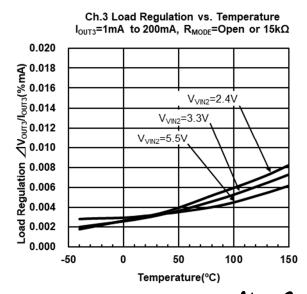

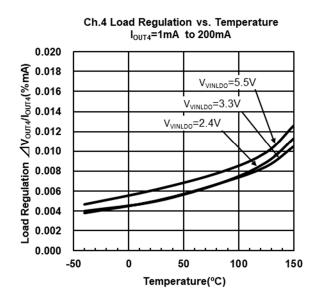

| Load Regulation                                   | <b>A</b> 1                | I <sub>OUT3</sub> =1mA to 200mA                                          | - 0.003 | 0.009     |       |        |

|                                                   | ∠V <sub>OUT3</sub>        | I <sub>OUT3</sub> =1mA to 200mA<br>Ta=-40°C to +125°C                    | _       | _         | 0.020 | %/mA   |

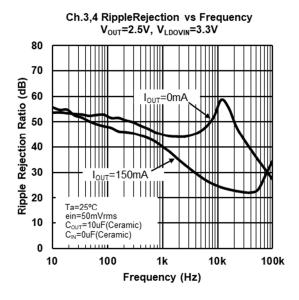

| Ripple Rejection                                  | RR3                       | ein=50mVrms, f=1kHz<br>V <sub>OUT3</sub> =2.5V, I <sub>OUT3</sub> =150mA | _       | 40        | _     | dB     |

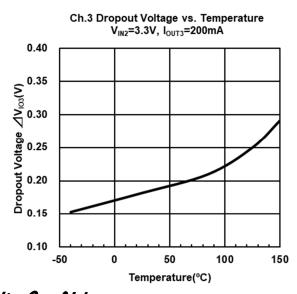

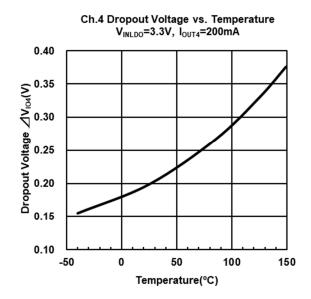

|                                                   |                           | I <sub>OUT3</sub> =200mA                                                 | _       | 0.2       | 0.3   |        |

| Dropout Voltage                                   | ∠V <sub>IO3</sub>         | I <sub>OUT3</sub> =200mA<br>Ta=-40°C to +125°C                           | _       | _         | 0.4   | V      |

| Average Temperature Coefficient of Output Voltage | ⊿V <sub>оитз</sub><br>/Та | I <sub>OUT3</sub> =150mA<br>Ta=-20°C to +75°C                            | _       | ±50       | _     | ppm/°C |

(Unless otherwise noted,  $V_{VIN1}$ =12V,  $V_{LDOVIN}$ = $V_{EN4}$  =3.3V,  $R_T$ =6.8k $\Omega$ , Ta=25°C)

# Ch.4 (Low voltage LDO)

| PARAMETER                                         | SYMBOL                    | TEST CONDITION                                                           | MIN.  | TYP.  | MAX.  | UNIT   |

|---------------------------------------------------|---------------------------|--------------------------------------------------------------------------|-------|-------|-------|--------|

| Error Amplifier Block                             |                           |                                                                          |       |       |       |        |

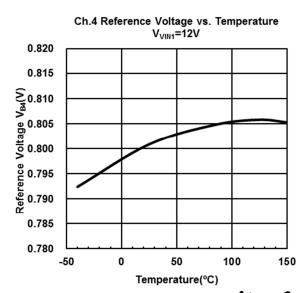

| Reference Voltage                                 | V                         |                                                                          | -1.0% | 0.8   | +1.0% | V      |

| Reference voltage                                 | $V_{B4}$                  | Ta=-40°C to +125°C                                                       | -2.0% | _     | +2.0% | V      |

|                                                   |                           | V <sub>OUT4</sub> ×0.9                                                   | 300   | 600   | _     |        |

| Output Current                                    | $I_{OUT4}$                | V <sub>OUT4</sub> ×0.9                                                   | 300   | _     | _     | mA     |

|                                                   |                           | Ta=-40°C to +125°C                                                       | 000   |       |       |        |

|                                                   | $\Delta V_{OUT4}$         | I <sub>OUT4</sub> =1mA to 200mA                                          | _     | 0.003 | 0.009 |        |

| Load Regulation                                   | /I <sub>OUT4</sub>        | I <sub>OUT4</sub> =1mA to 200mA<br>Ta=-40°C to +125°C                    | _     | _     | 0.020 | %/mA   |

| Ripple Rejection                                  | RR4                       | ein=50mVrms, f=1kHz<br>V <sub>OUT4</sub> =2.5V, I <sub>OUT4</sub> =150mA | _     | 40    | _     | dB     |

|                                                   |                           | I <sub>OUT4</sub> =200mA                                                 | _     | 0.2   | 0.3   |        |

| Dropout Voltage                                   | $\Delta V_{104}$          | I <sub>OUT4</sub> =200mA                                                 |       |       |       | V      |

|                                                   |                           | Ta=-40°C to +125°C                                                       | _     | _     | 0.4   |        |

| Average Temperature Coefficient of Output Voltage | ∠V <sub>ouт4</sub><br>/Ta | I <sub>OUT4</sub> =150mA<br>Ta=-20°C to +75°C                            | -     | ±50   | _     | ppm/°C |

| Enable Control Block (EN4)                        |                           |                                                                          | 1     |       |       |        |

|                                                   |                           | $V_{EN4}=L \rightarrow H$                                                | 1.0   | _     | 5.5   |        |

| High Threshold Voltage                            | $V_{\text{THH\_EN4}}$     | $V_{EN4}=L \rightarrow H$ Ta=-40°C to +125°C                             | 1.0   | _     | 5.5   | V      |

|                                                   |                           | $V_{EN4}=H \rightarrow L$                                                | 0     | _     | 0.4   |        |

| Low Threshold Voltage                             | $V_{\text{THL\_EN4}}$     | $V_{EN4}$ =H $\rightarrow$ L Ta=-40°C to +125°C                          | 0     | _     | 0.4   | V      |

|                                                   |                           | V <sub>EN4</sub> =3.3V                                                   | _     | 7     | 14    |        |

| Input Bias Current                                | I <sub>EN4</sub>          | V <sub>EN4</sub> =3.3V<br>Ta=-40°C to +125°C                             | _     | -     | 14    | μΑ     |

| Power Good Block (PG4)                            |                           |                                                                          |       |       |       |        |

| High Level Detection                              | .,                        | Rising                                                                   | 0.836 | _     | 0.924 |        |

| Reference Voltage                                 | $V_{THH\_PG4}$            | Rising, Ta=-40°C to +125°C                                               | 0.836 | _     | 0.924 | V      |

| Low Level Detection                               | \ /                       | Rising                                                                   | 0.745 | _     | 0.775 | \\     |

| Reference Voltage                                 | $V_{THL\_PG4}$            | Rising, Ta=-40°C to +125°C                                               | 0.745 | _     | 0.775 | V      |

| Hysteresis Voltage                                | $V_{HYS\_PG4}$            |                                                                          | _     | 16    | _     | mV     |

| Power Good ON Resistance                          | R <sub>ON_PG4</sub>       | I <sub>PG4</sub> =10mA                                                   | _     | 100   | _     | Ω      |

|                                                   | _                         | V <sub>PG4</sub> =5.5V                                                   | _     | _     | 0.1   |        |

| Leak Current at OFF State                         | I <sub>LEAK_PG4</sub>     | V <sub>PG4</sub> =5.5V<br>Ta=-40°C to +125°C                             | _     | _     | 0.1   | μΑ     |

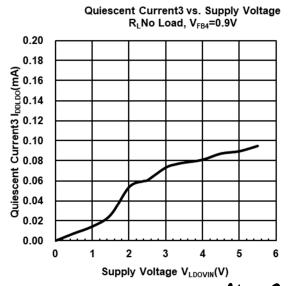

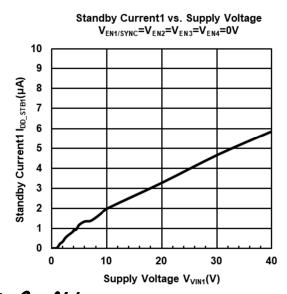

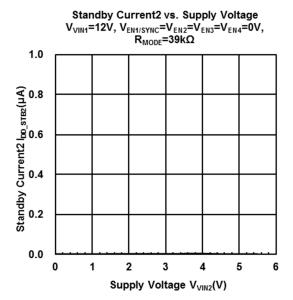

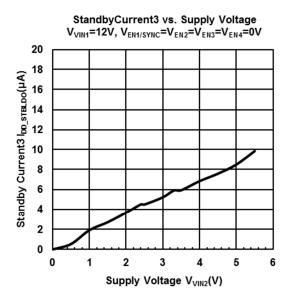

$(Unless \ otherwise \ noted, \ V_{VIN1}=V_{EN1/SYNC}=12V, \ V_{VIN2}=V_{LDOVIN}=V_{EN2}=V_{EN3}=V_{EN4}=3.3V, \ R_T=6.8k\Omega, \ Ta=25^{\circ}C)$

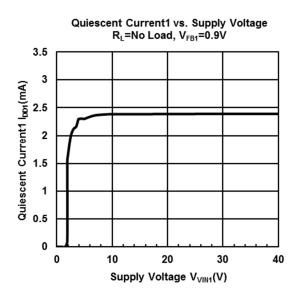

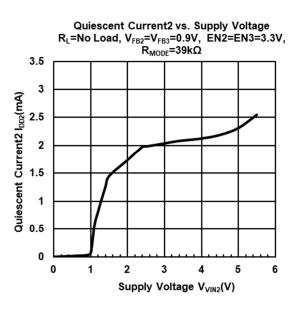

## Common parameter

| PARAMETER                     | SYMBOL                 | TEST CONDITION                                                       | MIN. | TYP. | MAX. | UNIT   |

|-------------------------------|------------------------|----------------------------------------------------------------------|------|------|------|--------|

| General Characteristic        |                        |                                                                      |      |      |      |        |

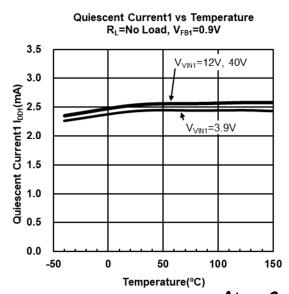

| Quiescent Current 1<br>(VIN1) |                        | R <sub>L</sub> =no load, V <sub>FB1</sub> =0.9V                      | _    | 2.3  | 3.5  |        |

|                               | I <sub>DD1</sub>       | R <sub>L</sub> =no load, V <sub>FB1</sub> =0.9V                      | _    | _    | 3.5  | mA     |

|                               |                        | Ta=-40°C to +125°C                                                   |      |      | 0.0  |        |

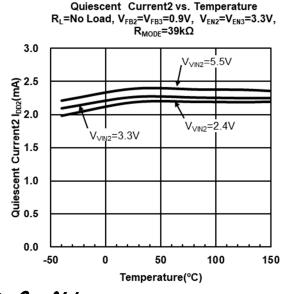

|                               |                        | R <sub>L</sub> =no load                                              | _    | 2    | 3    |        |

| Quiescent Current 2           |                        | V <sub>FB2</sub> =0.9V, V <sub>FB3</sub> =0.9V                       |      |      |      |        |

| (VIN2)                        | I <sub>DD2</sub>       | R <sub>L</sub> =no load                                              |      |      |      | mA     |

|                               |                        | V <sub>FB2</sub> =0.9V, V <sub>FB3</sub> =0.9V<br>Ta=-40°C to +125°C | _    | _    | 3    |        |

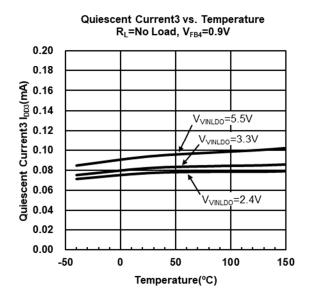

|                               |                        | $R_L$ =no load, $V_{FB4}$ =0.9V                                      |      | 0.1  | 0.2  |        |

| Quiescent Current 3           | I <sub>DDLDO</sub>     | $R_L$ =no load, $V_{FB4}$ =0.9V                                      |      | 0.1  |      | mA     |

| (LDOVIN)                      | IDDLDO                 | Ta=-40°C to +125°C                                                   | _    | _    | 0.2  | 1117 ( |

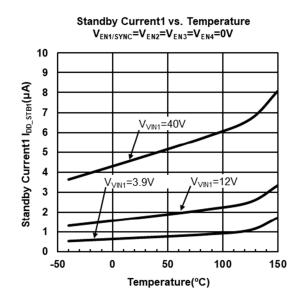

|                               |                        | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      |        |

|                               |                        | V <sub>EN2</sub> =0V                                                 |      |      |      |        |

|                               |                        | V <sub>EN3</sub> =0V                                                 | _    | _    | 3    | μΑ     |

| 0                             |                        | V <sub>EN4</sub> =0V                                                 |      |      |      |        |

| Standby Current 1<br>(VIN1)   | I <sub>DD_STB1</sub>   | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      |        |

| (VIIVI)                       |                        | V <sub>EN2</sub> =0V                                                 |      |      |      |        |

|                               |                        | V <sub>EN3</sub> =0V                                                 | _    | _    | 6    |        |

|                               |                        | V <sub>EN4</sub> =0V                                                 |      |      |      |        |

|                               |                        | Ta=-40°C to +125°C                                                   |      |      |      |        |

|                               |                        | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      |        |

|                               |                        | V <sub>EN2</sub> =0V                                                 |      | _    | 2    |        |

|                               |                        | V <sub>EN3</sub> =0V                                                 |      |      |      |        |

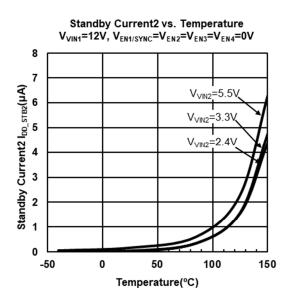

| Standby Current 2             |                        | V <sub>EN4</sub> =0V                                                 |      |      |      |        |

| (VIN2)                        | I <sub>DD_STB2</sub>   | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      | μΑ     |

| (*****                        |                        | V <sub>EN2</sub> =0V                                                 |      |      |      |        |

|                               |                        | V <sub>EN3</sub> =0V                                                 | _    | _    | 4    |        |

|                               |                        | V <sub>EN4</sub> =0V                                                 |      |      |      |        |

|                               |                        | Ta=-40°C to +125°C                                                   |      |      |      |        |

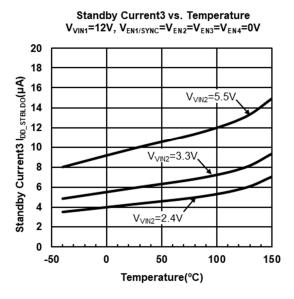

|                               |                        | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      |        |

|                               |                        | V <sub>EN2</sub> =0V                                                 | _    | _    | 15   |        |

| Standby Current 3             |                        | V <sub>EN3</sub> =0V                                                 |      |      |      |        |

|                               |                        | V <sub>EN4</sub> =0V                                                 |      |      |      | _      |

| (LDOVIN)                      | I <sub>DD_STBLDO</sub> | V <sub>EN1/SYNC</sub> =0V                                            |      |      |      | μΑ     |

| ,                             |                        | V <sub>EN2</sub> =0V                                                 |      |      | 00   |        |

|                               | · · ·                  | V <sub>EN3</sub> =0V                                                 | _    | _    | 20   | 0      |

|                               |                        | V <sub>EN4</sub> =0V                                                 |      |      |      |        |

|                               |                        | Ta=-40°C to +125°C                                                   |      |      |      |        |

#### THERMAL CHARACTERISTICS

| PARAMETER                  | SYMBOL | VALUE                | UNIT |

|----------------------------|--------|----------------------|------|

| Junction-to-ambient        | Qia    | 146.3 <sup>(3)</sup> | °C W |

| Thermal resistance         | θја    | 50.5 <sup>(4)</sup>  | C/VV |

| Junction-to-Top of package | i+     | 6.1 <sup>(3)</sup>   | °C W |

| Characterization parameter | ψjt    | 0.8 <sup>(4)</sup>   | C/VV |

<sup>(3):</sup> Mounted on glass epoxy board.

(101.5×114.5×1.6mm:based on EIA/JEDEC standard,2layers, with Exposed Pad)

(101.5×114.5×1.6mm:based on EIA/JEDEC standard,4layers, with Exposed Pad)

(For 4Layers: Applying 99.5×99.5mm inner Cu area and a thermal via holes to a board based on JEDEC standard JESD51-5)

#### ■ POWER DISSIPATION vs. AMBIENT TEMPERATURE

<sup>(4):</sup> Mounted on glass epoxy board.

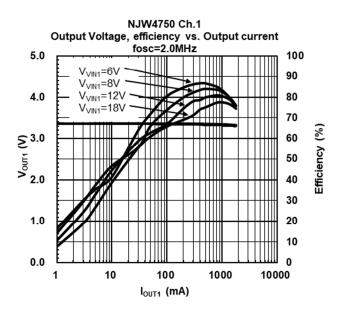

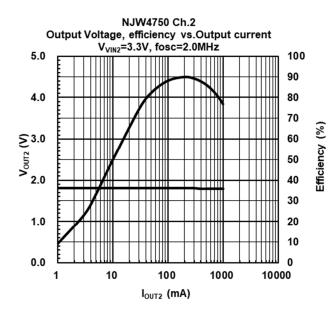

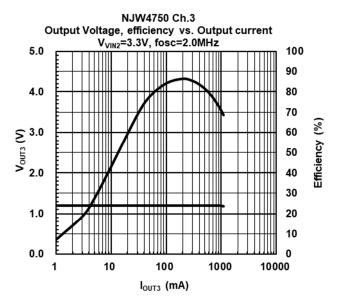

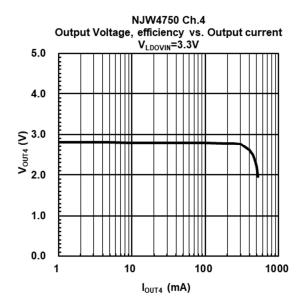

#### ■ TYPICAL CHARACTERISTICS

New Japan Radio Co., Ltd.

#### TYPICAL CHARACTERISTICS

Ver.1.0

New Japan Radio Co., Ltd.

- 19 www.njr.com

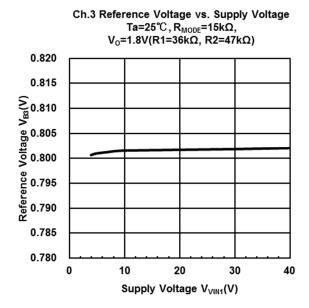

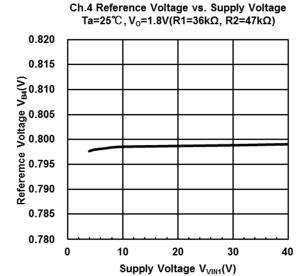

### **■ TYPICAL CHARACTERISTICS**

#### **■ TYIPICAL CHARACTERISTICS**

Ver.1.0

#### **■ TYPICAL CHARACTERISTICS**

### **■ TYPICAL CHARACTERITICS**

New Japan Radio Co., Ltd. www.njr.com

- 23 -

#### TYPICAL CHARACTERISTICS

New Japan Radio Co., Ltd. www.njr.com

- 24 -

#### **■ TYPICAL CHARACTERISTICS**

- 25 -

New Japan Radio Co., Ltd. www.njr.com

r com

#### **■ TYPICAL CHARACTERISTICS**

New Japan Radio Co., Ltd.

www.njr.com - 26 -

#### **■ TYIPICAL CHARACTERISTICS**

Ver.1.0

## ■ INTRODUCTION

# **Technical Information**

Please note the following when using NJW 4750.

- The NJW 4750 can operate each Ch. independently.

However, even if Ch.1 is not used, it is necessary to input a power supply to VIN1 pin.

- Ch.3 (LDOMODE) and Ch.4 need to be start-up after power Ch. becomes active.

The LDO may not be start-up by the protection function.

e.g. The case of using Ch.1 as a power supply for Ch.4.

It becomes the start of Ch.4 after normal start of Ch.1 by connecting PG1 pin of Ch.1 to EN4 pin of Ch.4.

## **■ PIN DESCRIPTION**

| PIN NO. | SYMBOL                                                                                             | DESCRIPTION                                                                                                                         |  |  |

|---------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | GND                                                                                                | Ground pin.                                                                                                                         |  |  |

| 2       | EN3                                                                                                | This pin controls the operation and stop of Ch.3. High Level: operation, Low level or Open level: Standby mode.                     |  |  |

| 2       | FD2                                                                                                | This pin detects the output voltage of Ch.3.                                                                                        |  |  |

| 3       | FB3                                                                                                | The output voltage is divided and inputted so that the FB pin voltage becomes 0.8V same as the reference voltage.                   |  |  |

| 4       | NC                                                                                                 | Non connection.                                                                                                                     |  |  |

| 5       | FB2                                                                                                | This pin detects the output voltage of Ch.2.                                                                                        |  |  |

|         | T DZ                                                                                               | The output voltage is divided and inputted so that the FB pin voltage becomes 0.8V same as the reference voltage.                   |  |  |

| 6       | EN2                                                                                                | This pin controls the operation and stop of Ch.2. High Level: operation, Low level or Open level: Standby mode.                     |  |  |

| 7       | RT                                                                                                 | Oscillation frequency setting pin by Timing Resistor. Oscillating frequency should set between 280kHz and 2.4MHz.                   |  |  |

| 8       | GND                                                                                                | Ground pin.                                                                                                                         |  |  |

| 9       | PG1                                                                                                | Power-good output of Ch.1 configured with open drain.                                                                               |  |  |

| 10      | MODE                                                                                               | This pin is used to determine the operation mode. Connect an open or mode setting resistor.                                         |  |  |

| 11      | FB1                                                                                                | This pin detects the output voltage of Ch.1.                                                                                        |  |  |

|         | 101                                                                                                | The output voltage is divided and inputted so that the FB pin voltage becomes 0.8V same as the reference voltage.                   |  |  |

| 12      | EN1/SYNC                                                                                           | This pin controls the operation and stop of Ch.1. High Level: operation, Low level or Open level: Standby mode.                     |  |  |

|         | LIVI/OTIVO                                                                                         | By inputting the clock signal, it operates synchronized with the input signal.                                                      |  |  |

| 13      | VIN1                                                                                               | Power supply input for IC and Ch.1.                                                                                                 |  |  |

|         | VII VI                                                                                             | Since the impedance of the power supply path needs to be lowered connecting a capacitor $(C_{IN})$ near the IC is required.         |  |  |

| 14      | GND                                                                                                | Ground pin.                                                                                                                         |  |  |

| 15      | SW1                                                                                                | Ch.1 Output.                                                                                                                        |  |  |

| 16      | EN4                                                                                                | This pin controls the operation and stop of Ch.4. High Level: operation, Low level or Open level: Standby mode.                     |  |  |

| 17      | LDOVOUT                                                                                            | Ch.4 Output                                                                                                                         |  |  |

| 18      | FB4                                                                                                | This pin detects the output voltage of Ch.4.                                                                                        |  |  |

|         |                                                                                                    | The output voltage is divided and inputted so that the FB pin voltage becomes 0.8V same as the reference voltage.                   |  |  |

| 19      | LDOVIN                                                                                             | Power supply input for Ch.4.                                                                                                        |  |  |

|         |                                                                                                    | Since the impedance of the power supply path needs to be lowered connecting a capacitor (C <sub>IN</sub> ) near the IC is required. |  |  |

| 20      | PG4                                                                                                | Power-good output of Ch.4 configured with open drain.                                                                               |  |  |

| 21      | GND                                                                                                | Ground pin.                                                                                                                         |  |  |

| 22      | SW2                                                                                                | Ch.2 Output.                                                                                                                        |  |  |

| 23      | PG2                                                                                                | Power-good output of Ch.2 configured with open drain.                                                                               |  |  |

| 24      | VIN2                                                                                               | Power supply input for Ch.2 and Ch.3.                                                                                               |  |  |

|         |                                                                                                    | Since the impedance of the power supply path needs to be lowered connecting a capacitor (C <sub>IN</sub> ) near the IC is required. |  |  |

| 25      | PG3                                                                                                | Power-good output of Ch.3 configured with open drain.                                                                               |  |  |

| 26      | SW3                                                                                                | Ch.3 Output.                                                                                                                        |  |  |

| Exposed | <ul> <li>Exposed PAD on backside should be connected to the ground and soldered to PCB.</li> </ul> |                                                                                                                                     |  |  |

| PAD     |                                                                                                    | <u> </u>                                                                                                                            |  |  |

# **Technical Information**

#### **■ DESCRIPTION OF BLOCK FEATURES**

#### 1. Mode setting

By connecting the resistor between the MODE pin and GND, the operation mode of Ch.3 and protection type of OCP are selected.(Table 1)

Table 1 The NJW4750 operation mode and setting resistor value.

| MODE | J     | resistor<br>(±5%)<br>Max | Ch.3    | OCP Mode                 | MODE Pin<br>Output Voltage<br>(±5%) |

|------|-------|--------------------------|---------|--------------------------|-------------------------------------|

| 1    | ор    | en                       | LDO     | Latch                    | 2.5V                                |

| 2    | 82kΩ  | 110kΩ                    | SW reg. | Latch                    | 1.4V                                |

| 3    | 27kΩ  | 39kΩ                     | SW reg. | Hiccup(SW) Foldback(LDO) | 1.2V                                |

| 4    | 6.8kΩ | 15kΩ                     | LDO     | Hiccup(SW) Foldback(LDO) | 1.0V                                |

The mode setting can be set only at startup, and the state of the mode can be checked by pin voltage.

- 2. Basic functions of switching regulator. (Ch.1,2 and Ch.3)

- Error Amplifier Section (Error AMP)

- 0.8V±1% precise reference voltage is connected to the non-inverted input of this section.

The output voltage can be set by dividing the output of the converter and connecting to the inverted input (FB pin).

• PWM comparator section (PWM), oscillating circuit Section (OSC)

Oscillating frequency can be set by inserting resistor between the RT pin and GND.

Table 2 shows example of oscillating frequency and timing resistor. The resistance is adapted to a series of E24 and a series of E96.

Please set the oscillating frequency according to Table 2

Table 2 The NJW4750 oscillating frequency and timing resistor value

| Oscillating | Timing      | Oscillating | Timing      |

|-------------|-------------|-------------|-------------|

| Frequency   | Resistor    | Frequency   | Resistor    |

| (kHz)       | $(k\Omega)$ | (kHz)       | $(k\Omega)$ |

| 280         | 27          | 1200        | 5.6         |

| 380         | 20          | 1750        | 3.9         |

| 500         | 15          | 2000        | 3.0         |

| 700         | 10          | 2250        | 2.0         |

| 1000        | 6.8         | 2400        | 1.8         |

NJW4750 is limited in minimum ON time and minimum OFF time, refer to electrical characteristics. Maximum duty cycle is 100%.

When you design the application, please refer to "Application information - Oscillating frequency setting".

## ■ DESCRIPTION OF BLOCK FEATURES (Continued)

# **Technical Information**

#### Power MOSFET

The power is stored in the inductor by the switch operation of built-in power MOSFET. The switching current is limited by the overcurrent protection function.

### Power supply, GND pin(VIN, GND)

Current flows into the IC according to drive frequency in a switching element. When impedance of a power supply line is high, power supply will be unstably, and the performance of the IC can't be drawn out sufficiently.

Therefore, since the impedance of the power supply path needs to be lowered connecting a capacitor  $(C_{IN})$  near the IC is required.

### 3. Additional and protection functions of switching regulator. (Ch.1,2 and Ch.3 are similar)

## Under voltage lockout (UVLO)

The UVLO circuit stops the IC operation in a low power supply voltage case, and when a power supply voltage becomes higher voltage than threshold, then the IC operation starts.

The threshold voltage has a hysteresis voltage width at rising and falling. A flutter of detection and release of UVLO is prevented by it.

#### · Soft start function

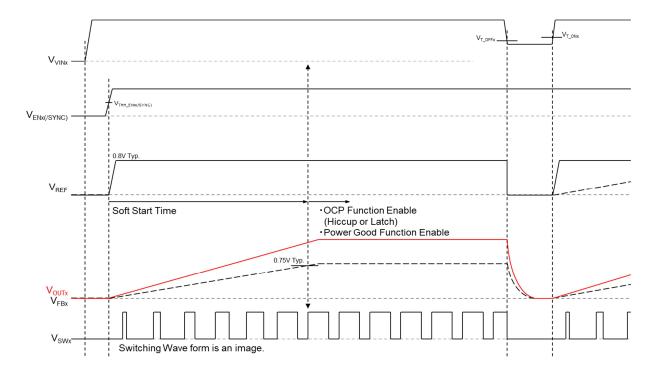

The output voltage of the converter gradually rises to a set value by the soft start function. The soft start time is 4ms (max.). It is defined with the time of the error amplifier reference voltage becoming from 0V to 0.75V.(Fig.1) Soft start operating condition.

- Ch.1:  $V_{VIN1} \ge V_{T\_ON1}$ ,  $V_{EN1} \ge V_{THH\_EN1}$

- Ch.2:  $V_{VIN1} \ge V_{T\_ON1}$ ,  $V_{VIN2} \ge V_{T\_ON2}$ ,  $V_{EN2} \ge V_{THH\_EN2}$

- Ch.3: V<sub>VIN1</sub>≧V<sub>T ON1</sub>, V<sub>VIN2</sub>≧V<sub>T ON2</sub>, V<sub>EN3</sub>≧V<sub>THH EN3</sub>

Also thermal shutdown must be disabled.

Fig.1 Soft start timing chart

# ■ DESCRIPTION OF BLOCK FEATURES (Continued)

# **Technical Information**

- Over current protection circuit (OCP) (Ch.1,2 and Ch.3 are similar)

Switching regulator block of NJW4750 has 2 kinds of overcurrent protection function.

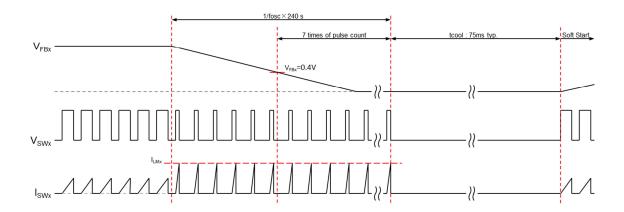

- 1. Hiccup (Fig.2):

Switching operation is reduced and output is restricted. When the load state normally returns, it is reset automatically.

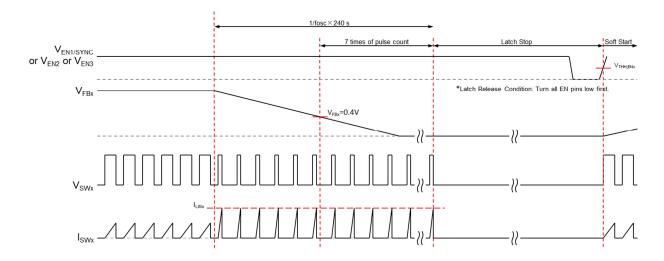

- 2. Latch (Fig.3):

- The function as the power supply is suspended.

- Latch is released by setting all EN pin to Low or VIN1 pin to 0 V.

- \* Hiccup system is each Ch. Independent control. Latch system suspends all output of IC.

#### Operating condition of OCP

In the soft start operating, Hiccup/Latch becomes ineffective.

The overcurrent protection function operates when one of them of 2 conditions was formed.

- V<sub>FBx</sub>≤0.4V and 7cycle over current detection continuously.

- Overcurrent detection continuously of 1/fosc×240 s.

Fig.2 Hiccup mode OCP timing chart

Fig.3 Latch mode OCP timing chart

# **DESCRIPTION OF BLOCK FEATURES (Continued)**

# **Technical Information**

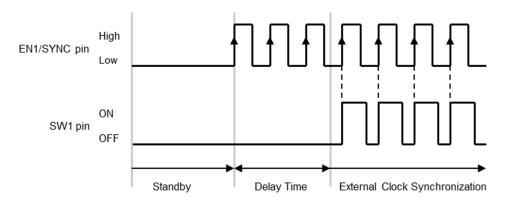

• External clock synchronization (Ch.1,2 and Ch.3)

By inputting a square wave to EN1/SYNC pin, the oscillator of NJW4750 can be synchronized to an external frequen-

The input square wave must be on the following specification. (Table 3)

Table 3 The input square wave to EN1/SYNC pin.

|                 | Condition                                      |

|-----------------|------------------------------------------------|

| Input Fraguanay | f <sub>OSC</sub> ×0.9 to f <sub>OSC</sub> ×1.7 |

| Input Frequency | Upper limit 2,800kHz                           |

| Duty Cycle      | 40% to 60%                                     |

| Voltage         | 1.6V or more (High level)                      |

| Magnitude       | 0.4V or less (Low level)                       |

Fig.4 Switching operation by external synchronized clock

Ver.1.0

# ■ DESCRIPTION OF BLOCK FEATURES (Continued)

# **Technical Information**

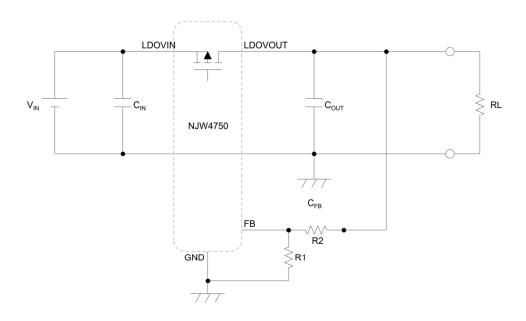

- 4. Basic functions of LDO (Ch.3 LDO MODE and Ch.4)

- Error amplifier section (Error AMP)

- 0.8V±1% precise reference voltage is connected to the non-inverted input of this section.

The output voltage can be set by dividing the output of the converter and connecting to the inverted input (FB pin).

- 5. Additional and protection functions of LDO (Ch.3 LDO MODE and Ch.4)

- Over current protection circuit(OCP)

LDO block of NJW4750 can choose 2 kinds of overcurrent protection function.

Fold back:

Limits the output current as the output voltage decreases.

2. Latch:

The function as the power supply is suspended at  $V_{\text{FBx}} \leq 0.4 V$ .

Latch is released by setting all EN pin to Low or VIN1 pin to 0V.

※ Fold back system is independent each Ch. Latch system suspends all output of IC.

- 6. Common protection function / features

- Thermal shutdown function (TSD)

When junction temperature of the NJW4750 exceeds the 160°C\*, internal thermal shutdown circuit function stops SW function. When junction temperature decreases to 145°C\* or less, SW operation re-start from the soft start operation. The purpose of this function is to prevent malfunctioning of IC at the high junction temperature.

Therefore it is not something that urges positive use. Please make sure to operate within the junction temperature range rated (-40°C to 150°C). (\* Design value)

· Standby function

Each Ch. stops the operating and becomes standby status when the ENx(/SYNC) pin becomes less than 0.4V. The ENx(/SYNC) pins are internally pulled down with resistor (CH1 :5M $\Omega$ , CH2 :500k $\Omega$ , CH3 :500k $\Omega$ , CH4 :500k $\Omega$ ), therefore the NJW4750 becomes standby mode when it is OPEN. Please connect this pin to VINx when you do not use standby function.

# ■ DESCRIPTION OF BLOCK FEATURES (Continued)

# **Technical Information**

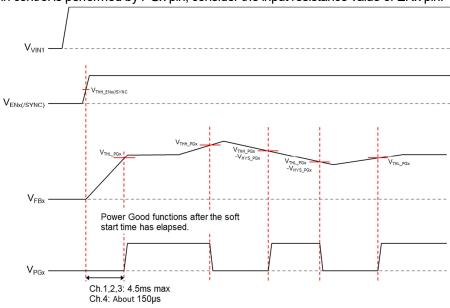

• Power Good function

It monitors the output status and outputs a signal from PGx pin that is internally connected to an open drain of MOSFET.

If the FB pin is within the range of -7% to + 15% of the error amplifier reference voltage, the PG pin becomes high impedance and notifies that the output voltage is normal. Otherwise the PG pin becomes low level and tells the output voltage is abnormal.

After soft start time, the Power Good function becomes effective in Ch.1, Ch.2, and Ch.3.

The Power Good function of Ch.4 becomes effective after passage for 150µs from EN4: H(@LDOVIN=3.3V).

When ENx pin control is performed by PGx pin, consider the input resistance value of ENx pin.

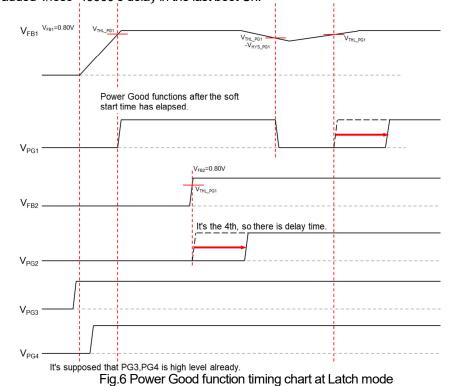

Fig.5 Power Good function timing chart

• Latch mode: added 1/fosc×40000 s delay in the last boot Ch.

# ■ APPLICATION INFORMATION(Switching regulator)

# **Technical Information**

#### · Oscillating frequency setting

When a switching frequency is high, a small inductor and capacitor are available.

If oscillating frequency is high, decrease in efficiency and a limit of the minimum ON time and minimum OFF time are demerit.

The buck converter of ON time and OFF time is decided the following formula.

$$t_{ON} = \frac{(V_{OUT} + V_L)}{(V_{IN} - V_{SWH} + V_L) \times f_{OSC}}[s]$$

$$t_{OFF} = \frac{1}{f_{OSC}} - t_{ON}[s]$$

V<sub>IN</sub>: Input voltage

V<sub>OUT</sub>: Output voltage

V<sub>SWH</sub>: High-side saturation voltage

$V_L$ : Catch Diode  $V_f$  or Lo-side saturation voltage  $V_{\text{SWL}}$

When the ON time becomes shorter than  $t_{ON-MIN}$  or OFF time becomes shorter than  $t_{OFF-MIN}$ , a change of duty or pulse skip operation may be performed in order to maintain output voltage at a stable state.

#### Inductors

Since a large current flows into an inductor, please select an appropriate inductor such as not saturate in the application.

Inductors have an important role in slope compensation.

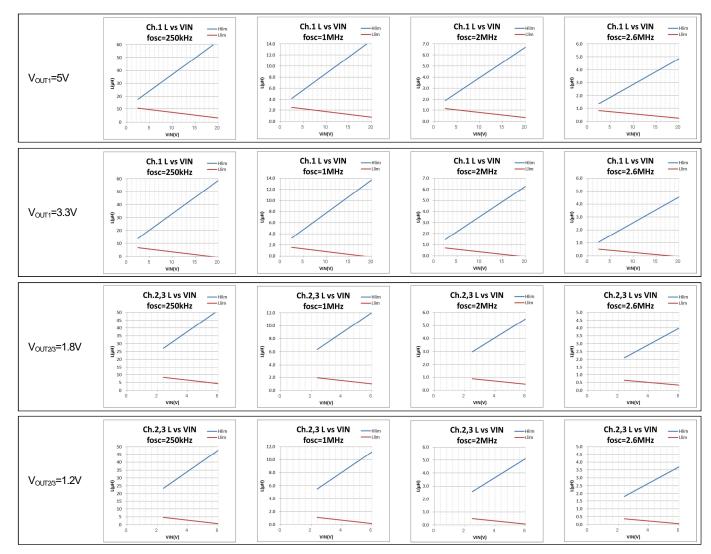

Inductor value is limited selection by supply voltage and oscillation frequency. Recommended selection of the inductor value is between Hlim. and Llim. shown in Fig.8.

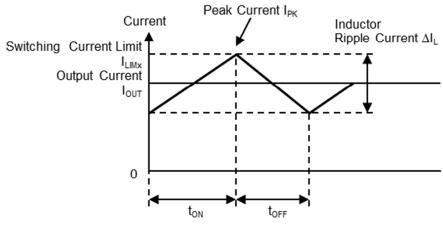

The maximum Output current of worst condition is decided the following formula.

$$\Delta I_{L} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{L \times V_{IN} \times f_{OSC}} [A]$$

$$I_{OUT} = I_{LIMx(MIN)} - \frac{\Delta I_L}{2} [A]$$

Fig.7 Inductor current state transition (Continuous conduction mode)

# APPLICATION INFORMATION(Switching regulator)

# **Technical Information**

Fig.8 Inductance range.

#### · Input capacitor

Transient current which is responsive to frequency flows into the input section of a switching regulator. When impedance of a power supply line is high, power supply will be unstably, and the performance of the IC can't be drawn out sufficiently.

Therefore, since the impedance of the power supply path needs to be lowered connecting a capacitor  $(C_{IN})$  near the IC is required.

The effective input current can be expressed by the following formula.

$$I_{\text{RMS}} = I_{\text{OUT}} \times \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}}{V_{\text{IN}}} [A_{\text{rms}}]$$

In the above formula, the maximum current is obtained when  $V_{IN}=2\times V_{OUT}$ , and the result in this case is  $I_{RMS}=I_{OUT(MAX)}\div 2$ . When the input capacitor in selecting, please carry out an evaluation based on an application, and decide a capacitor value that has adequate margin.

### ■ APPLICATION INFORMATION(Switching regulator)

# **Technical Information**

· Output capacitor

An output capacitor stores power from the inductor, and stabilizes voltage provided to the output.

The NJW4750 is designed phase compensation so that output capacitor of low ESR can be used. Therefore a ceramic capacitor is the most suitable.

Since capacity of a ceramic capacitor may decline by DC supply voltage and temperature change, please confirm it's characteristics on specification sheet.

When selecting an output capacitor, must be considered Equivalent Series Resistance (ESR) characteristics, ripple current, and breakdown voltage.

In case of using a low ESR capacitor, it's possible to lower the ripple voltage.

The output ripple noise can be expressed by the following formula.

$$V_{ripple(p-p)} = \Delta I_{L} \times \left( ESR + \frac{1}{8 \times f_{OSC} \times C_{OUT}} \right) [V]$$

The effective ripple current that flows in a capacitor (I<sub>RMS</sub>) is obtained by the following equation.

$$I_{RMS} = \frac{\Delta I_L}{2\sqrt{3}} [A_{rms}]$$

· Setting of phase compensation

The NJW 4750 has a built-in phase compensation circuit.

Table 4 shows the values of extern al parts based on oscillation frequency and output voltage.

Table 4 Value of phase compensation

| f <sub>OSC</sub> | V <sub>OUT</sub>              | C <sub>OUT</sub> | C <sub>FB</sub> | $R_{FB}$ | R2                         |

|------------------|-------------------------------|------------------|-----------------|----------|----------------------------|

| 1MHz or more     | 2.5V, 2.8V, 3.3V,<br>3.6V, 5V | 10µF or more     | 22pF            | 1kΩ      | 30kΩ to 82kΩ               |

|                  | 1.8V                          | 22µF or more     | 22pF            | 1kΩ      | $30k\Omega$ to $82k\Omega$ |

|                  | 1.1V*, 1.2V*                  | 47μF or more     | 22pF            | 1kΩ      | 30kΩ to 82kΩ               |

| 500kHz or less   | ALL                           | 100µF or more    | open            | open     | 30kΩ to 82kΩ               |

<sup>\*</sup> V<sub>VIN2</sub> is 4 V or less.

If  $V_{\text{VIN2}}$  is set to higher than 4 V, the oscillating frequency is limited up to 1.5MHz.

### APPLICATION INFORMATION(Switching regulator)

# **Technical Information**

#### · Catch diode

When the switch element is in OFF cycle, the power stored in the inductor flows to the output capacitor via the catch diode. Therefore an electric current according to the load current flows to the diode every cycle. Since a diode's forward saturation voltage and current accumulation cause power loss, a Schottky Barrier Diode (SBD), which has a low forward saturation voltage, is most suitable.

When select the SBD, the reverse current at the high temperature is important, too.

The characteristic of SBD has a high reverse current than a general diode. If the reverse current is large, it leads to the loss of the diode, so check the specification of the SBD

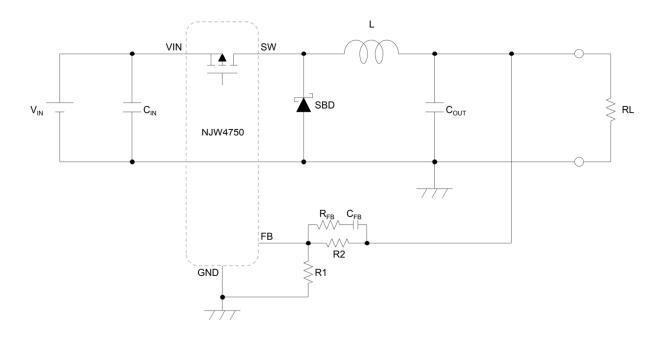

### Setting output voltage

The output voltage V<sub>OUT</sub> is determined by the relative resistances of R1, R2.

$$V_{OUT} = \left(\frac{R2}{R1} + 1\right) \times V_B[V]$$

Fig.9 Output voltage setting

### ■ APPLICATION INFORMATION(Switching regulator)

# **Technical Information**

#### Board layout

In the switching regulator application, since the current flow according to the oscillating frequency, the substrate (PCB) layout is very important.

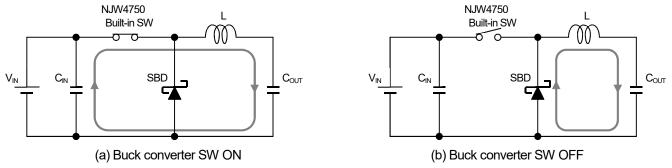

Therefore, a current flowing line must be wide and short as much as possible. Fig.10 shows a current loop of a step-down converter. (In case of synchronous rectification, SBD is changed to built-in SW.)

Especially, the loop of  $C_{IN}$  - SW - SBD which has a high frequency switching, is necessary to configure minimum loop as top priority. It is effective in reducing of spike noise caused by parasitic inductor.

Fig.10 Current loop of buck converter

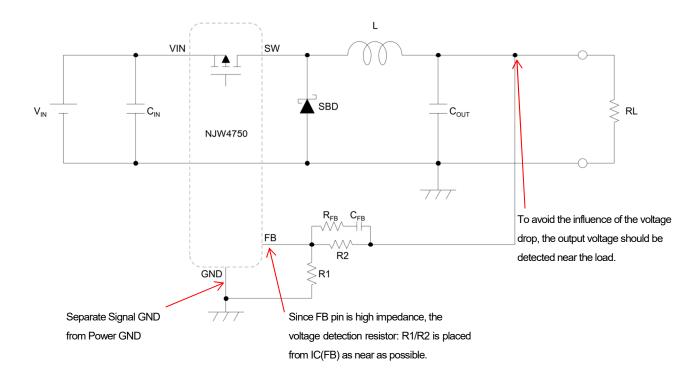

About concerning the GND, it is preferred to separate the power GND and the signal GND, and use single ground point.

The voltage sensing feedback line should be away as far away as possible from the inductor. Since this line has high impedance, it is laid out to avoid the influence noise caused by leakage flux from the inductor.

Fig.11 shows example of wiring at buck converter.