## **FEATURES**

- 1.8GHz min. count frequency

- Extended 100E VEE range of -4.2V to -5.5V

- Synchronous and asynchronous enable pins

- Differential clock input and data output pins

- VBB output for single-ended use

- Asynchronous Master Reset

- Internal 75K $\Omega$  input pull-down resistors

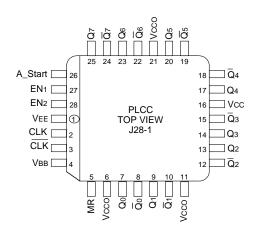

- Available in 28-pin PLCC packge

### **PIN NAMES**

| Pin                                | Function                   |

|------------------------------------|----------------------------|

| CLK, CLK                           | Differential Clock Inputs  |

| Q0–Q7, \overline{Q}0-\overline{Q}7 | Differential Q Outputs     |

| A_Start                            | Asynchronous Enable Input  |

| EN1, EN2                           | Synchronous Enable Inputs  |

| MR                                 | Asynchronous Master Reset  |

| VBB                                | Switching Reference Output |

| Vcco                               | Vcc to Output              |

## **DESCRIPTION**

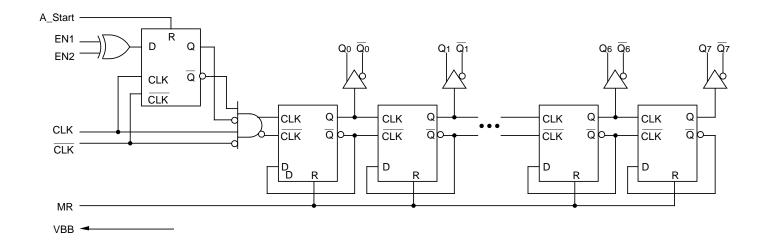

The SY10/100E137 are very high speed binary ripple counters. The two least significant bits were designed with very fast edge rates, while the more significant bits maintain standard ECLinPS output edge rates. This allows the counters to operate at very high frequencies, while maintaining a moderate power dissipation level.

The devices are ideally suited for multiple frequency clock generation, as well as for counters in high-performance ATE time measurement boards.

Both asynchronous and synchronous enables are available to maximize the device's flexibility for various applications. The asynchronous enable input, A Start, when asserted, enables the counter while overriding any synchronous enable signals. The E137 features XOR'ed enable inputs, EN1 and EN2, which are synchronous to the CLK input. When only one synchronous enable is asserted, the counter becomes disabled on the next CLK transition. All outputs remain in the previous state poised for the other synchronous enable or A Start to be asserted in order to re-enable the counter. Asserting both synchronous enables causes the counter to become enabled on the next transition of the CLK. EN1 (or EN2) and CLK edges are coincident. Sufficient delay has been inserted in the CLK path (to compensate for the XOR gate delay and the internal D-flip-flop set-up time) to ensure that the synchronous enable signal is clocked correctly; hence, the counter is disabled.

The E137 can also be driven single-endedly utilizing the VBB output supply as the voltage reference for the CLK input signal. If a single-ended signal is to be used, the VBB pin should be connected to the  $\overline{\text{CLK}}$  input and bypassed to ground via a  $0.01\mu\text{F}$  capacitor. VBB can only source/sink 0.5mA; therefore, it should be used as a switching reference for the E137 only.

All input pins left open will be pulled LOW via an input pull-down resistor. Therefore, do not leave the differential CLK inputs open. Doing so causes the current source transistor of the input clock gate to become saturated, thus upsetting the internal bias regulators and jeopardizing the stability of the device.

The asynchronous Master Reset resets the counter to an all zero state upon assertion.

# PACKAGE/ORDERING INFORMATION

28-Pin PLCC (J28-1)

# Ordering Information<sup>(1)</sup>

| Part Number                     | Package<br>Type | Operating<br>Range | Package<br>Marking                          | Lead<br>Finish |

|---------------------------------|-----------------|--------------------|---------------------------------------------|----------------|

| SY10E137JC                      | J28-1           | Commercial         | SY10E137JC                                  | Sn-Pb          |

| SY10E137JCTR <sup>(2)</sup>     | J28-1           | Commercial         | SY10E137JC                                  | Sn-Pb          |

| SY100E137JC                     | J28-1           | Commercial         | SY100E137JC                                 | Sn-Pb          |

| SY100E137JCTR <sup>(2)</sup>    | J28-1           | Commercial         | SY100E137JC                                 | Sn-Pb          |

| SY10E137JZ <sup>(3)</sup>       | J28-1           | Commercial         | SY10E137JZ with Pb-Free bar-line indicator  | Matte-Sn       |

| SY10E137JZTR <sup>(2, 3)</sup>  | J28-1           | Commercial         | SY10E137JZ with Pb-Free bar-line indicator  | Matte-Sn       |

| SY100E137JZ <sup>(3)</sup>      | J28-1           | Commercial         | SY100E137JZ with Pb-Free bar-line indicator | Matte-Sn       |

| SY100E137JZTR <sup>(2, 3)</sup> | J28-1           | Commercial         | SY100E137JZ with Pb-Free bar-line indicator | Matte-Sn       |

#### Notes

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A$  = 25°C, DC Electricals only.

- 2. Tape and Reel.

- 3. Pb-Free package is recommended for new designs.

## **BLOCK DIAGRAM**

# SEQUENTIAL TRUTH TABLE(1)

| Function     | EN <sub>1</sub> | EN <sub>2</sub> | A_Start | MR | CLK | Q7 | Q <sub>6</sub> | Q5 | Q4 | Q3 | Q2 | Q1 | Qo |

|--------------|-----------------|-----------------|---------|----|-----|----|----------------|----|----|----|----|----|----|

| Reset        | Х               | Х               | Х       | Н  | Х   | L  | L              | L  | L  | L  | L  | L  | L  |

| Count        | L               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | L  | L  | H  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | L  | H  | L  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | L  | H  | H  |

| Stop         | H               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | L  | H  | H  |

|              | H               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | L  | H  | H  |

| Async. Start | H               | L               | H       | L  | Z   | L  | L              | L  | L  | L  | H  | L  | L  |

|              | H               | L               | H       | L  | Z   | L  | L              | L  | L  | L  | H  | L  | H  |

|              | L               | L               | H       | L  | Z   | L  | L              | L  | L  | L  | H  | H  | L  |

| Count        | L               | L               | L       | L  | Z   | L  | L              | L  | L  | L  | H  | H  | H  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | L  | L  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | L  | H  |

| Stop         | L               | H               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | L  | H  |

|              | L               | H               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | L  | H  |

| Sync. Start  | H               | H               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | H  | L  |

|              | H               | H               | L       | L  | Z   | L  | L              | L  | L  | H  | L  | H  | H  |

|              | H               | H               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | L  | L  |

| Stop         | H               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | L  | L  |

|              | H               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | L  | L  |

| Count        | L               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | L  | H  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | H  | L  |

|              | L               | L               | L       | L  | Z   | L  | L              | L  | L  | H  | H  | H  | H  |

| Reset        | Х               | Х               | Х       | Н  | Х   | L  | L              | L  | L  | L  | L  | L  | L  |

#### Note:

1. Z = LOW-to-HIGH transition

# DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|        |                             |             | TA = 0°C       |            |                | TA = +25°C |            |                | TA = +85°C |            |                |      |           |

|--------|-----------------------------|-------------|----------------|------------|----------------|------------|------------|----------------|------------|------------|----------------|------|-----------|

| Symbol | Parameter                   |             | Min.           | Тур.       | Max.           | Min.       | Тур.       | Max.           | Min.       | Тур.       | Max.           | Unit | Condition |

| Vвв    | Output Reference<br>Voltage | 10E<br>100E | -1.38<br>-1.38 |            | -1.27<br>-1.26 |            |            | -1.25<br>-1.26 | _          |            | -1.19<br>-1.26 | V    | _         |

| lін    | Input HIGH Current          |             | _              | _          | 150            | _          | _          | 150            | _          | _          | 150            | μΑ   | _         |

| IEE    | Power Supply<br>Current     | 10E<br>100E | _              | 121<br>121 | 145<br>145     |            | 121<br>121 | 145<br>145     | _          | 121<br>139 | 145<br>167     | mA   | _         |

# **AC ELECTRICAL CHARACTERISTICS**

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|            |                                      | TA = 0°C |      |      | TA = +25°C |      |      | TΔ   | · = +85° | °C   |      |           |

|------------|--------------------------------------|----------|------|------|------------|------|------|------|----------|------|------|-----------|

| Symbol     | Parameter                            | Min.     | Тур. | Max. | Min.       | Тур. | Max. | Min. | Тур.     | Max. | Unit | Condition |

| fCOUNT     | Max. Count Frequency                 | 1800     | 2200 | _    | 1800       | 2200 |      | 1800 | 2200     |      | MHz  | _         |

| tPD        | Propagation Delay to Output          |          |      |      |            |      |      |      |          |      | ps   | _         |

|            | CLK to Q <sub>0</sub>                | 1300     | 1700 | 2150 | 1300       | 1700 | 2150 | 1350 | 1750     | 2200 |      |           |

|            | CLK to Q1                            | 1600     | 2025 | 2500 | 1600       | 2050 | 2500 | 1650 | 2100     | 2550 |      |           |

|            | CLK to Q2                            | 1950     | 2425 | 2925 | 1950       | 2450 | 2925 | 2025 | 2500     | 3000 |      |           |

|            | CLK to Q <sub>3</sub>                | 2275     | 2750 | 3350 | 2275       | 2775 | 3350 | 2350 | 2850     | 3425 |      |           |

|            | CLK to Q4                            | 2625     |      | 3750 | 2625       | 3150 | 3750 | 2700 | 3225     | 3625 |      |           |

|            | CLK to Q5                            | 2950     | 3450 | 4150 | 2950       | 3475 | 4150 | 3050 | 3550     | 4250 |      |           |

|            | CLK to Q <sub>6</sub>                | 3250     | 3775 | 4450 | 3250       | 3800 | 4450 | 3375 | 3925     | 4600 |      |           |

|            | CLK to Q7                            | 3575     | 4075 | 4800 | 3575       |      | 4800 | 3700 | 4250     | 4950 |      |           |

|            | A_Start to Q <sub>0</sub>            | 950      | 1325 | 1700 | 950        | 1325 | 1700 | 950  | 1325     | 1700 |      |           |

|            | MR to Q <sub>0</sub>                 | 700      | 1000 | 1300 | 700        | 1000 | 1300 | 700  | 1000     | 1300 |      |           |

| ts         | Set-up Time (EN1, EN2)               | 0        | -150 | _    | 0          | -150 | _    | 0    | -150     |      | ps   | _         |

| tH         | Hold Time (EN1, EN2)                 | 300      | 150  | _    | 300        | 150  | _    | 300  | 150      |      | ps   | _         |

| trr        | Reset Recovery Time<br>MR, A_Start   | 400      | 200  | _    | 400        | 200  | _    | 400  | 200      |      | ps   | _         |

| tPW        | Minimum Pulse Width CLK, MR, A_Start | 400      | _    | _    | 400        |      |      | 400  |          | 1    | ps   | _         |

| VPP        | Minimum Input Swing (CLK)            | 0.25     | _    | 1.0  | 0.25       | _    | 1.0  | 0.25 | _        | 1.0  | V    | 1         |

| VCMR       | Com. Mode Range (CLK)                | -0.4     |      | -2.0 | -0.4       | _    | -2.0 | -0.4 | _        | -2.0 | V    | _         |

| tr         | Rise/Fall Time, 20% to 80%           |          |      |      |            |      |      |      |          |      | ps   | _         |

| <b>t</b> f | Q0, Q1                               | 150      | —    | 400  | 150        | —    | 400  | 150  | —        | 400  |      |           |

|            | Q2–Q7                                | 275      | —    | 600  | 275        | _    | 600  | 275  | _        | 600  |      |           |

### Note:

1. Minimum input swing for which AC parameters are guaranteed. Full DC ECL output swings will be generated with only 50mV input swings.

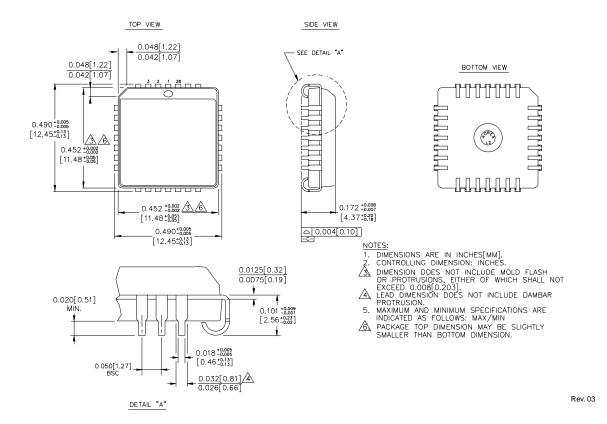

## 28-PIN PLCC (J28-1)

## MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.