# TPS775xx with RESET Output, TPS776xx with PG Output FAST-TRANSIENT-RESPONSE 500mA LOW-DROPOUT VOLTAGE REGULATORS

#### **FEATURES**

- Open Drain Power-On Reset with 200ms Delay (TPS775xx)

- Open Drain Power Good (TPS776xx)

- 500mA Low-Dropout Voltage Regulator

- Available in Fixed Output and Adjustable Versions

- Dropout Voltage to 169mV (Typ) at 500mA (TPS77x33)

- Ultralow 85µA Typical Quiescent Current

- Fast Transient Response

- 2% Tolerance Over Specified Conditions for Fixed-Output Versions

- 8-Pin SOIC and 20-Pin TSSOP PowerPAD™ (PWP) Packages

- Thermal Shutdown Protection

#### **APPLICATIONS**

- FPGA Power

- DSP Core and I/O Voltages

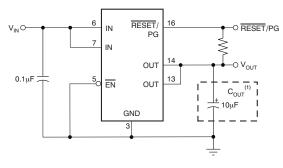

## Typical Application Circuit (Fixed Voltage Options)

#### DESCRIPTION

The TPS775xx and TPS776xx devices are designed to have a fast transient response and be stable with a  $10\mu F$  low ESR capacitor. This combination provides high performance at a reasonable cost.

Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 169mV at an output current of 500mA for the TPS77x33) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (typically 85 $\mu$ A over the full range of output current, 0mA to 500mA). These two key specifications yield a significant improvement in operating life for battery-powered systems. This LDO family also features a sleep mode; applying a TTL high signal to  $\overline{\text{EN}}$  (enable) shuts down the regulator, reducing the quiescent current to  $1\mu\text{A}$  at  $T_J = +25^{\circ}\text{C}$ .

The RESET output of the TPS775xx initiates a reset in microcomputer and microprocessor systems in the event of an undervoltage condition. An internal comparator in the TPS775xx monitors the output voltage of the regulator to detect an undervoltage condition on the regulated output voltage.

Power good (PG) of the TPS776xx is an active high output, which can be used to implement a power-on reset or a low-battery indicator.

The TPS775xx and TPS776xx are offered in 1.5V, 1.6V (TPS77516 only), 1.8V, 2.5V, 2.8V (TPS77628 only), and 3.3V fixed-voltage versions and in an adjustable version (programmable over the range of 1.5V to 5.5V for the TPS77501 and 1.2V to 5.5V for the TPS77601). Output voltage tolerance is specified as a maximum of 2% over line, load, and temperature ranges. The TPS775xx and TPS776xx families are available in 8-pin SOIC and 20-pin TSSOP packages.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| PRODUCT                                     | V <sub>OUT</sub> <sup>(2)</sup>                                                                                                          |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| TPS775xx <i>yyyz</i> , TPS776xx <i>yyyz</i> | XX is nominal output voltage (for example, 28 = 2.8V, 285 = 2.85V, 01 = Adjustable).  YYY is package designator.  Z is package quantity. |

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (2) Custom fixed output voltages are available; minimum order quantities may apply. Contact factory for details and availability.

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating temperature range (unless otherwise noted)(1)

| PARAMETER                                             | TPS775xx, TPS776xx | UNIT        |

|-------------------------------------------------------|--------------------|-------------|

| Input voltage range, V <sub>IN</sub> <sup>(2)</sup>   | -0.3 to +13.5      | V           |

| Voltage range at EN                                   | -0.3 to +16.5      | V           |

| Maximum RESET voltage (TPS775xx)                      | 16.5               | V           |

| Maximum PG voltage (TPS776xx)                         | 16.5               | V           |

| Peak output current                                   | Internally limited |             |

| Voltage range at OUT, FB                              | 7                  | V           |

| Continuous total power dissipation                    | See Dissipation Ra | tings Table |

| Operating junction temperature range, T <sub>J</sub>  | -40 to +125        | °C          |

| Storage junction temperature range , T <sub>STG</sub> | -65 to +150        | °C          |

| ESD rating, HBM                                       | 2                  | kV          |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### **DISSIPATION RATINGS**

| BOARD                 | PACKAGE | AIRFLOW<br>(CFM) | T <sub>A</sub> < +25°C (mW) | DERATING FACTOR<br>ABOVE T <sub>A</sub> = +25°C | T <sub>A</sub> = +70°C (mW) | T <sub>A</sub> = +85°C (mW) |

|-----------------------|---------|------------------|-----------------------------|-------------------------------------------------|-----------------------------|-----------------------------|

|                       | D       | 0                | 568                         | 5.68mW/°C                                       | 312                         | 227                         |

| _                     | D       | 250              | 904                         | 9.04mW/°C                                       | 497                         | 362                         |

| Low-K <sup>(1)</sup>  | PWP     | 0                | 2350                        | 23.5mW/°C                                       | 1300                        | 940                         |

| LOW-K\                | PVVP    | 300              | 3460                        | 34.6mW/°C                                       | 1900                        | 1400                        |

| High-K <sup>(2)</sup> | PWP     | 0                | 2380                        | 23.8mW/°C                                       | 1300                        | 952                         |

| Flight-K              | FVVP    | 300              | 5790                        | 57.9mW/°C                                       | 3200                        | 2300                        |

<sup>(1)</sup> This parameter is measured with the recommended copper heat sink pattern on a 1-layer, 5in x 5in printed circuit board (PCB), 1-ounce copper, 2in x 2in coverage (4in<sup>2</sup>).

<sup>(2)</sup> All voltages are with respect to network terminal ground.

<sup>(2)</sup> This parameter is measured with the recommended copper heat sink pattern on a 8-layer, 1.5in × 2in PCB, 1-ounce copper with layers 1, 2, 4, 5, 7, and 8 at 5% coverage (0.9in²) and layers 3 and 6 at 100% coverage (6in²). For more information, refer to TI technical brief SLMA002.

#### **ELECTRICAL CHARACTERISTICS**

Over recommended operating temperature range ( $T_J = -40^{\circ}\text{C}$  to +125°C),  $V_{IN} = V_{OUT(TYP)} + 1V$ ;  $I_{OUT} = 1\text{mA}$ ,  $V_{\overline{EN}} = 0V$ ,  $C_{OUT} = 10\mu\text{F}$ , unless otherwise noted. Typical values are at  $T_J = +25^{\circ}\text{C}$ .

|                                   | PARAMETER                                    |               | TEST CONDITIONS                                                                                                               | MIN  | TYP  | MAX  | UNIT             |

|-----------------------------------|----------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------------|

| V <sub>IN</sub>                   | Input voltage range                          |               |                                                                                                                               | 2.7  |      | 10   | V                |

|                                   | 0                                            | TPS77501      |                                                                                                                               | 1.5  |      | 5.5  | V                |

| $V_{OUT}$                         | Output voltage range                         | TPS77601      |                                                                                                                               | 1.2  |      | 5.5  | V                |

| V <sub>OUT</sub>                  | Accuracy                                     |               | $V_{OUT} + 1V \le V_{IN} \le 10V^{(1)}$<br>$10\mu A < I_{OUT} < 500mA$                                                        | -2.0 |      | +2.0 | %                |

| I                                 | Ground pin current                           |               | I <sub>OUT</sub> = 10mA                                                                                                       |      | 85   |      | μΑ               |

| I <sub>GND</sub>                  | Ground pin current                           |               | I <sub>OUT</sub> = 500mA                                                                                                      |      |      | 125  | μА               |

| $\Delta V_{OUT}\%/\Delta V_{IN}$  | Output voltage line regula                   | ation         | $V_{OUT} + 1V \le V_{IN} \le 10V^{(1)}$                                                                                       |      | 0.01 |      | %/V              |

| $\Delta V_{OUT}\%/\Delta I_{OUT}$ | Load regulation                              |               |                                                                                                                               |      | 3    |      | mV               |

| $V_N$                             | Output noise voltage<br>BW = 200Hz to 100kHz | TPS77x18      | $I_C = 500 \text{mA}, C_{OUT} = 10 \mu \text{F}$                                                                              |      | 53   |      | μV <sub>RM</sub> |

|                                   |                                              | TPS77628      | I <sub>OUT</sub> = 500mA                                                                                                      |      | 285  | 410  | mV               |

| $V_{DO}$                          | Dropout voltage (2)                          | TPS77533      | I <sub>OUT</sub> = 500mA                                                                                                      |      | 169  | 287  | mV               |

|                                   |                                              | TPS77633      | I <sub>OUT</sub> = 500mA                                                                                                      |      | 169  | 287  | mV               |

| I <sub>CL</sub>                   | Output current limit                         | •             | V <sub>OUT</sub> = 0V                                                                                                         | 1.2  | 1.6  | 1.9  | Α                |

| T <sub>SD</sub>                   | Shutdown temperature                         |               |                                                                                                                               |      | 150  |      | °C               |

| TJ                                | Operating junction tempe                     | rature range  |                                                                                                                               | -40  |      | +125 | °C               |

| I <sub>STBY</sub>                 | Standby current                              |               | $\overline{\text{EN}} = V_{\text{IN}}$ , at $T_{\text{J}} = +25^{\circ}\text{C}$ , $2.7\text{V} < V_{\text{IN}} < 10\text{V}$ |      | 1    |      | μА               |

|                                   | 5151                                         |               | EN = V <sub>IN</sub> , 2.7V < V <sub>IN</sub> < 10V                                                                           |      |      | 10   |                  |

| I <sub>FB</sub>                   | FB input current                             | TPS77x01      | FB = 1.5V                                                                                                                     |      | 2    |      | nA               |

| V <sub>EN(HI)</sub>               | High-level enable input vo                   | oltage        |                                                                                                                               | 1.7  |      |      | V                |

| V <sub>EN(LO)</sub>               | Low-level enable input vo                    | ltage         |                                                                                                                               |      |      | 0.9  | V                |

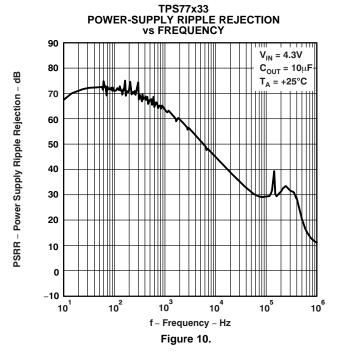

| PSRR                              | Power-supply ripple reject                   | tion          | f = 100Hz, C <sub>OUT</sub> = 10μF                                                                                            |      | 60   |      | dB               |

|                                   | Minimum input voltage fo                     | r valid RESET | I <sub>OUT(RESET)</sub> = 300μA                                                                                               |      | 1.1  |      | V                |

|                                   | Trip threshold voltage                       |               | V <sub>OUT</sub> decreasing                                                                                                   | 92   |      | 98   | %Vo              |

| RESET                             | Hysteresis voltage                           |               | Measured at V <sub>OUT</sub>                                                                                                  |      | 0.5  |      | %Vo              |

| (TPS775xx)                        | Output low voltage                           |               | V <sub>IN</sub> = 2.7V, I <sub>OUT(RESET)</sub> = 1mA                                                                         |      | 0.15 | 0.4  | V                |

|                                   | Leakage current                              |               | V <sub>(RESET)</sub> = 5V                                                                                                     |      |      | 1    | μΑ               |

|                                   | RESET time-out delay                         |               |                                                                                                                               |      | 200  |      | ms               |

|                                   | Minimum input voltage fo                     | r valid PG    | I <sub>OUT(PG)</sub> = 300μA                                                                                                  |      | 1.1  |      | V                |

|                                   | Trip threshold voltage                       |               | V <sub>OUT</sub> decreasing                                                                                                   | 92   |      | 98   | %V <sub>OI</sub> |

| PG<br>(TPS776xx)                  | Hysteresis voltage                           |               | Measured at V <sub>OUT</sub>                                                                                                  |      | 0.5  |      | %Vol             |

| (11 077000)                       | Output low voltage                           |               | V <sub>IN</sub> = 2.7V, I <sub>OUT(PG)</sub> = 1mA                                                                            |      | 0.15 | 0.4  | V                |

|                                   | Leakage current                              |               | V <sub>(PG)</sub> = 5V                                                                                                        |      |      | 1    | μА               |

|                                   | Input current (EN)                           |               | EN = 0V                                                                                                                       | -1   | 0    | 1    |                  |

|                                   |                                              |               | EN = V <sub>IN</sub>                                                                                                          | -1   |      | 1    | μΑ               |

<sup>(1)</sup> Minimum  $V_{IN} = V_{OUT} + V_{DO}$  or 2.7V, whichever is greater. (2)  $V_{DO}$  is not measured for fixed output versions with  $V_{OUT(NOM)} < 2.8$  V because minimum  $V_{IN} = 2.7$ V.

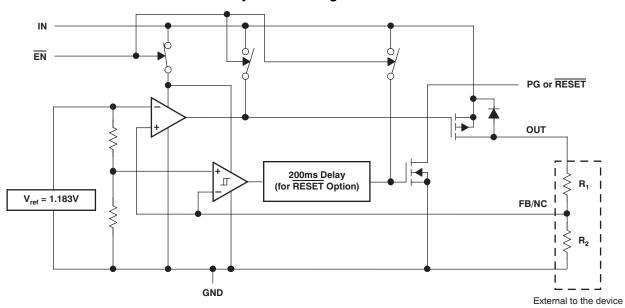

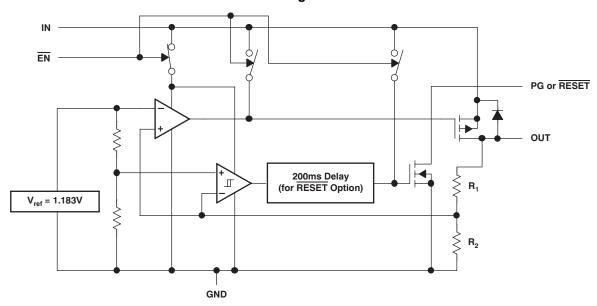

#### **FUNCTIONAL BLOCK DIAGRAMS**

#### **Adjustable Voltage Versions**

#### **Fixed Voltage Versions**

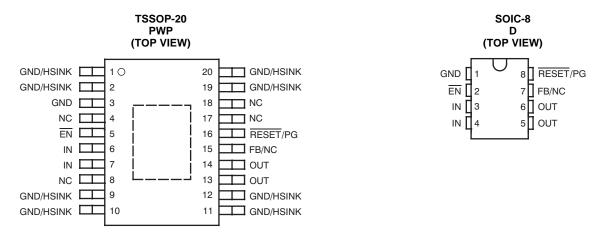

#### **PIN CONFIGURATIONS**

**Table 1. PIN DESCRIPTIONS**

| TPS     | S775xx, TPS77         | 6xx                                  |                                                                                                                                              |

|---------|-----------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | SOIC-8 (D)<br>PIN NO. | TSSOP-20<br>(PWP)<br>PIN NO.         | DESCRIPTION                                                                                                                                  |

| EN      | 2                     | 5                                    | Negative polarity enable (EN) input                                                                                                          |

| FB      | 7                     | 15                                   | Adjustable voltage version only; feedback voltage for setting output voltage of the device. Not internally connected on adjustable versions. |

| GND     | 1                     | 1, 2, 3, 9, 10,<br>11, 12, 19,<br>20 | Ground                                                                                                                                       |

| IN      | 3, 4                  | 6, 7                                 | Input voltage                                                                                                                                |

| OUT     | 5, 6                  | 13, 14                               | Regulated output voltage                                                                                                                     |

| RESET   | 8                     | 16                                   | TPS775xx devices only; open-drain RESET output.                                                                                              |

| PG      | 8                     | 16                                   | TPS776xx devices only; open-drain power-good (PG) output.                                                                                    |

| NC      | _                     | 4, 8, 17, 18                         | No internal connection                                                                                                                       |

| PAD/TAB | _                     | _                                    | Should be soldered to ground plane and used for heat sinking.                                                                                |

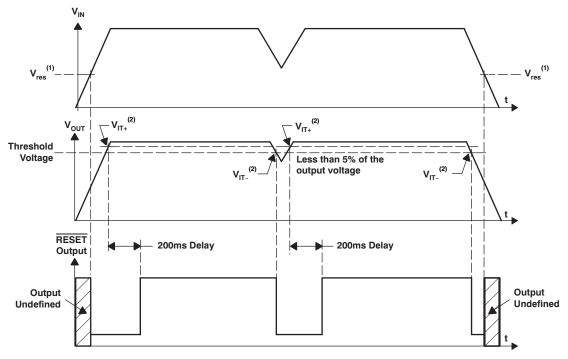

#### **TPS775xx RESET** Timing Diagram

- (1)  $V_{res}$  is the minimum input voltage for a valid  $\overline{RESET}$ . The symbol  $V_{res}$  is not currently listed within EIA or JEDEC standards for semiconductor symbology.

- (2)  $V_{IT}$ : Trip voltage is typically 5% lower than the output voltage (95%  $V_{OUT}$ ).  $V_{IT-}$  to  $V_{IT+}$  is the hysteresis voltage.

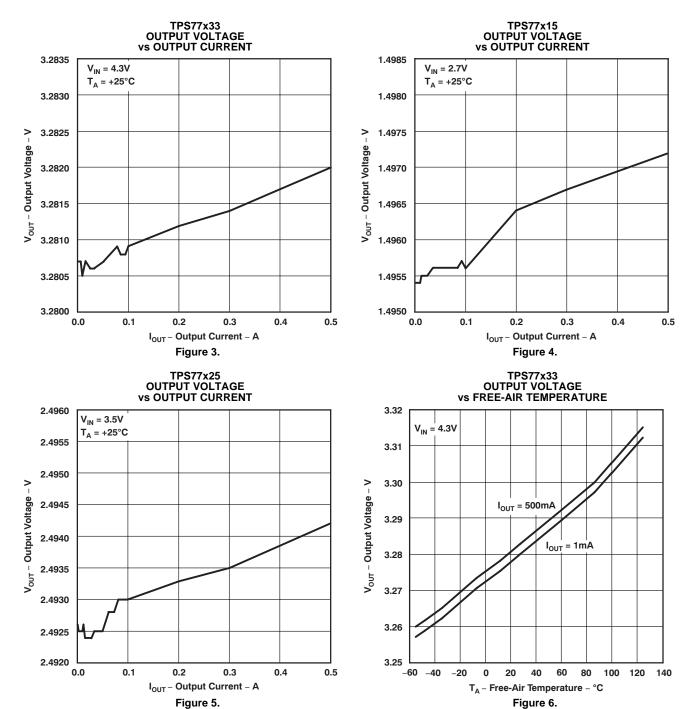

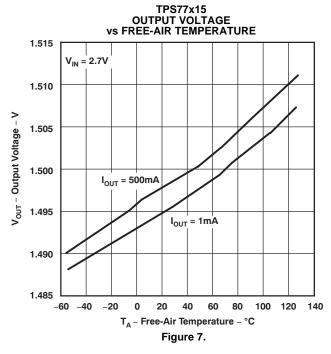

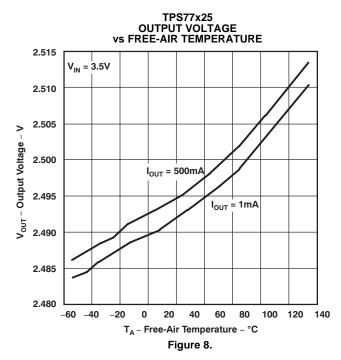

#### **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                  |                               |                         | FIGURE NO.                   |

|------------------|-------------------------------|-------------------------|------------------------------|

|                  |                               | vs Output Current       | Figure 3, Figure 4, Figure 5 |

| V <sub>OUT</sub> | Output Voltage                | vs Free-Air Temperature | Figure 6, Figure 7, Figure 8 |

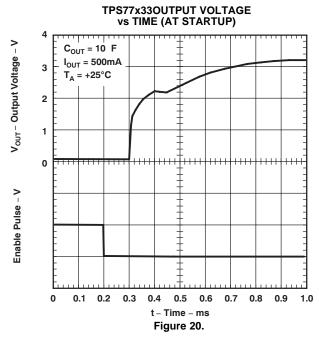

|                  |                               | vs Time                 | Figure 20                    |

| $I_{GND}$        | Ground Current                | vs Free-Air Temperature | Figure 9                     |

| PSRR             | Power-Supply Ripple Rejection | vs Frequency            | Figure 10                    |

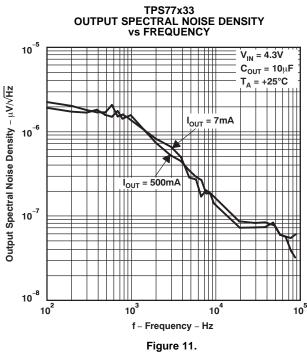

|                  | Output Spectral Noise Density | vs Frequency            | Figure 11                    |

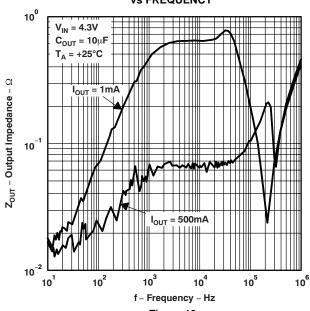

| Z <sub>OUT</sub> | Output Impedance              | vs Frequency            | Figure 12                    |

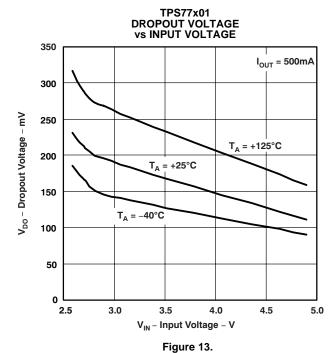

| V                | Dropout Voltage               | vs Input Voltage        | Figure 13                    |

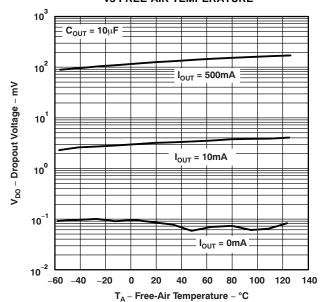

| $V_{DO}$         | Dropout voltage               | vs Free-Air Temperature | Figure 14                    |

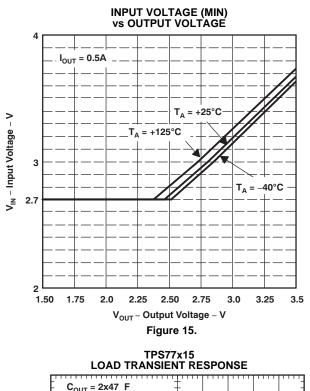

| V <sub>IN</sub>  | Input Voltage (Min)           | vs Output Voltage       | Figure 15                    |

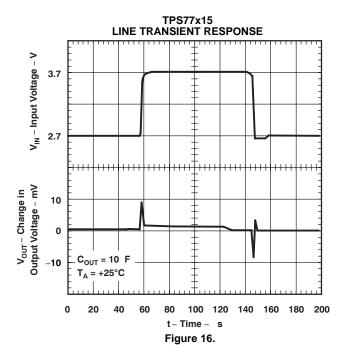

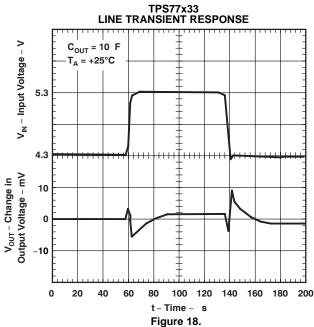

| LINE             | Line Transient Response       |                         | Figure 16, Figure 18         |

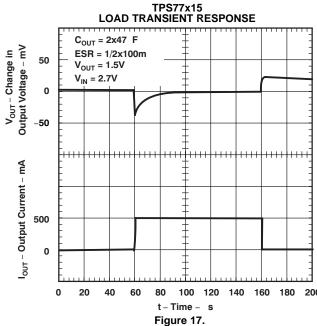

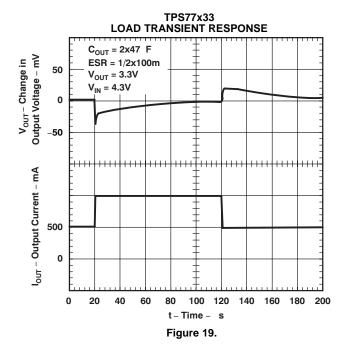

| LOAD             | Load Transient Response       |                         | Figure 17, Figure 19         |

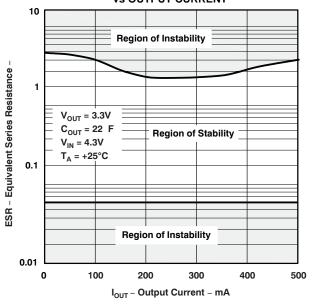

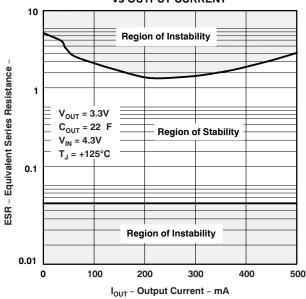

| ESR              | Equivalent Series Resistance  | vs Output Current       | Figure 22, Figure 23         |

#### TYPICAL CHARACTERISTICS

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

TPS77x33 OUTPUT IMPEDANCE vs FREQUENCY

Figure 12.

# TPS77x33 DROPOUT VOLTAGE vs FREE-AIR TEMPERATURE

Figure 14.

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

Over operating temperature range ( $T_J = -40$ °C to +125°C) unless otherwise noted. Typical values are at  $T_J = +25$ °C.

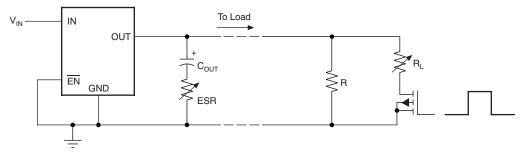

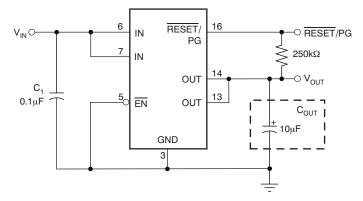

#### Test Circuit for Typical Regions of Stability (Figure 22 and Figure 23) (Fixed Output Options)

Figure 21.

# TYPICAL REGION OF STABILITY EQUIVALENT SERIES RESISTANCE<sup>(1)</sup> vs OUTPUT CURRENT

(1) Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>OUT</sub>. Figure 22.

# TYPICAL REGION OF STABILITY EQUIVALENT SERIES RESISTANCE<sup>(1)</sup> VS OUTPUT CURRENT

(1) Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>OUT</sub>. Figure 23.

#### **APPLICATION INFORMATION**

The TPS775xx and TPS776xx feature very low quiescent current, which remains virtually constant even with varying loads. Conventional LDO regulators use a pnp pass element, the base current of which is directly proportional to the load current through the regulator ( $I_B = I_C/\beta$ ). The TPS775xx and TPS776xx use a PMOS transistor to pass current; because the gate of the PMOS is voltage driven, operating current is low and invariable over the full load range.

Another pitfall associated with the pnp-pass element is its tendency to saturate when the device goes into dropout. The resulting drop in  $\beta$  forces an increase in  $I_B$  to maintain the load. During power up, this  $I_B$  increase translates to large start-up currents. Systems with limited supply current may fail to start up. In battery-powered systems, it means rapid battery discharge when the voltage decays below the minimum required for regulation. The TPS775xx and TPS776xx quiescent currents remain low even when the regulator drops out, eliminating both problems.

The TPS775xx and TPS776xx families also feature a shutdown mode that places the output in the high-impedance state (essentially equal to the feedback-divider resistance) and reduces quiescent current to  $2\mu$ A. If the shutdown feature is not used,  $\overline{\text{EN}}$  should be tied to ground.

#### **Minimum Load Requirements**

The TPS775xx and TPS776xx families are stable at zero load; no minimum load is required for operation.

#### FB—Pin Connection (Adjustable Version Only)

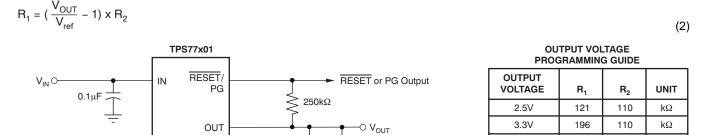

The FB pin is an input pin to sense the output voltage and close the loop for the adjustable option. The output voltage is sensed through a resistor divider network to close the loop as it is shown in Figure 25. Normally, this connection should be as short as possible; however, the connection can be made near a critical circuit to improve performance at that point. Internally, FB connects to a high-impedance wide-bandwidth amplifier and noise pickup feeds through to the regulator output. Routing the FB connection to minimize/avoid noise pickup is essential.

#### **External Capacitor Requirements**

An input capacitor is not usually required; however, a ceramic bypass capacitor ( $0.047\mu F$  or larger) improves load transient response and noise rejection if the TPS775xx or TPS776xx are located more than a few inches from the power supply. A higher-capacitance electrolytic capacitor may be necessary if large (hundreds of milliamps) load transients with fast rise times are anticipated.

Like all low dropout regulators, the TPS775xx and TPS776xx require an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitance value is  $10\mu F$  and the ESR (equivalent series resistance) must be between  $50m\Omega$  and  $1.5\Omega$ . Capacitor values  $10\mu F$  or larger are acceptable, provided the ESR is less than  $1.5\Omega$ . Solid tantalum electrolytic, aluminum electrolytic, and multilayer ceramic capacitors are all suitable, provided they meet the requirements described previously.

Figure 24. Typical Application Circuit (Fixed Versions)

#### Programming the TPS77x01 Adjustable LDO Regulator

The output voltage of the TPS77x01 adjustable regulator is programmed using an external resistor divider as shown in Figure 25. The output voltage is calculated using Equation 1:

$$V_{OUT} = V_{ref} \times (1 + \frac{R_1}{R_2})$$

(1)

#### Where:

•  $V_{ref} = 1.1834V$  typ (the internal reference voltage)

ΕN

FB/NC

Resistors  $R_1$  and  $R_2$  should be chosen for approximately  $10\mu A$  divider current. Lower value resistors can be used, but offer no inherent advantage and waste more power. Higher values should be avoided as leakage currents at FB increase the output voltage error. The recommended design procedure is to choose  $R_2 = 110k\Omega$  to set the divider current at approximately  $10\mu A$  and then calculate  $R_1$  using Equation 2:

Figure 25. TPS77x01 Adjustable LDO Regulator Programming

#### **Reset Indicator**

< 0.9V

The TPS775xx features a RESET output that can be used to monitor the status of the regulator. The internal comparator monitors the output voltage: when the output drops to between 92% and 98% of its nominal regulated value, the RESET output transistor turns on, taking the signal low. The open-drain output requires a pullup resistor. If not used, it can be left floating. RESET can be used to drive power-on reset circuitry or as a low-battery indicator. RESET does not assert itself when the regulated output voltage falls outside the specified 2% tolerance, but instead reports an output voltage low relative to its nominal regulated value (refer to Timing Diagram for start-up sequence).

#### **Power-Good Indicator**

The TPS776xx features a power-good (PG) output that can be used to monitor the status of the regulator. The internal comparator monitors the output voltage: when the output drops to between 92% and 98% of its nominal regulated value, the PG output transistor turns on, taking the signal low. The open-drain output requires a pullup resistor. If not used, it can be left floating. PG can be used to drive power-on reset circuitry or used as a low-battery indicator.

3.6V

4.75V

226

332

110

110

$k\Omega$

kΩ

www.ti.com

#### **Regulator Protection**

The TPS775xx and TPS776xx PMOS-pass transistors have a built-in back diode that conducts reverse currents when the input voltage drops below the output voltage (for example, during power down). Current is conducted from the output to the input and is not internally limited. When extended reverse voltage is anticipated, external limiting may be appropriate.

The TPS775xx and TPS776xx also feature internal current limiting and thermal protection. During normal operation, the TPS775xx and TPS776xx limit output current to approximately 1.7A. When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package. If the temperature of the device exceeds +150°C(typ), thermal-protection circuitry shuts it down. Once the device has cooled below +130°C(typ), regulator operation resumes.

#### **Power Dissipation and Junction Temperature**

Specified regulator operation is assured to a junction temperature of +125°C; the maximum junction temperature should be restricted to +125°C under normal operating conditions. This restriction limits the power dissipation the regulator can handle in any given application. To ensure the junction temperature is within acceptable limits, calculate the maximum allowable dissipation,  $P_{D(max)}$ , and the actual dissipation,  $P_D$ , which must be less than or equal to  $P_{D(max)}$ .

The maximum-power-dissipation limit is determined using the following equation:

$$P_{D(max)} = \frac{T_{J(max)} - T_{A}}{R_{\theta JA}}$$

#### where:

- T<sub>J(max)</sub> is the maximum allowable junction temperature

- R<sub>θJA</sub> is the thermal resistance junction-to-ambient for the package, and is calculated as

derating factor from the dissipation rating tables

- T<sub>A</sub> is the ambient temperature

The regulator dissipation is calculated using:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$$

Power dissipation resulting from quiescent current is negligible. Excessive power dissipation will trigger the thermal protection circuit.

www.ti.com

com 14-Oct-2022

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS77501D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77501                   | Samples |

| TPS77501DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77501                   | Samples |

| TPS77501PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77501                 | Samples |

| TPS77501PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77501                 | Samples |

| TPS77515D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77515                   | Samples |

| TPS77515DG4      | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77515                   | Samples |

| TPS77515DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77515                   | Samples |

| TPS77515PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77515                 | Samples |

| TPS77515PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77515                 | Samples |

| TPS77516D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 77516                   | Samples |

| TPS77516DG4      | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 77516                   | Samples |

| TPS77516DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 85    | 77516                   | Samples |

| TPS77516PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | PT77516                 | Samples |

| TPS77516PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | PT77516                 | Samples |

| TPS77518D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77518                   | Samples |

| TPS77518DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77518                   | Samples |

| TPS77518PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77518                 | Samples |

| TPS77518PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77518                 | Samples |

| TPS77525D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77525                   | Samples |

| TPS77525DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77525                   | Samples |

14-Oct-2022 www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS77525PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77525                 | Samples |

| TPS77533D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77533                   | Samples |

| TPS77533DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77533                   | Samples |

| TPS77533PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77533                 | Samples |

| TPS77533PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77533                 | Samples |

| TPS77601D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77601                   | Samples |

| TPS77601DG4      | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77601                   | Samples |

| TPS77601DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77601                   | Samples |

| TPS77601DRG4     | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77601                   | Samples |

| TPS77601PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77601                 | Samples |

| TPS77601PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77601                 | Samples |

| TPS77615D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77615                   | Samples |

| TPS77615DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77615                   | Samples |

| TPS77615PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77615                 | Samples |

| TPS77618D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77618                   | Samples |

| TPS77618DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77618                   | Samples |

| TPS77618PWP      | ACTIVE | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77618                 | Samples |

| TPS77618PWPR     | ACTIVE | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77618                 | Samples |

| TPS77625D        | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77625                   | Samples |

| TPS77625DG4      | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77625                   | Samples |

| TPS77625DR       | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77625                   | Samples |

www.ti.com 14-Oct-2022

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| TPS77625DRG4     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77625                | Samples |

| TPS77625PWP      | ACTIVE     | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77625              | Samples |

| TPS77625PWPR     | ACTIVE     | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77625              | Samples |

| TPS77628D        | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77628                | Samples |

| TPS77633D        | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77633                | Samples |

| TPS77633DG4      | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77633                | Samples |

| TPS77633DR       | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77633                | Samples |

| TPS77633DRG4     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM  | -40 to 125   | 77633                | Samples |

| TPS77633PWP      | ACTIVE     | HTSSOP       | PWP                | 20   | 70             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77633              | Samples |

| TPS77633PWPR     | ACTIVE     | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | PT77633              | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 14-Oct-2022

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS775, TPS776:

Automotive: TPS775-Q1, TPS776-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 13-May-2022

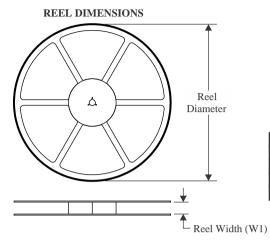

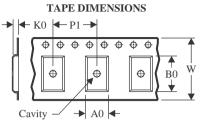

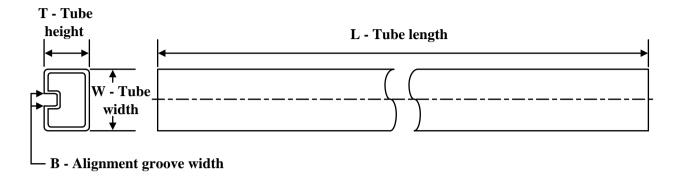

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

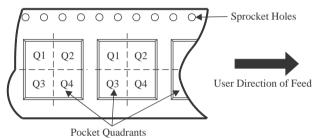

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS77501DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77501PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77515DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77515PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77516DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77516PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77518DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77518PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77525DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77533DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77533PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77601DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77601PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77615DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77618DR   | SOIC            | D                  | 8    | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77618PWPR | HTSSOP          | PWP                | 20   | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-May-2022

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS77625DR   | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77625PWPR | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS77633DR   | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS77633PWPR | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com 13-May-2022

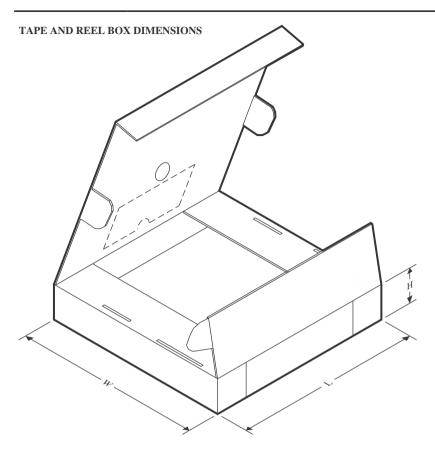

\*All dimensions are nominal

| Device       | Package Type        | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|---------------------|-----------------|------|------|-------------|------------|-------------|

| TPS77501DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77501PWPR | rps77501pwpr HTSSOp |                 | 20   | 2000 | 350.0 350.0 |            | 43.0        |

| TPS77515DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77515PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77516DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77516PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77518DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77518PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77525DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77533DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77533PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77601DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77601PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77615DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77618DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77618PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS77625DR   | SOIC                | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS77625PWPR | HTSSOP              | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 13-May-2022

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | TPS77633DR   | SOIC         | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| ĺ | TPS77633PWPR | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

www.ti.com 13-May-2022

#### **TUBE**

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS77501D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77501PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77515D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77515DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77515PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77516D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77516DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77516PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77518D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77518PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77525D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77525PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77533D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77533PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77601D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77601DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77601PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77615D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77615PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77618D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77618PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77625D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77625DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77625PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS77628D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77633D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77633DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS77633PWP | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

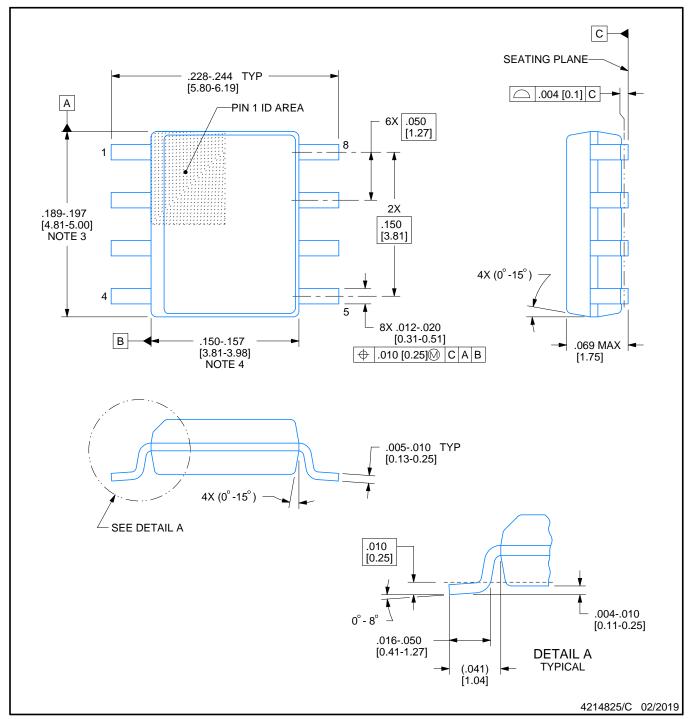

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

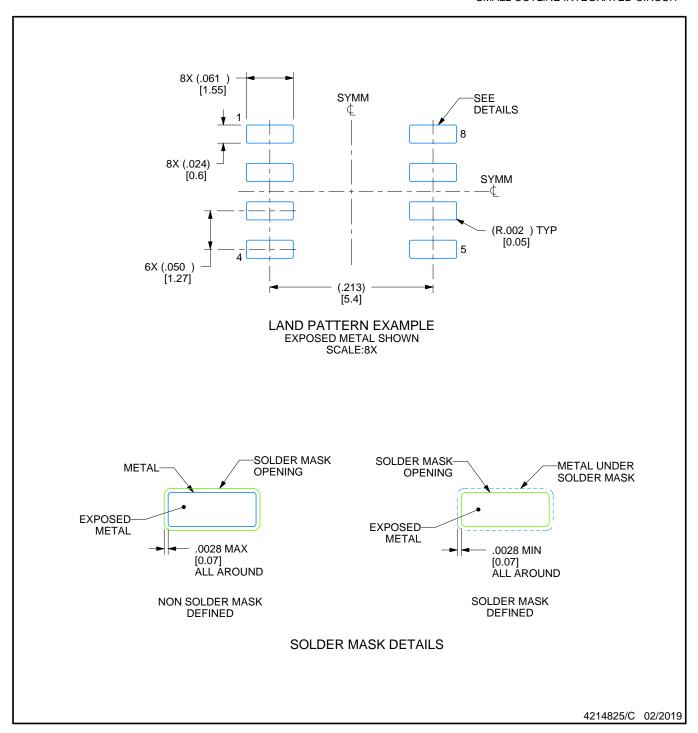

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

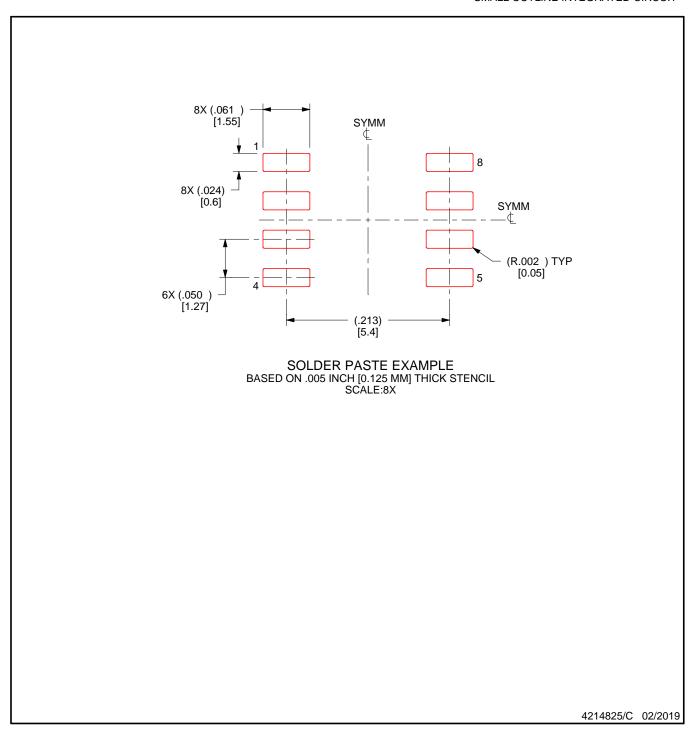

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

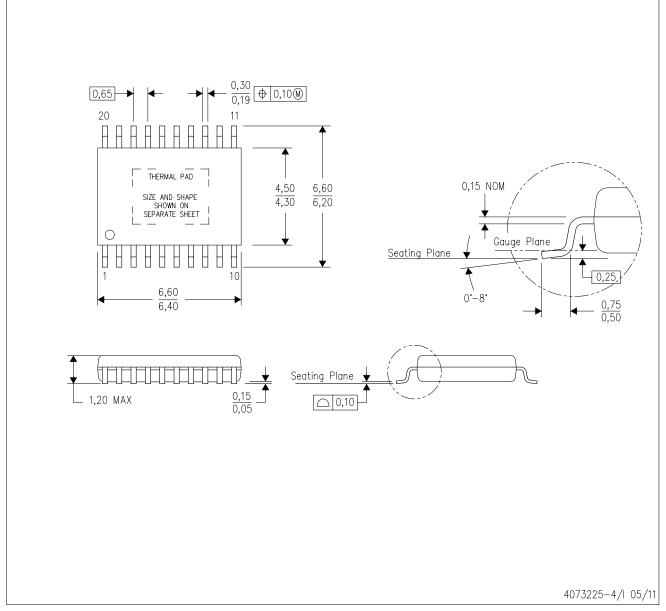

PWP (R-PDSO-G20)

### PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

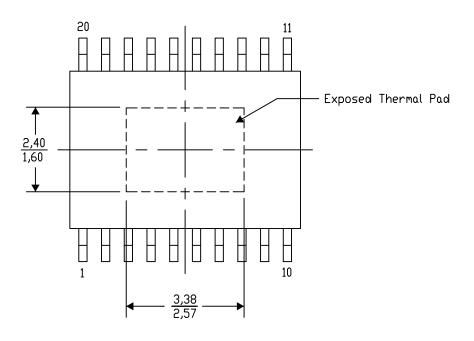

# PWP (R-PDSO-G20) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-13/AO 01/16

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

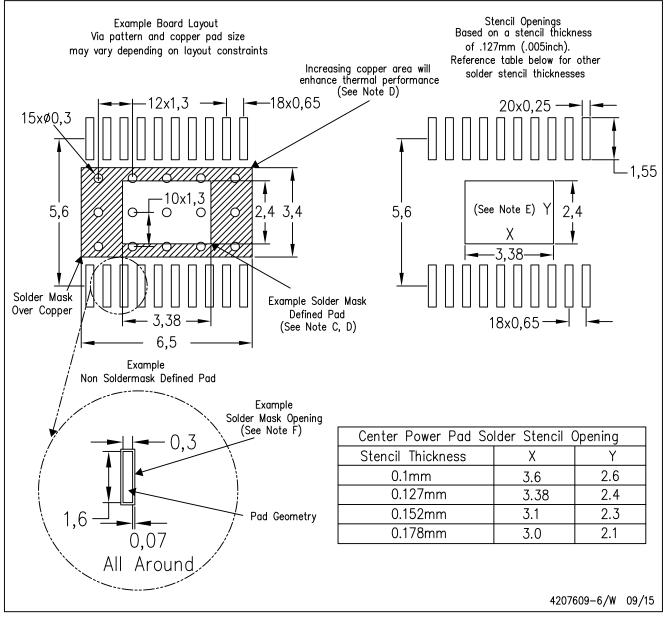

## PWP (R-PDSO-G20)

### PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

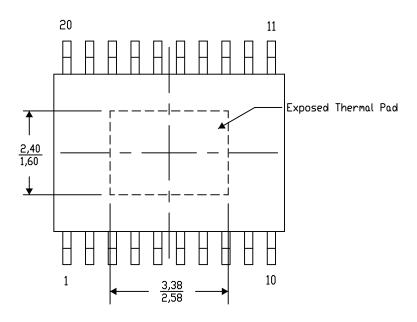

# PWP (R-PDSO-G20) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

Exposed Thermal Pad Dimensions

4206332-21/AO 01/16

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated