# DC to 65GHz Broadband MMIC Low-Noise Amplifier with PLFX

#### **Features**

- Integrated PLFX technology:

- Allows use of less-expensive coil

- Very low power dissipation:

- 4.5V, 85mA (383mW)

- High drain efficiency (38dBm/W)

- Great 0.04-50GHz performance:

- 10.5 ± 1.25dB gain

- 14.5dBm Psat, 11dBm P1dB

- 5dB noise figure

- >30dB dynamic gain control

- Integrated temperature-referenced power detector output

- 100% DC, RF, and visually tested

- Size: 1640x920um (64.6x36.2mil)

- ECCN 3A001.b.2.d

# **Description**

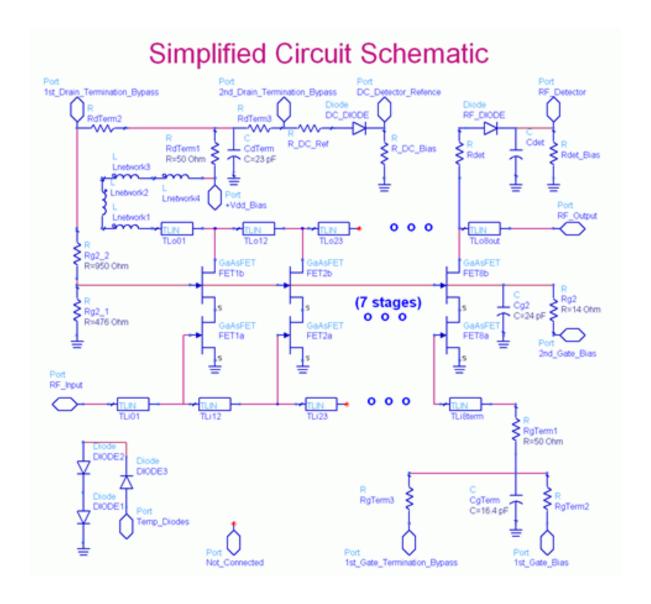

The MMA036AA is a seven stage traveling wave amplifier. The amplifier features Microsemi PLFX (Passive Low Frequency eXtension) circuitry designed to reduce the integration cost of the amplifier. PLFX isolates the amplifier from bias inductor resonances, allowing use of a less-expensive coil.

# **Application**

The MMA036AA Broadband MMIC Low-Noise Amplifier with PLFX is designed for high efficiency and low-noise broadband applications in RF and microwave communications, test equipment and military systems. By using specific external components, the bandwidth of operation can be extended below 40MHz.

**Key Characteristics:** Vdd=4.5V, Idd=85mA, Zo=50 $\Omega$  Specifications pertain to wafer measurements with RF probes and DC bias cards @ 25°C

|                           |                             | 1.5 - 40GHz |      | 0.04 - 50GHz |     |      | 0.04 - 65GHz |     |     |     |

|---------------------------|-----------------------------|-------------|------|--------------|-----|------|--------------|-----|-----|-----|

| Parameter                 | Description                 | Min         | Тур  | Max          | Min | Тур  | Max          | Min | Тур | Max |

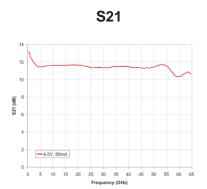

| S21 (dB)                  | Small Signal Gain           | 9.5         | 11   | -            | 9.5 | 10.5 | -            | 8   | 10  | -   |

| Flatness (±dB)            | Gain Flatness               | -           | 0.5  | 1.25         | -   | 1.25 | 1.75         | -   | 1.5 | 2.0 |

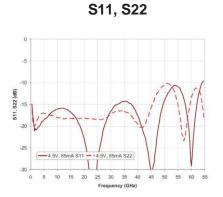

| S11 (dB)                  | Input Match                 | -           | -15  | -12          | -   | -15  | -12          | -   | -11 | -9  |

| S22 (dB)                  | Output Match                | -           | -15  | -12          | -   | -12  | -10          | -   | -12 | -9  |

| S12 (dB)                  | Reverse Isolation           | -           | -20  | -17          | -   | -18  | -15          | -   | -16 | -13 |

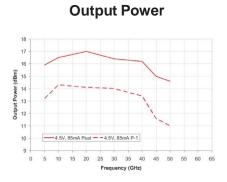

| P1dB (dBm)                | 1dB Compressed Output Power | 11.5        | 13   | -            | 9.5 | 11   | -            | -   | -   | -   |

| Psat (dBm)                | Saturated Output Power      | 14          | 15.5 | -            | -   | 14.5 | -            | -   | -   | -   |

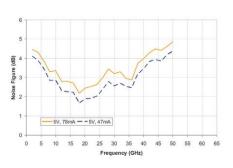

| NF (dB)                   | Noise Figure                | -           | 4.5  | -            | -   | 5    | -            | -   | -   | -   |

| RF <sub>det</sub> (mV/mW) | RF Detector Sensitivity     | -           | 0.5  | -            | -   | 0.5  | -            | -   | -   | -   |

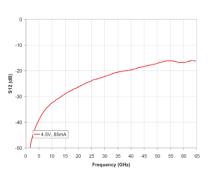

# **Typical Performance**

Typical IC performance measured on-wafer

Typical IC performance measured on-wafer

Typical IC performance measured on-wafer

# **Noise Frequency**

Typical IC performance with package de-embedded

Typical IC performance measured on-wafer

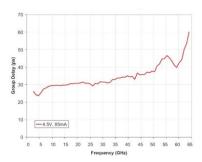

# **Group Delay**

Typical IC performance measured on-wafer

**Table 1: Supplemental Specifications**

| Parameter       | Description                                  | Min            | Тур     | Max   |

|-----------------|----------------------------------------------|----------------|---------|-------|

| Vdd             | Drain Bias Voltage                           | 3V             | 4.5V    | 7.5V  |

| ldd             | Drain Bias Current                           | -              | 85mA    | 120mA |

| Vg1             | 1st Gate Bias Voltage                        | -4V            | -       | +0.5V |

| Vg2             | 2nd Gate Bias Voltage                        | Vdd - Vg2 < 7V | N/C     | +4V   |

| $P_{in}$        | Input Power (CW)                             | -              | -       | 20dBm |

| P <sub>dc</sub> | Power Dissipation                            | -              | 0.383W  | -     |

| T <sub>ch</sub> | Channel Temperature                          | -              | -       | 150°C |

| $\Theta_{ch}$   | Thermal Resistance (T <sub>case</sub> =85°C) | -              | 22° C/W | -     |

#### DC Bias:

The MMA036AA features a patented on-chip passive bias circuit called 'PLFX'. This circuit isolates the amplifier from bias coil resonances above 14GHz, allowing the use of less expensive coils; traditional biasing requires bias coils with self-resonances outside the operating range of the amplifier.

The device is biased by applying a positive voltage to the drain (Vdd), then setting the drain current (Idd) using a negative voltage on the gate (Vg1). The nominal bias is Vdd=4.5V, Idd=85mA.

Improved performance can be achieved with gate bias adjustment; use the drain termination bypass to alter the output voltage (detected at drain voltage sense).

#### **Gain Control:**

Dynamic gain control is available when operating the amplifier in the linear gain region. Negative voltage applied to the second gate (Vg2) reduces amplifier gain.

#### **RF Power Detection:**

RF output power can be calculated from the difference between the RF detector voltage and the DC detector voltage, minus a DC offset. Please consult the application note available on the Microsemi website.

# **Low-Frequency Use:**

The MMA036AA has been designed so that the bandwidth can be extended to low frequencies. The low end corner frequency of the device is primarily determined by the external biasing and AC coupling circuitry.

# Matching:

The amplifier incorporates on- chip termination resistors on the RF input and output. These resistors are RF grounded through on-chip capacitors, which are small and become open circuits at frequencies below 1GHz.

A pair of gate and drain termination bypass pads are provided for connecting external capacitors required for the low frequency extension network. These capacitors should be 10x the value of the DC blocking capacitors.

#### DC Blocks:

The amplifier is DC coupled to the RF input and output pads; DC voltage on these pads must be isolated from external circuitry.

For operation above 2GHz, a series DC-blocking capacitor with minimum value of 20pF is recommended; operation above 40MHz requires a minimum of 120pF.

#### **Bias Inductor:**

DC bias applied to the drain (Vdd) must be decoupled with an off-chip RF choke inductor. The amount of bias inductance will determine the low frequency operating point. Inductive biasing can also be applied to the chip through the RF output.

For many applications above 2GHz, a bondwire from the Vdd pad will suffice as the biasing inductor. Ensure the correct bond length as shown in the assembly diagrams.

Simplified Circuit Schematic

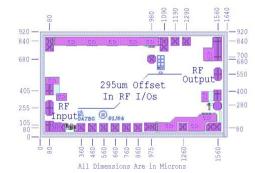

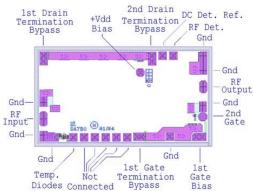

#### Die size, pad locations, and pad descriptions

Chip size: 1640x920um (64.6x36.2ml) Chip size tolerance:  $\pm 5um$  (0.2mil) Chip thickness:  $100 \pm 10um$  ( $4 \pm 0.4mil$ ) Pad dimensions: 80x80um (3.1x3.1mil)

# **Pick-up and Chip Handling:**

This MMIC has exposed air bridges on the top surface. **Do not pick up chip with vacuum on the die center**; handle from edges or with a custom collet.

# **Thermal Heat Sinking:**

To avoid damage and for optimum performance, you must observe the maximum channel temperature and ensure adequate heat sinking.

#### **ESD Handling and Bonding:**

**This MMIC** is **ESD** sensitive; preventive measures should be taken during handling, die attach, and bonding.

**Epoxy die attach is recommended.** Please review our application note MM-APP-0001 handling and die attach recommendations, on our website for more handling, die attach and bonding information.

Information contained in this document is proprietary to Microsem. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.