## 3 V to 5 V Single Supply, 200 kSPS 8-Channel, 12-Bit Sampling ADCs

## AD7859/AD7859L

#### **FEATURES**

Specified for V<sub>DD</sub> of 3 V to 5.5 V AD7859-200 kSPS; AD7859L-100 kSPS System and Self-Calibration

Low Power

**Normal Operation**

AD7859: 15 mW ( $V_{DD} = 3 \text{ V}$ ) AD7859L: 5.5 mW ( $V_{DD} = 3 \text{ V}$ )

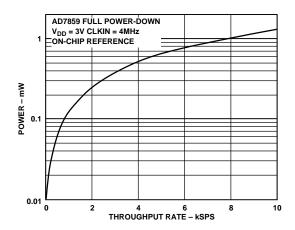

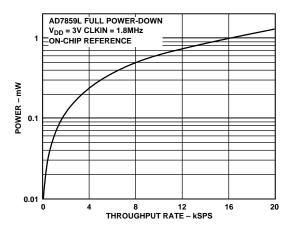

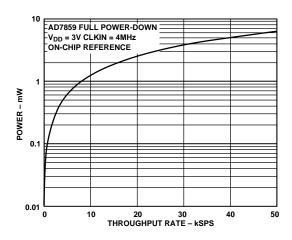

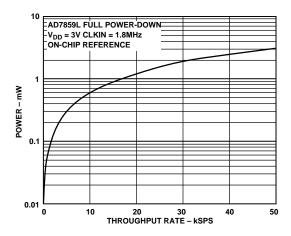

Using Automatic Power-Down After Conversion (25  $\mu$ W)

AD7859: 1.3 mW ( $V_{DD}$  = 3 V 10 kSPS) AD7859L: 650  $\mu$ W ( $V_{DD}$  = 3 V 10 kSPS)

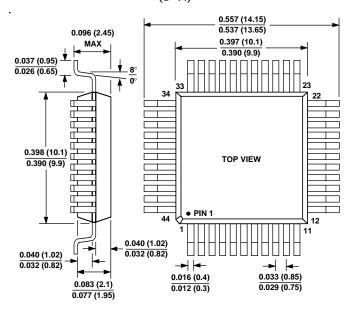

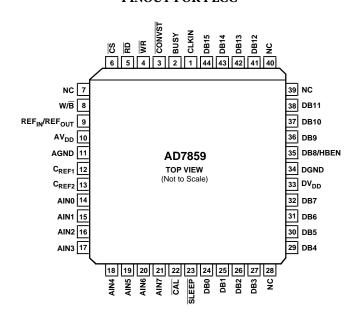

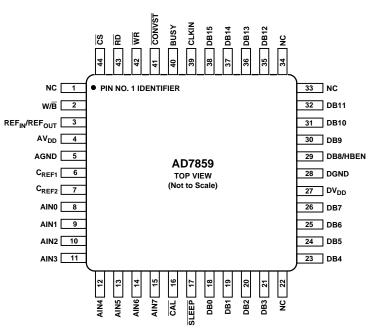

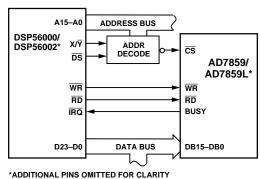

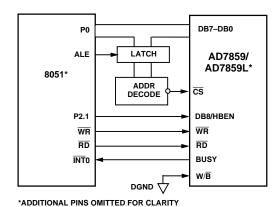

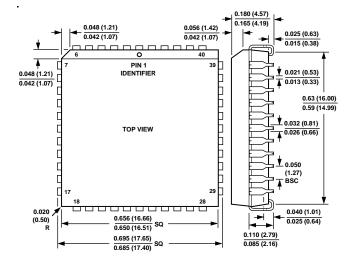

Flexible Parallel Interface: 16-Bit Parallel/8-Bit Parallel 44-Pin PQFP and PLCC Packages

#### **APPLICATIONS**

Battery-Powered Systems (Personal Digital Assistants, Medical Instruments, Mobile Communications) Pen Computers Instrumentation and Control Systems High Speed Modems

#### **GENERAL DESCRIPTION**

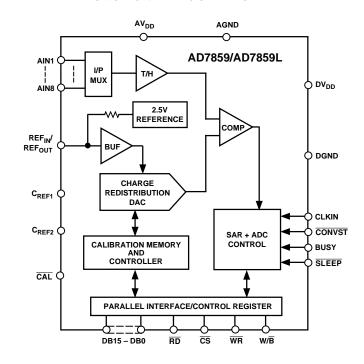

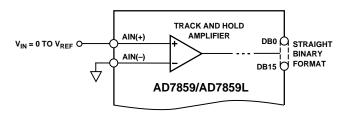

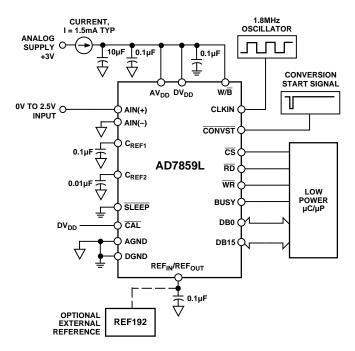

The AD7859/AD7859L are high speed, low power, 8-channel, 12-bit ADCs which operate from a single 3 V or 5 V power supply, the AD7859 being optimized for speed and the AD7859L for low power. The ADC contains self-calibration and system calibration options to ensure accurate operation over time and temperature and have a number of power-down options for low power applications.

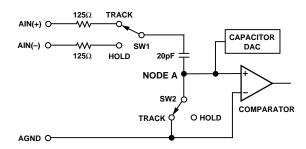

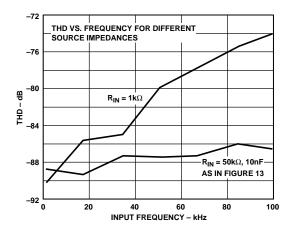

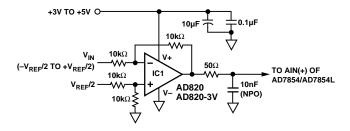

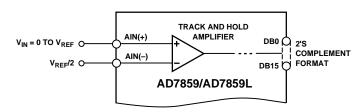

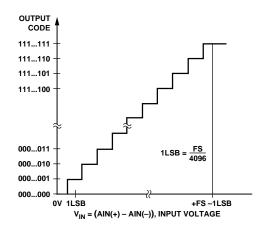

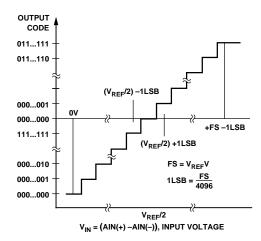

The AD7859 is capable of 200 kHz throughput rate while the AD7859L is capable of 100 kHz throughput rate. The input track-and-hold acquires a signal in 500 ns and features a pseudo-differential sampling scheme. The AD7859 and AD7859L input voltage range is 0 to  $V_{REF}$  (unipolar) and  $-V_{REF}/2$  to  $+V_{REF}/2$  about  $V_{REF}/2$  (bipolar) with both straight binary and 2s complement output coding respectively. Input signal range is to the supply and the part is capable of converting full-power signals to 100 kHz.

CMOS construction ensures low power dissipation of typically 5.4 mW for normal operation and 3.6  $\mu$ W in power-down mode. The part is available in 44-pin, plastic quad flatpack package (PQFP) and plastic lead chip carrier (PLCC).

See page 28 for data sheet index.

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- 1. Operation with either 3 V or 5 V power supplies.

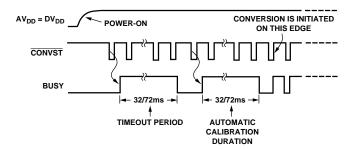

- 2. Flexible power management options including automatic power-down after conversion.

- 3. By using the power management options a superior power performance at slower throughput rates can be achieved. AD7859: 1 mW typ @ 10 kSPS AD7859L: 1 mW typ @ 20 kSPS

- 4. Operates with reference voltages from 1.2 V to the supply.

- 5. Analog input ranges from 0 V to V<sub>DD</sub>.

- 6. Self and system calibration.

- 7. Versatile parallel I/O port.

- 8. Lower power version AD7859L.

#### REV. A

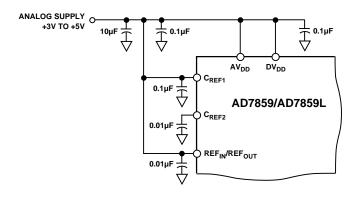

$\begin{array}{l} \textbf{AD7859/AD7859L-SPECIFICATIONS}^{1,\;2} \\ \textbf{External Reference,} \; f_{\text{CLKIN}} = 4 \; \text{MHz} \; (\text{for L Version: } 1.8 \; \text{MHz} \; (0^{\circ}\text{C to } +70^{\circ}\text{C}) \; \text{and } 1 \; \text{MHz} \; (-40^{\circ}\text{C to } +85^{\circ}\text{C})); \; f_{\text{SAMPLE}} = 200 \; \text{kHz} \; (\text{AD7859}) \; 100 \; \text{kHz} \\ \textbf{AD70501} \; \text{CLRIP Constitutions} \;$ (AD7859L);  $\overline{\text{SLEEP}} = \text{Logic High}$ ;  $T_A = T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.) Specifications in () apply to the AD7859L.

| Parameter                                                    | A Version <sup>1</sup> | B Version <sup>1</sup>          | Units      | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------|------------------------|---------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                          |                        |                                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

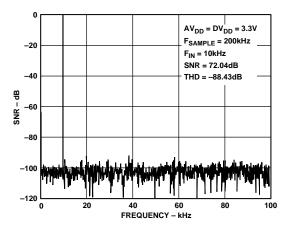

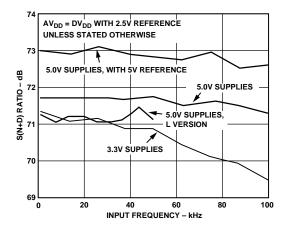

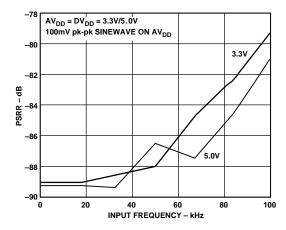

| Signal to Noise + Distortion Ratio <sup>3</sup>              | 70                     | 71                              | dB min     | Typically SNR is 72 dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (SNR)                                                        |                        |                                 |            | $V_{IN} = 10 \text{ kHz Sine Wave, } f_{SAMPLE} = 200 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                              |                        |                                 |            | (for L Version: $f_{SAMPLE} = 100 \text{ kHz}$ @ $f_{CLKIN} = 2 \text{ MHz}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Total Harmonic Distortion (THD)                              | -78                    | -78                             | dB max     | $V_{IN} = 10 \text{ kHz Sine Wave, } f_{SAMPLE} = 200 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ,                                                            |                        |                                 |            | (for L Version: $f_{SAMPLE} = 100 \text{ kHz}$ @ $f_{CLKIN} = 2 \text{ MHz}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Peak Harmonic or Spurious Noise                              | -78                    | -78                             | dB max     | $V_{IN} = 10 \text{ kHz Sine Wave, } f_{SAMPLE} = 200 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| •                                                            |                        |                                 |            | (for L Version: f <sub>SAMPLE</sub> = 100 kHz @ f <sub>CLKIN</sub> = 2 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Intermodulation Distortion (IMD)                             |                        |                                 |            | CHAILE CHAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Second Order Terms                                           | -78                    | -78                             | dB typ     | $fa = 9.983 \text{ kHz}, fb = 10.05 \text{ kHz}, f_{SAMPLE} = 200 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              |                        |                                 |            | (for L Version: $f_{SAMPLE} = 100 \text{ kHz}$ @ $f_{CLKIN} = 2 \text{ MHz}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Third Order Terms                                            | -78                    | -78                             | dB typ     | $fa = 9.983 \text{ kHz}, fb = 10.05 \text{ kHz}, f_{SAMPLE} = 200 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              |                        |                                 |            | (for L Version: f <sub>SAMPLE</sub> = 100 kHz @ f <sub>CLKIN</sub> = 2 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel-to-Channel Isolation                                 | -80                    | -80                             | dB typ     | $V_{IN} = 25 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D.C. L.C.CVID.L.CVI                                          |                        |                                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DC ACCURACY                                                  | 1                      |                                 | n.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Resolution                                                   | 12                     | 12                              | Bits       | SUD C V - SV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Integral Nonlinearity                                        | ±1                     | ±0.5                            | LSB max    | 5 V Reference $V_{DD} = 5 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Nonlinearity                                    | ±1                     | ±1                              | LSB max    | Guaranteed No Missed Codes to 12 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Unipolar Offset Error                                        | ±5                     | ±5                              | LSB max    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| H: 1 Off F M: 1                                              | ±2                     | ±2                              | LSB typ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unipolar Offset Error Match                                  | 2(3)                   | 2                               | LSB max    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Positive Full-Scale Error                                    | ±5                     | ±5                              | LSB max    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| N . F 11.0 1 F                                               | ±2                     | ±2                              | LSB typ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Negative Full-Scale Error                                    | ±2                     | ±2                              | LSB max    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Full-Scale Error Match                                       | 1                      | 1                               | LSB max    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bipolar Zero Error                                           | ±1                     | ±1                              | LSB typ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bipolar Zero Error Match                                     | 2                      | 2                               | LSB typ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ANALOG INPUT                                                 |                        |                                 |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Voltage Ranges                                         | 0 to V <sub>REF</sub>  | 0 to V <sub>REF</sub>           | Volts      | i.e., $AIN(+) - AIN(-) = 0$ to $V_{REF}$ , $AIN(-)$ Can Be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                              |                        |                                 |            | Biased Up But AIN(+) Cannot Go Below AIN(-)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                              | $\pm V_{REF}/2$        | $\pm V_{REF}/2$                 | Volts      | i.e., $AIN(+) - AIN(-) = -V_{REF}/2$ to $+V_{REF}/2$ , $AIN(-)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

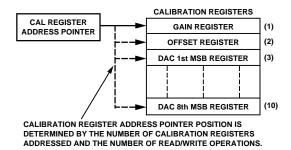

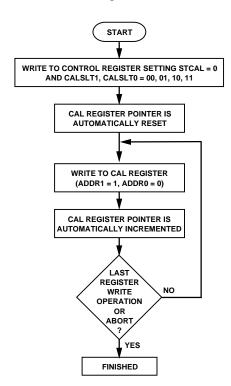

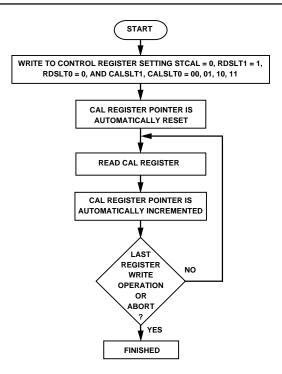

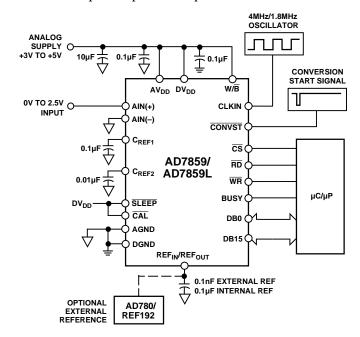

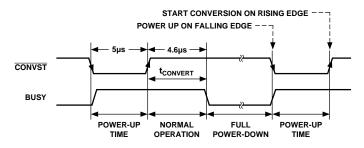

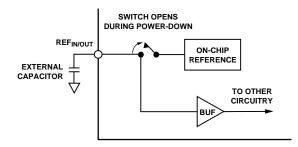

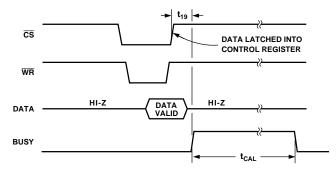

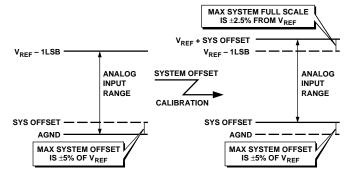

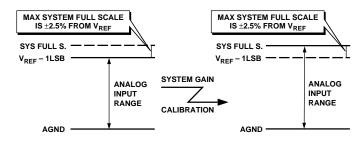

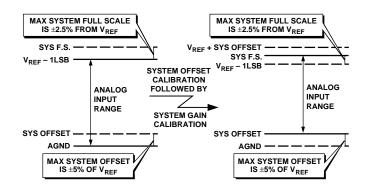

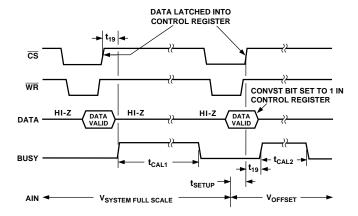

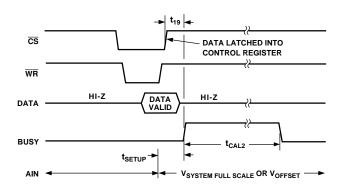

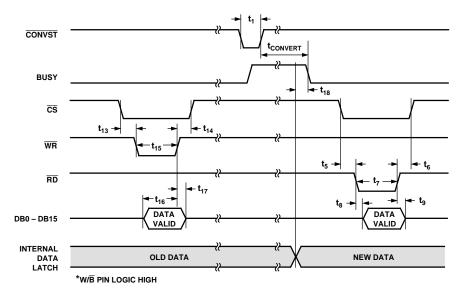

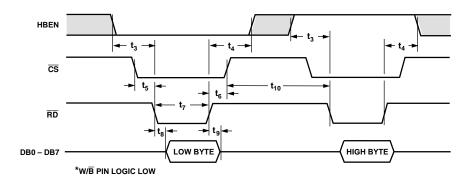

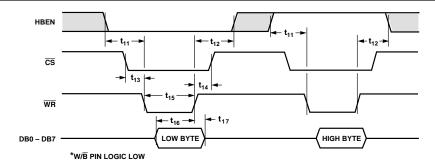

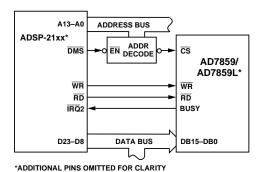

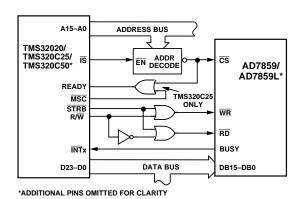

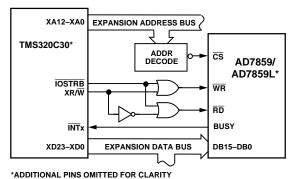

|                                                              |                        |                                 |            | Should Be Biased to +V <sub>REF</sub> /2 and AIN(+) Can Go                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |