# <u>LDO Regulator</u> - Dual, Camera Modules, Low Iq, Very Low Dropout, Ultra Low Noise

## 500 mA, 250 mA

The NCP156 is Dual Output Linear Voltage Regulator optimized for camera module application. The device offers unique combination of High Current Low Voltage Bias Rail Topology for supplying digital block and very precise second output for powering analog sensor block. This combination allows achieving the best performance and power efficiency.

## **Features**

- High Current Bias Rail Topology for OUT1

- High PSRR, Ultra Low Noise LDO for OUT2

- Output voltage range: OUT1 0.8 V to 1.8 V (Factory trimmed) OUT2 – 1.8 V to 3.6 V

- Low I<sub>O</sub> of typ. 90 μA

- Slow V<sub>OUT</sub> Slew Rate for Camera Modules (Optional) typ. ≤30 mV/ms

- Ultra–Low Dropout: OUT1 typ. 70 mV @ 1.2 V/500 mA

OUT2 typ. 95 mV @ 2.8 V/250 mA

- ±1% Typical Accuracy

- High PSRR: OUT1 typ. 70 dB at 1 kHz OUT2 typ. 92 dB at 1 kHz

- Thermal Shutdown and Current Limit Protections

- Stable with a Small Ceramic Capacitor

- Available WLCSP-6 1.2x0.8 mm Package

- Active Output Discharge for Fast Output Turn-Off

- These are Pb-free Devices

## **Typical Applications**

- Camera Modules

- Smartphones, Tablets

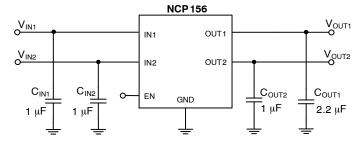

Figure 1. Typical Application Schematic

## ON Semiconductor™

www.onsemi.com

MARKING DIAGRAM

WLCSP6, 1.2x0.8 CASE 567MV

XX = Specific Device Code

M = Month Code

= Pb-Free Package

## **PIN CONNECTIONS**

## (Top View)

## **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 8 of this data sheet.

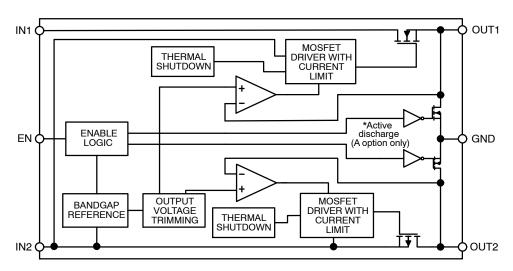

Figure 2. Simplified Schematic Block Diagram

## **Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Description                                                                                              |

|---------|----------|----------------------------------------------------------------------------------------------------------|

| A1      | IN1      | Output 1 – Power Supply pin                                                                              |

| A2      | OUT1     | Regulated Output 1 Voltage pin                                                                           |

| B1      | EN       | Applying $V_{EN}$ < 0.4 V disables the regulator; Pulling $V_{EN}$ > 0.9 V enables both voltage outputs. |

| B2      | GND      | Common ground connection                                                                                 |

| C1      | IN2      | Output 2 – Power Supply pin, Output 1 – Control Supply pin                                               |

| C2      | OUT2     | Regulated Output 2 Voltage pin                                                                           |

## Table 2. THERMAL CHARACTERISTICS (Note 1)

| Rating                                     | Symbol            | Value | Unit |

|--------------------------------------------|-------------------|-------|------|

| Thermal Characteristics, WLCSP6 1.2x0.8mm, |                   |       | °C/W |

| Thermal Resistance, Junction-to-Air        | $\theta_{\sf JA}$ | 90    |      |

<sup>1.</sup> Single component mounted on 1 oz, FR4 PCB with 645mm2 Cu area

## **Table 3. ABSOLUTE MAXIMUM RATINGS**

| Rating                                        | Symbol             | Value                          | Unit |

|-----------------------------------------------|--------------------|--------------------------------|------|

| Input Voltage 1 (Note 2)                      | V <sub>IN1</sub>   | -0.3 to 6                      | V    |

| Input Voltage 2 (Note 2)                      | $V_{IN2}$          | -0.3 to 6                      | V    |

| Output Voltage 1                              | V <sub>OUT1</sub>  | -0.3 to V <sub>IN1</sub> + 0.3 | V    |

| Output Voltage 2                              | V <sub>OUT2</sub>  | $-0.3$ to $V_{IN2} + 0.3$      | V    |

| Enable Input                                  | $V_{EN}$           | -0.3 to 6                      | V    |

| Output Short Circuit Duration                 | t <sub>SC</sub>    | Indefinite                     | S    |

| Maximum Junction Temperature                  | $T_{J(MAX)}$       | 150                            | °C   |

| Storage Temperature                           | T <sub>STG</sub>   | -55 to 125                     | °C   |

| ESD Capability, Human Body Model (Note 3)     | ESD <sub>HBM</sub> | 2000                           | V    |

| ESD Capability, Machine Model (Note 3)        | ESD <sub>MM</sub>  | 200                            | V    |

| ESD Capability, Charged Device Model (Note 3) | ESD <sub>CDM</sub> | 1000                           | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 2. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 3. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- ESD Charged Device Model tested per EIA/JESD22-C101, Field Induced Charge Model

- Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

Table 4. ELECTRICAL CHARACTERISTICS  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ ;  $V_{IN1} = V_{OUT1(NOM)} + 0.3$  V,  $V_{IN2} = 2.7$  V or  $(V_{OUT1} + 1.6$  V) or  $V_{OUT2(NOM)} + 0.3$  V whichever is greater,  $I_{OUT1} = I_{OUT2} = 1$  mA,  $V_{EN} = 1$  V, unless otherwise noted.  $C_{IN1} = C_{IN2} = 1$  μF,  $C_{OUT1} = 2.2$  μF,  $C_{OUT2} = 1$  μF. Typical values are at  $T_{J} = +25^{\circ}C$ . Min/Max values are for  $-40^{\circ}C \le T_{J} \le 125^{\circ}C$  unless otherwise noted.

| Parameter                                             | Test Conditions                                                                                                        |                                                                 | Symbol                                                      | Min                   | Тур                                                                                                                                                                 | Max  | Unit |     |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|

| Operating Input Voltage<br>Range                      |                                                                                                                        |                                                                 |                                                             | V <sub>IN1</sub>      | V <sub>OUT1</sub> + V <sub>DO</sub>                                                                                                                                 |      | 5.5  | V   |

|                                                       |                                                                                                                        |                                                                 |                                                             | V <sub>IN2</sub>      | $\begin{aligned} &V_{IN2} = \\ &(V_{OUT1} + 1.\\ &5) \geq 2.4 \text{ or } \\ &V_{OUT2(NO}\\ &M) + V_{DO}, \\ &\text{whichever} \\ &\text{is greater} \end{aligned}$ |      | 5.5  |     |

| Output Voltage Accuracy                               | $T_J = 25^{\circ}C$                                                                                                    |                                                                 |                                                             | V <sub>OUT1</sub>     |                                                                                                                                                                     | ±1   |      | %   |

|                                                       |                                                                                                                        |                                                                 |                                                             | $V_{OUT2}$            |                                                                                                                                                                     |      |      |     |

| Undervoltage Lock-out                                 | V <sub>IN2</sub> Risin                                                                                                 | g                                                               |                                                             | UVLO                  |                                                                                                                                                                     | 1.5  |      | V   |

|                                                       | Hysteresia                                                                                                             | 3                                                               |                                                             |                       |                                                                                                                                                                     | 0.2  |      |     |

| Output Voltage Accuracy                               | $V_{OUT1(NO)} \le V_{OUT1(NO)} \le V_{OUT2} = 2$                                                                       | IOM) + 1.0 V,                                                   | V <sub>OUT1</sub> < 1.2 V                                   | V <sub>OUT1</sub>     | -18                                                                                                                                                                 |      | +18  | mV  |

|                                                       | (V <sub>OUT1(N0</sub><br>whichever<br>< I <sub>OUT1</sub> <                                                            | r is greater, 1 mA                                              | V <sub>OUT1</sub> ≥ 1.2 V                                   |                       | -1.5                                                                                                                                                                |      | +1.5 | %   |

|                                                       | $V_{IN2} = (V_{OUT2(NOM)} + 0.3 \text{ V}) \text{ to } 5.5 \text{ V}, \\ 0 \text{ mA} \le I_{OUT2} \le 250 \text{ mA}$ |                                                                 | V <sub>OUT2</sub>                                           | -2                    |                                                                                                                                                                     | +2   | %    |     |

| Line Regulation                                       | V <sub>OUT1</sub>                                                                                                      | V <sub>OUT1(NOM)</sub> + 0.3 \                                  | $V \le V_{IN1} \le 5.5 \text{ V}$                           | Line <sub>REG</sub>   |                                                                                                                                                                     | 0.01 |      | %/V |

|                                                       | V <sub>OUT2</sub>                                                                                                      | V <sub>OUT2(NOM)</sub> + 0.3 \                                  | V ≤ V <sub>IN2</sub> ≤ 5.5 V                                |                       |                                                                                                                                                                     | 0.02 |      |     |

|                                                       | V <sub>IN2</sub> to<br>V <sub>OUT1</sub>                                                                               | (2.7 V or (V <sub>OUT1(N0</sub> ever is greater) < \footnote{N} | <sub>OM)</sub> + 1.6 V), which-<br>V <sub>IN2</sub> < 5.5 V |                       |                                                                                                                                                                     | 0.01 |      |     |

| Load Regulation                                       | OUT1                                                                                                                   | I <sub>OUT1</sub> = 1 mA to 50                                  | 0 mA                                                        | Load <sub>REG</sub>   |                                                                                                                                                                     | 5    |      | mV  |

|                                                       | OUT2                                                                                                                   | I <sub>OUT2</sub> = 1 mA to 25                                  | 0 mA                                                        |                       |                                                                                                                                                                     | 1    |      |     |

| Dropout Voltage                                       | OUT1                                                                                                                   | I <sub>OUT1</sub> = 500 mA                                      |                                                             | $V_{DO}$              |                                                                                                                                                                     | 70   | 150  | mV  |

| (Note 5)                                              | OUT2                                                                                                                   | I <sub>OUT2</sub> = 250 mA                                      | V <sub>OUT2(NOM)</sub> = 2.8 V                              |                       |                                                                                                                                                                     | 95   | 160  |     |

| V <sub>IN2</sub> to V <sub>OUT1</sub> Dropout Voltage | I <sub>OUT1</sub> = 50                                                                                                 | $00 \text{ mA}, V_{\text{IN1}} = V_{\text{IN2}}$                | Notes 5, 6)                                                 | V <sub>DO(IN2)</sub>  |                                                                                                                                                                     | 1.1  | 1.5  | V   |

| Output Current Limit                                  | OUT1                                                                                                                   | V <sub>OUT</sub> = 90% V <sub>OUT</sub>                         | (NOM)                                                       | I <sub>CL</sub>       | 550                                                                                                                                                                 | 850  |      | mA  |

|                                                       | OUT2                                                                                                                   |                                                                 |                                                             |                       | 300                                                                                                                                                                 | 550  |      |     |

| Quiescent Current IN1                                 | I <sub>OUT1</sub> = 0                                                                                                  | mA                                                              |                                                             | I <sub>Q1</sub>       |                                                                                                                                                                     | 10   | 20   | μΑ  |

| Quiescent Current IN2                                 | $I_{OUT2} = 0$                                                                                                         | mA                                                              |                                                             | I <sub>Q2</sub>       |                                                                                                                                                                     | 80   | 130  |     |

| Disable Current                                       | V <sub>IN1</sub> Pin                                                                                                   | $V_{EN1} \le 0.4 \text{ V}$                                     |                                                             | I <sub>IN1(DIS)</sub> |                                                                                                                                                                     | 0.05 | 1    | μΑ  |

|                                                       | $V_{\text{IN2}}$ Pin                                                                                                   |                                                                 |                                                             | I <sub>IN2(DIS)</sub> |                                                                                                                                                                     | 0.1  | 1    |     |

| EN Pin Threshold Voltage                              | EN Input                                                                                                               | √oltage "H"                                                     |                                                             | V <sub>EN(H)</sub>    | 0.9                                                                                                                                                                 |      |      | V   |

|                                                       | EN Input                                                                                                               | √oltage "L"                                                     |                                                             | V <sub>EN(L)</sub>    |                                                                                                                                                                     |      | 0.4  |     |

| EN Pull Down Current                                  | V <sub>EN</sub> = 5.5                                                                                                  | V                                                               |                                                             | I <sub>EN</sub>       |                                                                                                                                                                     | 0.3  | 2    | μΑ  |

| Turn-On Delay                                         | OUT1                                                                                                                   | From assertion of \                                             | V <sub>EN</sub> to raising V <sub>OUT</sub>                 | t <sub>DELAY</sub>    |                                                                                                                                                                     | 200  |      | μs  |

|                                                       | OUT2                                                                                                                   |                                                                 |                                                             |                       |                                                                                                                                                                     | 130  |      |     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>4.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at TA = 25°C. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible.

<sup>5.</sup> Dropout voltage is characterized when VOUT falls 3% below VOUT(NOM).

<sup>6.</sup> For output 1 voltages below 0.9 V,  $V_{IN2}$  to  $V_{OUT1}$  dropout voltage does not apply due to a minimum  $V_{IN2}$  operating voltage of 2.4 V.

<sup>7.</sup> Refer to Table 6 for output slew rate configuration.

Table 4. ELECTRICAL CHARACTERISTICS  $-40^{\circ}C \le T_J \le 125^{\circ}C$ ;  $V_{IN1} = V_{OUT1(NOM)} + 0.3$  V,  $V_{IN2} = 2.7$  V or  $(V_{OUT1} + 1.6$  V) or  $V_{OUT2(NOM)} + 0.3$  V whichever is greater,  $I_{OUT1} = I_{OUT2} = 1$  mA,  $V_{EN} = 1$  V, unless otherwise noted.  $C_{IN1} = C_{IN2} = 1$  μF,  $C_{OUT1} = 2.2$  μF,  $C_{OUT2} = 1$  μF. Typical values are at  $T_J = +25^{\circ}C$ . Min/Max values are for  $-40^{\circ}C \le T_J \le 125^{\circ}C$  unless otherwise noted.

| Parameter                           | Test Conditions                                             |                                                                | Symbol                  | Min | Тур | Max | Unit  |

|-------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| V <sub>OUT</sub> Slew Rate (Note 7) | Normal                                                      |                                                                | V <sub>OUT1</sub>       |     | 100 |     | mV/μs |

|                                     |                                                             |                                                                | V <sub>OUT2</sub>       |     | 200 |     | 1     |

|                                     | Slow                                                        |                                                                | V <sub>OUT1</sub>       |     | 15  |     | 1     |

|                                     |                                                             |                                                                | V <sub>OUT2</sub>       |     | 30  |     | 1     |

| Power Supply Rejection Ratio        | V <sub>IN1</sub> to V <sub>O</sub><br>V <sub>OUT</sub> +0.5 | $S_{OUT1}$ , f = 1 kHz, $I_{OUT1}$ = 150 mA, $V_{IN1} \ge 5$ V | PSRR(V <sub>IN1</sub> ) |     | 70  |     | dB    |

|                                     | V <sub>IN2</sub> to V <sub>O</sub><br>V <sub>OUT</sub> +0.5 | $_{OUT2}$ , f = 1 kHz, $I_{OUT2}$ = 10 mA, $V_{IN2} \ge$       | PSRR(V <sub>IN2</sub> ) |     | 92  |     |       |

|                                     | V <sub>IN2</sub> to V <sub>O</sub><br>V <sub>OUT1</sub> +0. | $_{OUT1}$ , f = 1 kHz, $I_{OUT1}$ = 150 mA, $V_{IN1} \ge$ 5 V  | PSRR(IN2 to<br>OUT1)    |     | 80  |     |       |

| Output Noise Voltage                | OUT1                                                        | V <sub>IN</sub> = V <sub>OUT</sub> +0.5 V                      | $V_N$                   |     | 40  |     | μVRMS |

|                                     | OUT2                                                        | f = 10 Hz to 100 kHz                                           |                         |     | 8.5 |     | 1     |

| Thermal Shutdown Threshold          | Temperatu                                                   | Temperature increasing                                         |                         |     | 160 |     | °C    |

|                                     | Temperatu                                                   | ure decreasing                                                 | T <sub>SDH</sub>        |     | 140 |     | 1     |

| Output Discharge Pull-Down          | V <sub>EN</sub> ≤ 0.4<br>(only if Ac                        | V<br>tive Discharge feature enabled)                           | R <sub>DISCH</sub>      |     | 150 |     | Ω     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. Dropout voltage is characterized when VouT falls 3% below VouT(NOM).

<sup>4.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at TA = 25°C. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible.

<sup>6.</sup> For output 1 voltages below 0.9 V, V<sub>IN2</sub> to V<sub>OUT1</sub> dropout voltage does not apply due to a minimum V<sub>IN2</sub> operating voltage of 2.4 V. 7. Refer to Table 6 for output slew rate configuration.

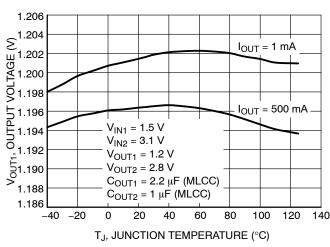

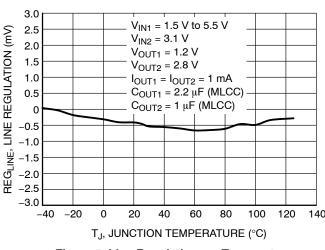

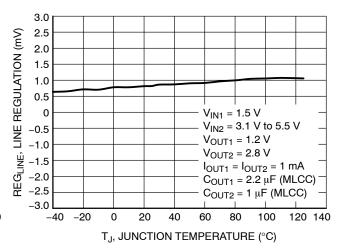

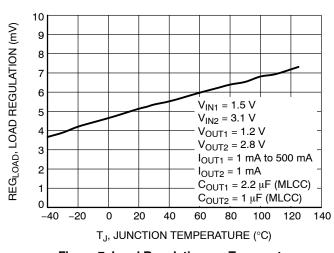

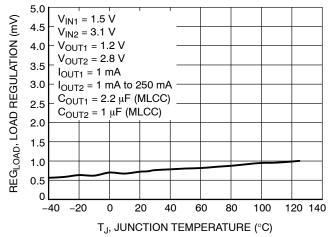

## **TYPICAL CHARACTERISTICS**

2.808 2.806 2.806 2.804 2.802 2.802 2.800  $I_{OUT} = 1 \text{ mA}$  $I_{OUT} = 250 \text{ mA}$ OUTPUT 2.798  $V_{IN1} = 1.5 V$ 2.796  $V_{IN2} = 3.1 \text{ V}$ 2.794  $V_{OUT1} = 1.2 V$ Voute,  $V_{OUT2} = 2.8 V$ 2.792  $C_{OUT1} = 2.2 \,\mu\text{F} \,(\text{MLCC})$ 2.790  $C_{OUT2} = 1 \mu F (MLCC)$ 2.788 -40 -20 40 60 80 100 120 140

T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 3. Output Voltage vs. Temperature –  $V_{OUT1} = 1.2 \text{ V}$

Figure 4. Output Voltage vs. Temperature –  $V_{OUT2}$  = 2.8 V

Figure 5. Line Regulation vs. Temperature –  $V_{OUT1} = 1.2 \text{ V}$

Figure 6. Line Regulation vs. Temperature –  $V_{OUT} = 2.8 \text{ V}$

Figure 7. Load Regulation vs. Temperature –  $V_{OUT1} = 1.2 \text{ V}$

Figure 8. Load Regulation vs. Temperature – V<sub>OUT</sub> = 2.8 V

## **APPLICATIONS INFORMATION**

#### General

The NCP156 is a 500 mA/250 mA dual output high performance Low Dropout Linear Regulator. It offers unique combination of N-MOS and P-MOS regulators to provide the best performance and power efficiency. The device is optimized for camera sensor applications to supply digital and analog power rails. Digital supply rail requires high current, low input voltage and as low as possible dropout to achieve the best efficiency and analog pixel array requires less current but very stable and clean supply line with very fast transient response. The NCP156 is offered in WLCSP6 package which helps with high integration as close as possible to sensor for best parameters.

## Input Capacitor Selection (CIN)

It is recommended to connect at least a 1  $\mu F$  Ceramic X5R or X7R capacitor as close as possible to the IN pin of the device. Larger input capacitor may be necessary if fast and large load transients are encountered in the application. This capacitor will provide a low impedance path for unwanted AC signals or noise modulated onto constant input voltage. There is no requirement for the min. or max. ESR of the input capacitor but it is recommended to use ceramic capacitors for their low ESR and ESL. A good input capacitor will limit the influence of input trace inductance and source resistance during sudden load current changes.

## Output Decoupling (COUT)

The NCP156 requires an output capacitor for each output connected as close as possible to the output pin of the regulator. The recommended capacitor value for OUT1 is 2.2  $\mu F$  and X7R or X5R dielectric due to its low capacitance variations over the specified temperature range. Recommended output capacitor for OUT2 is 1  $\mu F$  same type as OUT1. The NCP156 is designed to remain stable with minimum effective capacitance of 1  $\mu F$  for OUT1 and 0.7  $\mu F$  for OUT2 to account for changes with temperature, DC bias and package size. Especially for small package size capacitors such as 0201 the effective capacitance drops rapidly with the applied DC bias.

There is no requirement for the minimum value of Equivalent Series Resistance (ESR) for the  $C_{OUT}$  but the maximum value of ESR should be less than 1.9  $\Omega$ . Larger output capacitors and lower ESR could improve the load transient response or high frequency PSRR. It is not recommended to use tantalum or electrolytic capacitors on the output due to their large ESR. They can be used in connection with appropriate ceramic capacitor as secondary energy reservoir.

## **Input Voltage Requirements**

The NCP156 is combination N-MOS and P-MOS regulators in one package. It brings specific needs to proper design of power supply voltage rails. Input voltage 1 can be as low as V<sub>OUT1\_NOM</sub>+V<sub>DO1</sub> with minimal impact on performance. Typical parameters are characterized for

$V_{OUT1\_NOM} + 0.3$  V. The input voltage 2 is used as bias voltage of N-MOS output together with supply OUT2 and must be chosen more carefully. The basic condition to  $V_{IN2}$  selections is the same as for first input  $V_{IN2} \ge V_{OUT2\_NOM} + V_{DO2}$ . Due to the fact that  $V_{IN2}$  is also bias voltage for N-MOS regulator difference between  $V_{OUT1}$  and  $V_{IN2}$  must be at least 1.5 V.

The internal voltage references for both channels have cascade topology. It means reference  $V_{REF2}$  for OUT2 is derived from IN2 and reference for OUT1 is derived also from reference  $V_{REF2}$  not from  $V_{IN1}$ . All negative effects on  $V_{REF2}$  is visible also on  $V_{REF1}$  and then on  $V_{OUT1}$ . The reference voltage  $V_{REF2}$  has same value as  $V_{OUT2}$  due to there is necessary to have enough voltage headroom between  $V_{IN2}$  and  $V_{OUT2}$ . If  $V_{OUT2}$  is in dropout region then OUT1 is affected too. Consequently the OUT1 output voltage is lower than nominal due to lower  $V_{REF1}$  reference which is affected by drop  $V_{REF2}$ . For more information please refer design note  $\underline{DN05110/D}$ .

## **Enable Operation**

The NCP156 uses the single EN pin for both output channels. If the EN pin voltage is <0.4 V the device is guaranteed to be disabled. The pass transistors are turned–off so that there is virtually no current flow between the INs and OUTs. According to selected option the active discharge transistors are active so that the output voltages are pulled to GND through a 150  $\Omega$  resistor. In the disable state the device consumes as low as typ. 150 nA from the power supply. Active discharge feature is available for each output and can be select during manufacturing. It is necessary to choose correct option by exact device part number. Possible OPN configurations are in Table 5 below.

If the EN pin voltage >0.9 V the device is guaranteed to be enabled. The NCP156 regulates the output voltage and the active discharge transistor is turned–off.

The EN pin has internal pull-down current source with typ. value of 300 nA which assures that the device is turned-off when the EN pin is not connected. In the case where the EN function isn't required the EN should be tied directly to IN.

#### **Slew Rate Control**

The NCP156 is optimized for camera sensor application and meets all requirements for using in modern camera applications such as a smartphones, cameras and image capture devices. Power supply specification of sensors often requires output voltage slew rate limitation to protect sensor during regulator start-up. The NCP156 incorporates soft-start feature which can assure safe start-up output voltage ramp without excess current spikes and voltage undershoots. The device provides two options of slew rate speed, normal means typical slew rate about 100/200 mV/µs (OUT1/OUT2) and slow option means <15/30 mV/µs. Option is set during manufacturing process and cannot be

modified later. The possible slew rate configuration is explained in below in Table 6.

## **Output Current Limit**

The NCP156 provides output overcurrent protection on each output which limits maximum output current. Typical values are 850 mA for OUT1 and 550 mA for OUT2. The NCP156 will source this amount of current measured with a voltage drops on the 90% of the nominal  $V_{\rm OUT}$ . If the Output Voltage is directly shorted to ground ( $V_{\rm OUT}$  = 0 V), the short circuit protection will limit the output current typically to 880 mA on OUT1 and 590 mA on OUT2. The current limit and short circuit protection will work properly over whole temperature range and also input voltage range. There is no limitation for the short circuit duration. This protection works separately for each channel. Short circuit on the one channel do not influence second channel which will work according to specification.

#### Thermal Shutdown

When the die temperature exceeds the Thermal Shutdown threshold ( $T_{SD}$  –  $160^{\circ}$ C typical), Thermal Shutdown event is detected and the affected channel is turn–off. Second channel still working. The channel which is overheated will remain in this state until the die temperature decreases below the Thermal Shutdown Reset threshold ( $T_{SDU}$  –  $140^{\circ}$ C typical). Once the device temperature falls below the  $140^{\circ}$ C the appropriate channel is enabled again. The thermal

shutdown feature provides the protection from a catastrophic device failure due to accidental overheating. This protection is not intended to be used as a substitute for proper heat sinking. The long duration of the short circuit condition to some output channel could cause turn–off other output when heat sinking is not enough and temperature of the other output reach T<sub>SD</sub> temperature.

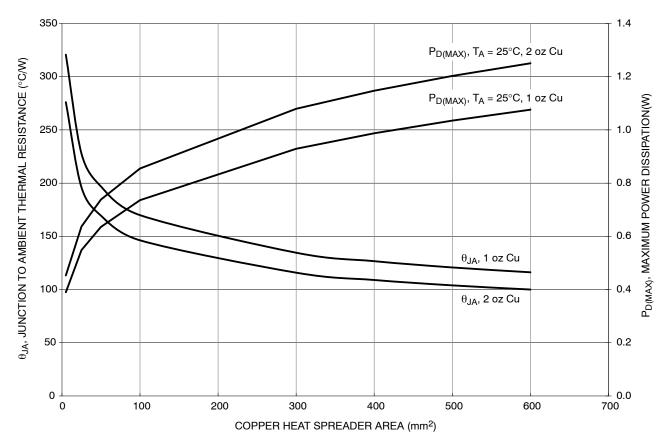

## **Power Dissipation**

As power dissipated in the NCP156 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part.

The maximum power dissipation the NCP156 can handle is given by:

$$P_{D(MAX)} = \frac{125^{\circ}C - T_{A}}{\theta_{JA}}$$

(eq. 1)

The power dissipated by the NCP156 for given application conditions can be calculated from the following equations:

$$\begin{split} P_{D} &\approx \left(V_{IN1} \times I_{GND1}\right) + \left(V_{IN2} \times I_{GND2}\right) + \\ &+ I_{OUT1} \!\! \left(V_{IN1} - V_{OUT1}\right) + I_{OUT2} \!\! \left(V_{IN2} - V_{OUT2}\right) \end{split} \tag{eq. 2}$$

Figure 9.  $\theta_{JA}$  vs. Copper Area (WLCSP-6)

### **Reverse Current**

The PMOS pass transistor has an inherent body diode which will be forward biased in the case that  $V_{OUT} > V_{IN}$ . Due to this fact in cases, where the extended reverse current condition can be anticipated the device may require additional external protection.

## **Power Supply Rejection Ratio**

The NCP156 features very good Power Supply Rejection ratio. If desired the PSRR at higher frequencies in the range  $100~\rm kHz-10~MHz$  can be tuned by the selection of  $C_{OUT}$  capacitor and proper PCB layout.

### **PCB Layout Recommendations**

To obtain good transient performance and good regulation characteristics place input and output capacitors close to the device pins and make the PCB traces wide. In order to minimize the solution size, use 0402 capacitors. Larger copper area connected to the pins will also improve the device thermal resistance. The actual power dissipation can be calculated from the equation above (Equation 2). Expose pad should be tied the shortest path to the GND pin.

### **OPN Selection Guide**

The NCP156 device offers various combinations of active discharge feature and  $V_{OUT}$  slew rate speed for each output channel. The OPN contains two letters behind product name which are dedicated for Active discharge and Slew rate speed. Possible combinations with corresponding letters are explained below.

**Table 5. ACTIVE DISCHARGE OPTION**

| Act. Discharge (x = ON) | OUT1 | OUT2 |

|-------------------------|------|------|

| А                       | х    | х    |

| В                       |      |      |

| С                       | х    |      |

| D                       |      | х    |

Table 6. V<sub>OUT</sub> SLEW RATE SPEED

| Slew rate (x = Slower) | OUT1 | OUT2 |

|------------------------|------|------|

| Α                      | х    | х    |

| В                      |      |      |

| С                      | х    |      |

| D                      |      | х    |

#### ORDERING INFORMATION

| Device                | Marking | Voltage Option<br>OUT1 / OUT2 | Active Discharge<br>OUT1 / OUT2 | V <sub>OUT</sub> Slew Rate<br>OUT1 / OUT2 | Package   | Shipping <sup>†</sup> |

|-----------------------|---------|-------------------------------|---------------------------------|-------------------------------------------|-----------|-----------------------|

| NCP156AAFCT100280T2G* | DL      | 1.0 V / 2.8 V                 | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156AAFCT105280T2G  | DM      | 1.05 V / 2.8 V                | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156AAFCT110280T2G* | DN      | 1.1 V / 2.8 V                 | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156AAFCT120180T2G* | DA      | 1.2 V / 1.8 V                 | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156AAFCT120270T2G* | DP      | 1.2 V / 2.7 V                 | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156AAFCT120280T2G  | DR      | 1.2 V / 2.8 V                 | Yes / Yes                       | Slow / Slow                               |           |                       |

| NCP156ABFCT100280T2G  | DD      | 1.0 V / 2.8 V                 | Yes / Yes                       | Normal / Normal                           | WLCSP6    | 5000 /                |

| NCP156ABFCT105280T2G* | DK      | 1.05 V / 2.8 V                | Yes / Yes                       | Normal / Normal                           | (Pb-Free) | Tape &<br>Reel        |

| NCP156ABFCT110280T2G  | DE      | 1.1 V / 2.8 V                 | Yes / Yes                       | Normal / Normal                           |           |                       |

| NCP156ABFCT120270T2G* | DG      | 1.2 V / 2.7 V                 | Yes / Yes                       | Normal / Normal                           |           |                       |

| NCP156ABFCT120280T2G  | DF      | 1.2 V / 2.8 V                 | Yes / Yes                       | Normal / Normal                           |           |                       |

| NCP156ABFCT180250T2G* | DJ      | 1.8 V / 2.5 V                 | Yes / Yes                       | Normal / Normal                           |           |                       |

| NCP156ABFCT180270T2G* | DH      | 1.8 V / 2.7 V                 | Yes / Yes                       | Normal / Normal                           |           |                       |

| NCP156BBFCT120180T2G* | DC      | 1.2 V / 1.8 V                 | No / No                         | Normal / Normal                           |           |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>Please contact local sales representative for availability.

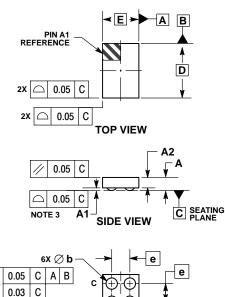

WLCSP6, 1.20x0.80 CASE 567MV ISSUE B

**DATE 05 JUN 2018**

**BOTTOM VIEW**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M. 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

|     | MILLIMETERS |          |  |  |

|-----|-------------|----------|--|--|

| DIM | MIN         | MAX      |  |  |

| Α   |             | 0.33     |  |  |

| A1  | 0.04        | 0.08     |  |  |

| A2  | 0.23        | REF      |  |  |

| b   | 0.24        | 0.30     |  |  |

| D   | 1.20 BSC    |          |  |  |

| E   | 0.80        | 0.80 BSC |  |  |

| e   | 0.40        | BSC      |  |  |

## **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code

М = Month Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

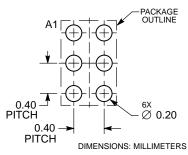

## **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON06670G       | Electronic versions are uncontrolled except when accessed directly from the Document Repo<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | WLCSP6, 1.20x0.80 |                                                                                                                                                                              | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative