# austriamicrosystems AG

is now

# ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

# **Headquarters:**

ams AG

Tobelbaderstrasse 30

8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0

e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

# **AS3665**

#### Datasheet, Confidential

## 9 Channel Advanced Command Driven RGB/White LED Driver

# 1 General Description

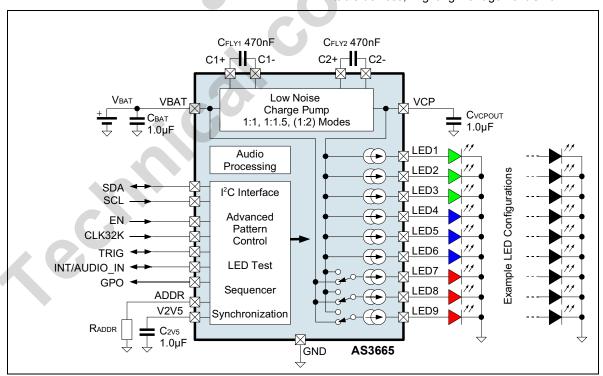

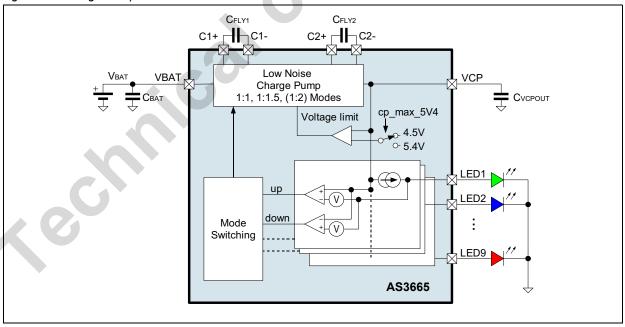

The AS3665 is a capacitive low noise charge pump with 9 current sources. The charge pump automatically switches between 1:1 and 1:1.5 modes. The connected current sources have a very low voltage compliance to improve efficiency of the whole system. Three current sources have the possibility to operate either from VBAT or VCP (especially useful for red LEDs).

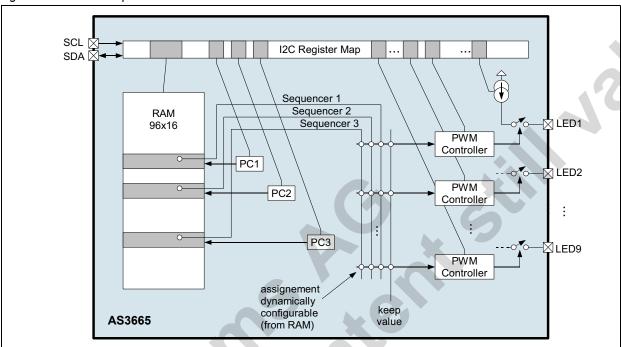

The internal control is done by command based pattern generators implemented by three sequencers. These commands are optimized for lighting applications (e.g. ramp up brightness logarithmically). It includes high level commands like conditionals jumps and variables. Any of the three sequencers can be dynamically mapped to any of the 9 PWM generators for the LEDs.

The AS3665 supports an audio input and sophisticated light patterns can be controlled by internal digital filters.

The AS3665 is controlled by I<sup>2</sup>C mode. Synchronization over several AS3665 is possible by the TRIG pin.

The AS3665 is available in a space-saving WL-CSP-25 (2.610x2.675mm) 0.5mm pitch and operates over the - 30°C to +85°C temperature range.

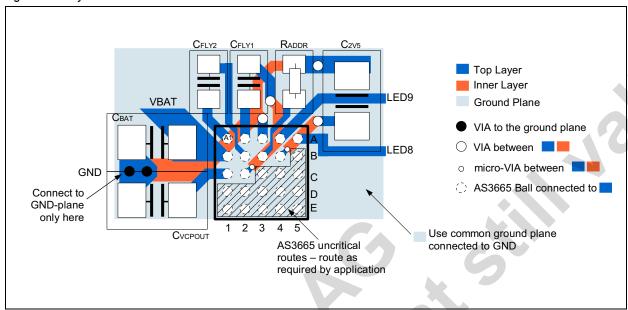

Figure 1. Typical Operating Circuit

# 2 Key Features

- High efficiency capacitive 150mA charge pump with 1:1, 1:1.5 and 1:2 modes with automatic mode switching; 1:2 mode can be disabled

- 9 Channel High Side 20mA Current sources

- Less than 50mV at 10mA dropout voltage

- LED7,8,9 either powered by VBAT or VCP

- Advanced Command based Pattern Generator

- 96 x 16 bits program memory

- Dedicated lighting commands like logarithmic fade

- Programming control and conditional jumps

- Audio Controlled Lighting with internal digital filters

- 3 Sequencers

- Dynamically mapped to 9 PWM generators

- Internal/External Synchronization

- 9 PWM generators (12 bit resolution)

- Automatic RGB Color Correction by TAMB

- I<sup>2</sup>C interface with dedicated EN pin

- Available in WL-CSP-25 (2.610x2.675mm) 0.5mm pitch

# 3 Applications

RGB/White Fun or Event LED for mobile phones or portable devices; Lighting Management Unit

# 4 Pinout

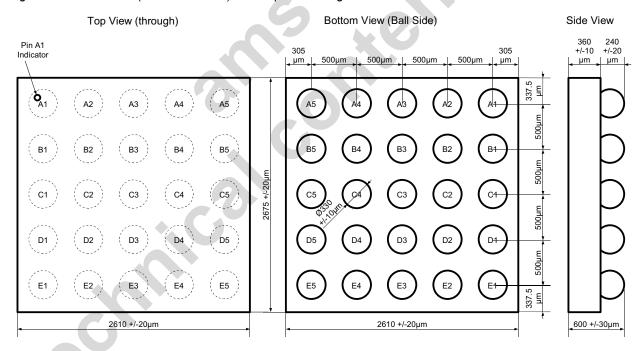

# Pin Assignment

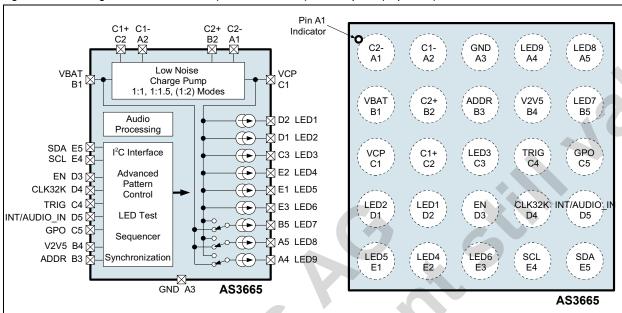

Figure 2. Pin Assignments WL-CSP-25 (2.610x2.675mm) 0.5mm pitch (Top View)

## **Pin Description**

Table 1. Pin Description for AS3665

| Pin Number | Pin Name                      | Description                                                                                                                       |

|------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| A1         | C2-                           | Charge Pump flying capacitor 2 - make a short connection to capacitor CFLY2                                                       |

| A2         | C1-                           | Charge Pump flying capacitor 1 - make a short connection to capacitor CFLY1                                                       |

| A3         | GND                           | Ground supply input pin                                                                                                           |

| A4         | LED9                          | LED9 output - current source from VCP or VBAT                                                                                     |

| A5         | LED8                          | LED8 output - current source from VCP or VBAT                                                                                     |

| B1         | VBAT                          | Positive supply input pin                                                                                                         |

| B2         | C2+                           | Charge Pump flying capacitor 2 - make a short connection to capacitor CFLY2                                                       |

| В3         | ADDR                          | Digital input - I <sup>2</sup> C address select; the value of the resistor RADDR defines the actual I <sup>2</sup> C address used |

| B4         | C <sub>2</sub> V <sub>5</sub> | Internal supply - connect a 1µF ceramic capacitor between C2V5 and GND                                                            |

| B5         | LED7                          | LED7 output - current source from VCP or VBAT                                                                                     |

| C1         | VCP                           | Charge Pump output - make a short connection to capacitor CVCPOUT                                                                 |

| C2         | C1+                           | Charge Pump flying capacitor 1 - make a short connection to capacitor CFLY1                                                       |

| C3         | LED3                          | LED3 output - current source from VCP                                                                                             |

| C4         | TRIG                          | Digital open drain input/output - used to synchronize across several AS3665                                                       |

| C5         | GPO                           | Digital open drain input/output - General purpose output and ADC input                                                            |

| D1         | LED2                          | LED2 output - current source from VCP                                                                                             |

| D2         | LED1                          | LED1 output - current source from VCP                                                                                             |

Table 1. Pin Description for AS3665 (Continued)

| Pin Number | Pin Name     | Description                                                                                                                                               |

|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| D3         | EN           | Digital input - active high enable for AS3665                                                                                                             |

| D4         | CLK32K       | Digital clock input - connect a 32.768kHz signal; if this signal is not available, connect this pin to GND                                                |

| D5         | INT/AUDIO_IN | Depending on the AS3665 configuration INT/AUDIO_IN is a  1. Open drain digital output - interrupt output pin  2. Analog input - audio or ADC signal input |

| E1         | LED5         | LED5 output - current source from VCP                                                                                                                     |

| E2         | LED4         | LED4 output - current source from VCP                                                                                                                     |

| E3         | LED6         | LED6 output - current source from VCP                                                                                                                     |

| E4         | SCL          | Digital input - clock input for I <sup>2</sup> C communication                                                                                            |

| E5         | SDA          | Digital open drain input/output - data input/output for I <sup>2</sup> C communication                                                                    |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3, "Electrical Characteristics," on page 5 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                                        | Min  | Max          | Units | Comments                                        |

|------------------------------------------------------------------|------|--------------|-------|-------------------------------------------------|

| VBAT, VCP, C1+, C1-,<br>C2+, C2- to GND                          | -0.3 | +7.0         | V     |                                                 |

| VCP to VBAT                                                      | -0.3 |              | V     | Note: Diode between VCP and VBAT                |

| LED1, LED2LED9 to GND                                            | -0.3 | VCP +<br>0.3 | V     |                                                 |

|                                                                  |      | 7.0          |       |                                                 |

| SDA, SCL, EN, CLK32K, TRIG, INT/AUDIO_IN, GPO, ADDR, C2V5 to GND | -0.3 | VBAT + 0.3   | V     |                                                 |

| INT/AODIO_IIV, GLO, ADDIX, G2V3 to GND                           |      | 7.0          |       |                                                 |

| Input Pin Current without causing latchup                        | -100 | +100<br>+lin | mA    | Norm: EIA/JESD78                                |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)            |      |              |       |                                                 |

| Continuous power dissipation                                     |      | 0.78         | mW    | PT <sup>1</sup>                                 |

| Continuous power dissipation derating factor                     |      | 14.2         | mW/°C | PDERATE <sup>2</sup>                            |

| Electrostatic Discharge                                          |      |              |       |                                                 |

| ESD HBM                                                          |      | ±1000        | V     | Norm: JEDEC JESD22-A114F                        |

| ESD CDM                                                          |      | ±500         | V     | Norm: JEDEC JESD 22-C101C                       |

| ESD MM                                                           |      | ±200         | V     | Norm: JEDEC JESD 22-A115-A level A              |

| Temperature Ranges and Storage Condition                         | ns   |              |       |                                                 |

| Junction Temperature                                             |      | +150         | °C    | Internally limited (overtemperature protection) |

| Storage Temperature Range                                        | -55  | +125         | °C    |                                                 |

| Humidity                                                         | 5    | 85           | %     | Non condensing                                  |

| Body Temperature during Soldering                                |      | +260         | °C    | according to IPC/JEDEC J-STD-020C               |

<sup>1.</sup> Depending on actual PCB layout and PCB used

<sup>2.</sup> PDERATE derating factor changes the total continuous power dissipation (PT) if the ambient temperature is not 70°C. Therefore for e.g. TAMB=85°C calculate PT at 85°C = PT - PDERATE \* (85°C - 70°C)

# **6 Electrical Characteristics**

VVBAT = +2.7V to +5.5V, TAMB =  $-30^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise specified. Typical values are at VVBAT = +3.6V, TAMB =  $+25^{\circ}$ C, unless otherwise specified.

Table 3. Electrical Characteristics

| Symbol                | Parameter                                  | Condition                                                          | Min                   | Тур | Max   | Unit |      |

|-----------------------|--------------------------------------------|--------------------------------------------------------------------|-----------------------|-----|-------|------|------|

|                       | erating Conditions                         |                                                                    |                       |     | 7.    |      |      |

| VVBAT                 | Supply Voltage                             |                                                                    | 2.7                   | 3.6 | 5.5   | ٧    |      |

| VVBATREDU<br>CED_FUNC | Supply Voltage                             | AS3665 functionally workir parameters fulfil                       | 2.5                   |     | 2.7   | V    |      |

| Ishutdown             | Shutdown Current                           |                                                                    |                       |     | 0.4   | 1.3  | μA   |

| ISTANBY               | Standby mode Current                       | I <sup>2</sup> C interface act                                     | ive                   |     | 1.6   | 6.0  | μA   |

| IACTIVE               | Active mode Current                        | I <sup>2</sup> C interface act<br>Internal oscillator running, pro | ive<br>ogram executed |     | 300   |      | μA   |

| ICP1:1.5              | Charge Pump Current                        | Charge pump operating in no load curren                            | 1:1.5 mode,<br>it     | •   | 0.7   |      | mA   |

| Тамв                  | Operating<br>Temperature                   |                                                                    | 2                     | -30 | 25    | 85   | °C   |

| Charge Pun            | пр                                         |                                                                    |                       |     |       |      |      |

| Vvout                 | Charge Pump output<br>Voltage (pin VOUT)   | Internally Limite                                                  | ed                    |     |       | 5.5  | ٧    |

| Ivout                 | Charge Pump output current                 | 5                                                                  |                       | 0.0 |       | 150  | mA   |

| η                     | Efficiency                                 | - N                                                                |                       |     | 75    |      | %    |

| fclk                  | Operating Frequency                        | All internal timings are deri oscillator if no clock is applied    | -10%                  | 2.0 | +10%  | MHz  |      |

| Rcp                   | Charge pump                                | VVBAT>=3.3V, ILED=100mA                                            | 1:1 Mode              |     | 0.65  |      | Ω    |

| TOI                   | effective resistance                       | VVBA12 = 0.0 V, IEED = 100111/1                                    | 1:1.5 Mode            |     | 3.3   |      | Ω    |

| Current Sou           | irces                                      |                                                                    |                       |     |       |      |      |

| ILED19                | LED1LED9 output current range              |                                                                    |                       | 0.0 |       | 25.5 | mA   |

| lled19∆               | LED1LED9 current source accuracy           | ILED = 17.5mA                                                      | A                     | -7  |       | +7   | %    |

| ILED19<br>MATCH       | LED1LED9 current source matching           | ILED = 17.5mA                                                      | A                     |     | 2.5   |      | %    |

| ILED19<br>LEAKAGE     | LED1LED9 leakage current                   | current source                                                     | off                   | -5  | 0     | +5   | μΑ   |

| VILED_COMP            | LED1LED9 current source voltage compliance | Minimum voltage between p<br>LED1LED9 or VBAT and                  |                       |     | 100   | mV   |      |

| ADC                   |                                            |                                                                    |                       |     | •     |      |      |

| ADCRES                | ADC resolution                             |                                                                    |                       |     | 10    |      | Bits |

| ADCINL                | ADC Integral non-<br>linearity             |                                                                    |                       | -2  | ±0.2  | +2   | LSB  |

| ADCDNL                | ADC differential non-<br>linearity         |                                                                    |                       | -2  | ±0.25 | +2   | LSB  |

| ADCLSB                | LSB of ADC conversion                      |                                                                    |                       |     | 6.1   |      | mV   |

Table 3. Electrical Characteristics (Continued)

| Symbol                    | Parameter                                              | Condition                                                                                                | Min                       | Тур   | Max   | Unit        |

|---------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------------|

| ADCTOFFSE<br>T            | ADC temperature measurement offset value               |                                                                                                          |                           | 393   |       | °C          |

| ADCTC                     | Code temperature coefficient                           |                                                                                                          |                           | 1.322 |       | °C/<br>Code |

| TTOL                      | Temperature sensor accuracy                            |                                                                                                          | -10                       |       | +10   | °C          |

| Audio Input               |                                                        |                                                                                                          |                           | •     |       |             |

| Raudio_in                 | Audio Input resistance                                 | pin INT/AUDIO_IN if used as analog input;<br>at maximum input gain (+30dB)                               |                           | 20    |       | kΩ          |

| Digital Inter             | face                                                   |                                                                                                          |                           |       |       |             |

| VIH                       | High Level Input<br>Voltage                            | Pins SDA, SCL, EN, CLK32K, TRIG,                                                                         | 1.26                      |       | VVBAT | >           |

| VIL                       | Low Level Input<br>Voltage                             | INT/AUDIO_IN, GPO <sup>1</sup>                                                                           | 0.0                       |       | 0.54  | ٧           |

| Vol                       | Low Level Output<br>Voltage                            | Pins SDA, TRIG, INT/AUDIO_IN, GPO IOL=3mA                                                                |                           |       | 0.2   | <b>V</b>    |

| ILEAK                     | Leakage Current                                        | Pins SDA, SCL, EN, CLK32K, TRIG, INT/<br>AUDIO_IN, GPO                                                   |                           | 0.01  | 1.0   | μΑ          |

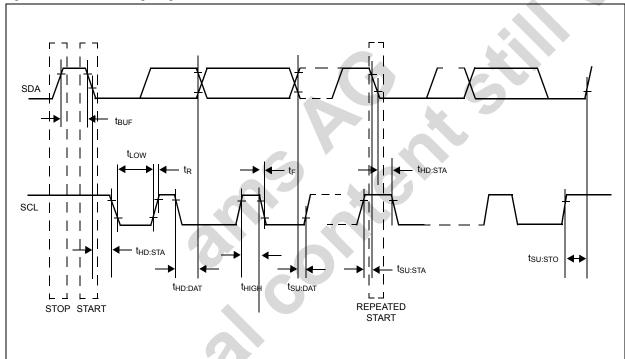

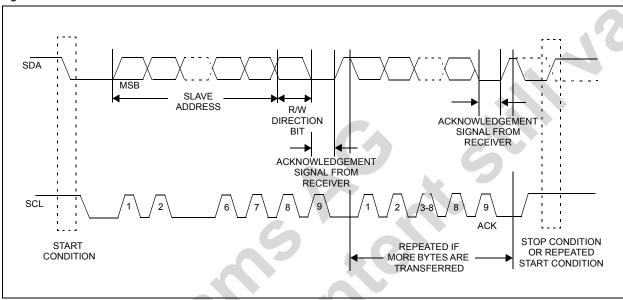

| I <sup>2</sup> C mode tir | mings - see Figure 3 or                                | n page 7                                                                                                 |                           |       |       |             |

| fsclk                     | SCL Clock Frequency                                    |                                                                                                          | 0                         |       | 400   | kHz         |

| t <sub>BUF</sub>          | Bus Free Time<br>Between a STOP and<br>START Condition | 70, 70,                                                                                                  | 1.3                       |       |       | μs          |

| thd:sta                   | Hold Time (Repeated) START Condition <sup>2</sup>      |                                                                                                          | 0.6                       |       |       | μs          |

| t <sub>LOW</sub>          | LOW Period of SCL<br>Clock                             | 70                                                                                                       | 1.3                       |       |       | μs          |

| t <sub>HIGH</sub>         | HIGH Period of SCL<br>Clock                            | . 0                                                                                                      | 0.6                       |       |       | μs          |

| t <sub>SU:STA</sub>       | Setup Time for a<br>Repeated START<br>Condition        |                                                                                                          | 0.6                       |       |       | μs          |

| t <sub>HD:DAT</sub>       | Data Hold Time <sup>3</sup>                            |                                                                                                          | 0                         |       | 0.9   | μs          |

| t <sub>SU:DAT</sub>       | Data Setup Time <sup>4</sup>                           |                                                                                                          | 100                       |       |       | ns          |

| t <sub>R</sub>            | Rise Time of Both<br>SDA and SCL Signals               |                                                                                                          | 20 +<br>0.1C <sub>B</sub> |       | 300   | ns          |

| t <sub>F</sub>            | Fall Time of Both SDA and SCL Signals                  |                                                                                                          | 20 +<br>0.1C <sub>B</sub> |       | 300   | ns          |

| tsu:sto                   | Setup Time for STOP<br>Condition                       |                                                                                                          | 0.6                       |       |       | μs          |

| СВ                        | Capacitive Load for<br>Each Bus Line                   | C <sub>B</sub> — total capacitance of one bus line in pF                                                 |                           |       | 400   | pF          |

| C <sub>I/O</sub>          | I/O Capacitance<br>(SDA, SCL)                          |                                                                                                          |                           |       | 10    | pF          |

| t <sub>TIMEOUT</sub>      | I <sup>2</sup> C timeout                               | If SCL and SDA are low for longer than this time, the AS3665 is switched into shutdown mode <sup>5</sup> |                           | 100   |       | ms          |

- 1. The logic input levels VIH and VIL allow for 1.8V supplied driving circuit

- 2. After this period the first clock pulse is generated.

- 3. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 4. A fast-mode device can be used in a standard-mode system, but the requirement  $t_{SU:DAT}$  = to 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_R$  max +  $t_{SU:DAT}$  = 1000 + 250 = 1250ns before the SCL line is released.

- 5. This feature can be disabled by setting auto\_shutdown (see page 13)=0

## **Timing Diagrams**

Figure 3. I<sup>2</sup>C mode Timing Diagram

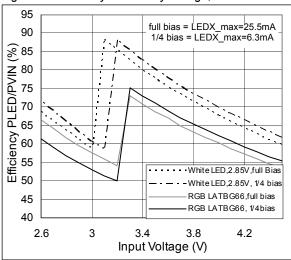

# 7 Typical Operating Characteristics

$V_{VBAT} = 3.6V$ ,  $T_A = +25^{\circ}C$  (unless otherwise specified).

Figure 4. Efficiency vs. Battery voltage, ILEDS=50mA

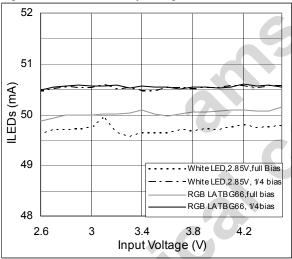

Figure 6. ILEDS vs. Battery voltage

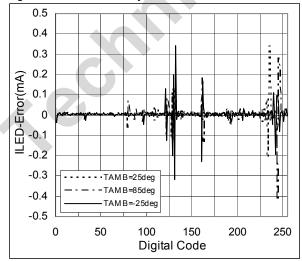

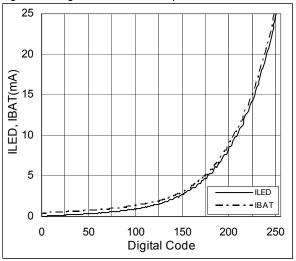

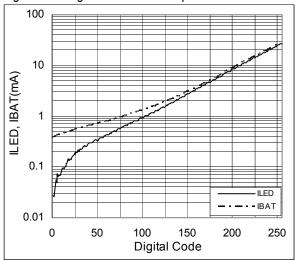

Figure 8. ILED1 Monotony of current source vs. Code

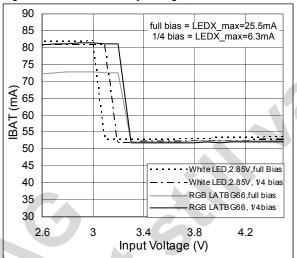

Figure 5. IVBAT vs. Battery voltage, ILEDS=50mA

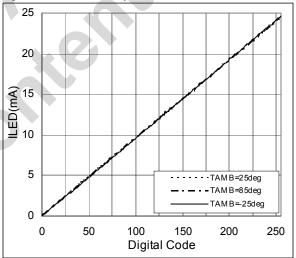

Figure 7. ILED1 Linearity of current source vs. Code

Figure 9. Logarithmic PWM ramp

Figure 10. Logarithmic PWM ramp

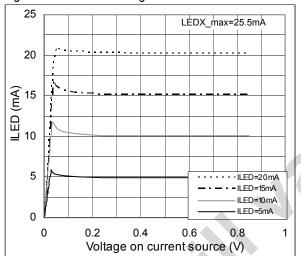

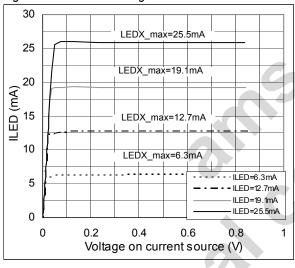

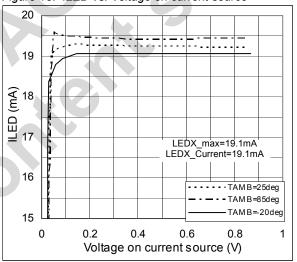

Figure 11. ILED vs. Voltage on current source

Figure 12. ILED vs. Voltage on current source

Figure 13. ILED vs. Voltage on current source

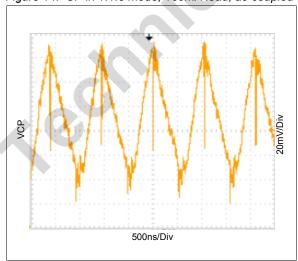

Figure 14. CP in 1:1.5 mode, 150mA load, ac-coupled

# 8 Detailed Description

The AS3665 is a fixed frequency charge pump. Its output (VOUT) is connected to nine current sources (LED1..LED9). A sophisticated command based pattern generator with three sequencers controls the nine PWM generators (12 bit resolution), which are connected to the current sources.

Commands are downloaded to the AS3665 internal memory space and can be executed autonomously in the three sequencers. The commands are optimized for lighting applications (e.g. a single command executes logarithmic up dimming). It supports command flow control (like unconditional and conditional jumps). Variables which are accessible through the I<sup>2</sup>C interface allow control of the program execution by the I<sup>2</sup>C interface and communication between the three sequencers.

The three sequencers can be dynamically assigned to any of the nine outputs (under program control).

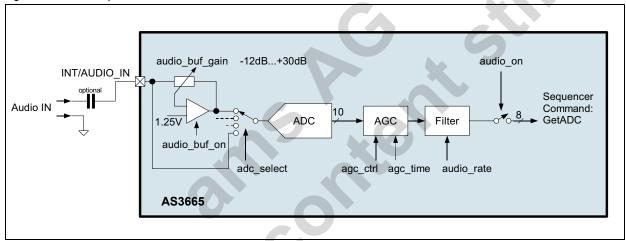

The AS3665 supports an audio input pin INT/AUDIO\_IN which allows the control of patterns depending on an audio input signal. This audio input can be feed through internal digital filters for better visual appearance.

If the audio feature is not used, the pin INT/AUDIO IN can be used as interrupt output 1 to send interrupts.

The AS3665 is controlled by an I<sup>2</sup>C interface and additional dedicated control lines. An EN input operates as a global enable/disable pin and with the pin TRIG several AS3665 can be synchronized in a system. A separate CLK32K input can be used to set an exact clock input frequency (all internal timings can be derived either from CLK32K or an internal oscillator). The I<sup>2</sup>C address is selectable by the pin ADDR - see I<sup>2</sup>C Address selection on page 40. A GPO pin can be used for external control or as an additional ADC input.

The AS3665 supports LED testing (verification of the performance of the connected LEDs in an assembled system). Following blocks are included inside the AS3665:

- Low Noise charge pump operating in 1:1, 1:1.5 and 1:2

- Automatic mode switching of the charge pump (up & down)

- 1MHz oscillator

- Internal LDO for powering the internal circuitry

- Audio processing of an analog input signal

- Overtemperature Protection

- Temperature Measurements of the AS3665

- 10 Bit ADC

- 9x12 bit, 1x8 bit PWM Generators

- 6 accurate current sources connected to VCP

- 3 accurate current source configurable to be connected to VBAT or VCP (to improve efficiency e.g. of red LEDs)

- Internal memory for the program execution

- 3 sequencers (3 parallel processing units)

- a fully programmable multiplexer connecting the three sequencers to the 10 PWM generators

- Automatic shutdown to safe power (if SCL and SDA=0 for 100ms)

-

<sup>1.</sup> INT/AUDIO\_IN is an open drain output. Several interrupt can be easily combined externally.

#### **Internal Circuit**

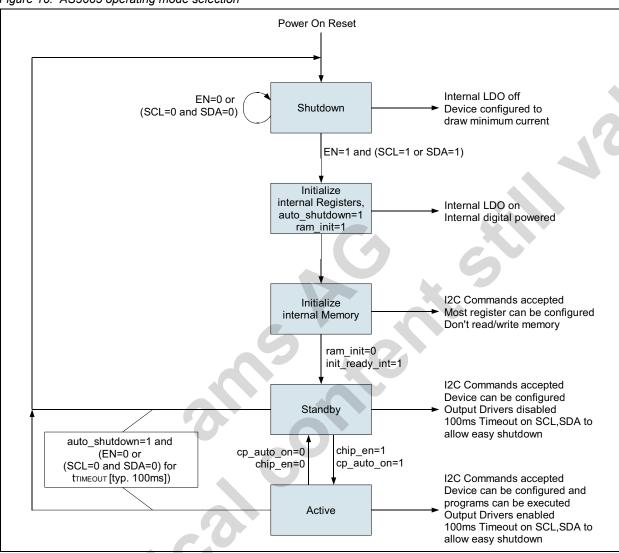

## **Device Operating Mode**

The operating mode is selected according to the following flowchart:

Figure 16. AS3665 operating mode selection

After power on reset, the AS3665 waits until EN=1 and SCL=1 or SDA=1<sup>2</sup> and then initializes its internal registers and program memory. Once standby mode is reached, the program and setup can be download to the AS3665 and by setting chip\_en=1 the program can be executed.

<sup>2.</sup> SCL and SDA is monitored to detect if the I<sup>2</sup>C bus is powered. Therefore if EN is not used, it can be tied to VBAT and the mode selection between shutdown and the other modes is performed by SCL and SDA.

If EN is pulled low or if the power from the  $I^2C$  bus pullup resistors is removed<sup>3</sup> for more than tTIMEOUT, the AS3665 enters shutdown<sup>4</sup>.

Table 4. Exec\_Enable Register

| Addr: 00h |          | Exec_Enable Register |        |                                                                                                                                                                                                                      |     |                                     |                                                                                                                                           |                                                       |

|-----------|----------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Bit       | Bit Name | Default              | Access | Description                                                                                                                                                                                                          |     |                                     |                                                                                                                                           |                                                       |

|           |          |                      |        | Enables the active mode (see Figure 16)                                                                                                                                                                              |     |                                     |                                                                                                                                           |                                                       |

| 6         | chip_en  | 0h                   | 0h     | 0h                                                                                                                                                                                                                   | R/W | R/W                                 | AS3665 standby mode select.  Set cp_auto_on=0 before setting chip_en=0.  Output drivers disabled, I <sup>2</sup> C communication possible |                                                       |

|           |          |                      |        | AS3665 active mode select.  Set cp_auto_on=1 after setting chip_en=1 All functions active, internal oscillator running.                                                                                              |     |                                     |                                                                                                                                           |                                                       |

|           |          |                      |        |                                                                                                                                                                                                                      |     |                                     |                                                                                                                                           | Initialization of the internal memory (see Figure 16) |

|           |          |                      |        |                                                                                                                                                                                                                      |     | 0 Memory initialization is finished |                                                                                                                                           |                                                       |

| 7         | ram_init | 0h                   | R/W    | Writing: Reset internal program memory and all register from 60hFFh to their default state Reading: memory initialization ongoing; when finished an interrupt can be triggered (init_ready_int (see page 37) is set) |     |                                     |                                                                                                                                           |                                                       |

The bit auto\_shutdown controls the automatic entering of shutdown mode if the I<sup>2</sup>C bus is disabled:

Table 5. Supervision Register

| Addr: 08h |                    |         |          | Supervision Register                                                        |

|-----------|--------------------|---------|----------|-----------------------------------------------------------------------------|

| Bit       | Bit Name           | Default | Access   | Description                                                                 |

|           |                    |         |          | Enables the shutdown mode (see Figure 16)                                   |

| 7         | 7 auto_shutdown 1h | 1h R/W  | 1h R/W 0 | AS3665 cannot enter shutdown do not set pin EN=0 if cp_auto_on=1 or cp_on=1 |

|           |                    |         | G        | AS3665 can use shutdown EN=0 can be used to enter shutdown mode             |

A complete reset cycle can be triggered by setting bit force\_reset:

Table 6. Reset\_Control Register

| Addr: 3Ch |             | Reset_Control Register |                    |                                                                |                  |  |

|-----------|-------------|------------------------|--------------------|----------------------------------------------------------------|------------------|--|

| Bit       | Bit Name    | Default                | Access Description |                                                                |                  |  |

|           |             |                        |                    | Start reset cycle (see Figure 16)                              |                  |  |

| 0         | force reset | 0                      | R/W                | 0                                                              | Normal operation |  |

|           | 0           |                        | 1                  | Reset all registers from 00h1Fh and 5Fh to their default value |                  |  |

<sup>3.</sup> Therefore SCL and SDA both are low.

<sup>4.</sup> Unless auto\_shutdown (see page 13)=0

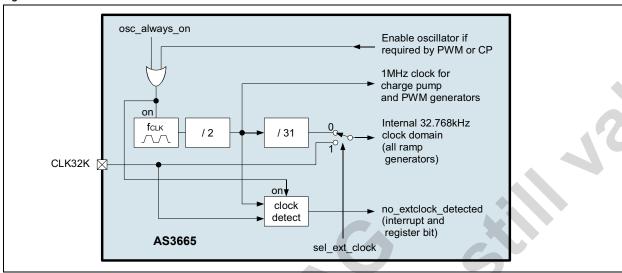

#### **Clock Generation**

The AS3665 has an internal oscillator running at fcLk and an external clock input CLK32K:

Figure 17. Clock Generation

The charge pump and the PWM generator use the fclk clock signal from the internal oscillator. Depending on the signal sel\_ext\_clock, the internal timers and ramp generators use either the pin CLK32K as input or fclk divided by 2 and 31.

Table 7. GPO\_Control Register

| Addr: 04h |               | GPO_Control Register |        |                                                      |  |  |

|-----------|---------------|----------------------|--------|------------------------------------------------------|--|--|

| Bit       | Bit Name      | Default              | Access | Description                                          |  |  |

|           |               | Oh                   |        | Enables the external clock on CLK32K (see Figure 17) |  |  |

| 6         | sel ext clock |                      | R/W    | 0 Use internal fcLκ clock divided by 31*2            |  |  |

|           | 001_0Xt_0100K |                      |        | Use external clock on CLK32K (also                   |  |  |

|           |               |                      |        | osc_always_on=0) <sup>1</sup>                        |  |  |

- 1. Using an external clock has two advantages:

- a) Reduced quiescent current: the internal clock is switched off whenever possible and the timers run from CLK32K.

- b) All timings (e.g. ramp-up, wait) are as accurate as the external clock (usually derived from a crystal).

The external clock on CLK32K is monitored and if the internal clock is enabled and no valid clock are detected the register bit no extclock detected (see page 37) is set and an interrupt can be triggered.

The internal oscillator is enabled and disabled automatically if register bit osc always on is reset:

Table 8. Supervision Register

| Addr: 08h |               | Supervision Register |                    |                                                                  |    |

|-----------|---------------|----------------------|--------------------|------------------------------------------------------------------|----|

| Bit       | Bit Name      | Default              | Access Description |                                                                  |    |

|           |               | 0h                   | R/W                | Enables the internal oscillator (see Figure 17)                  |    |

| 5         | osc always on |                      |                    | 0 Enable internal oscillator only if required                    |    |

|           | 000_aay0_0    |                      |                    | The internal oscillator is always running (except shutdown mode) | in |

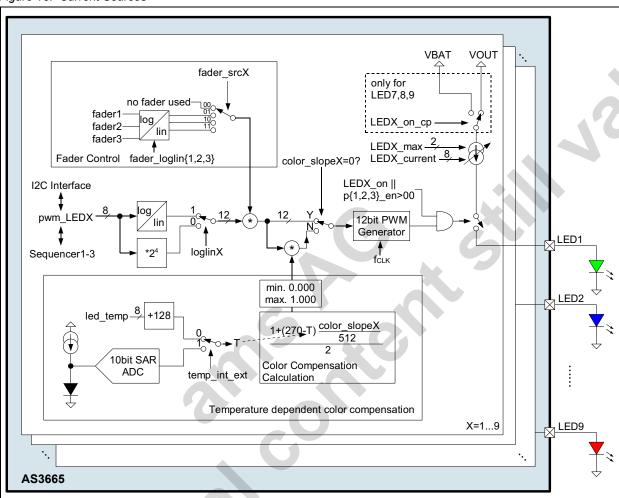

## **Current Sources**

The internal circuit of the current sources is shown in Figure 18 (one current source shown; internally there are 9 identical blocks):

Figure 18. Current Sources

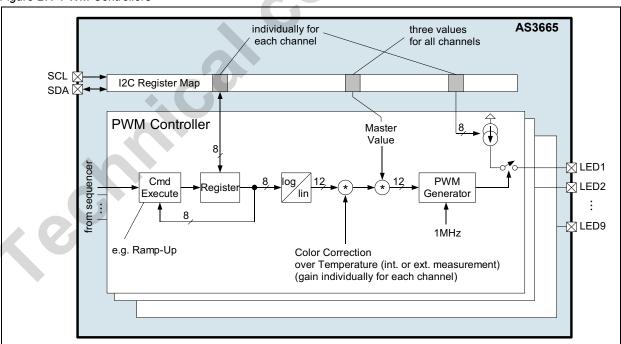

The processing path consists of the following step (using current source 1 as example):

- 1. The input of the complete current source block is the register pwm\_LED1 (see page 22). This register can be controlled by I<sup>2</sup>C directly or by any of the three sequencers (see section Sequencers on page 48).

- 2. The signal is converted from logarithmic domain to linear domain (depending on signal loglin1 (see page 25)) or multiplied by 16 to obtain 12 bits.

- 3. It passes an adjustable fader (it can be multiplied by any of the fader registers fader1, fader2 or fader3). If fader\_src1 (see page 25)=0, the fader is not used (signal is unchanged).

- 4. Color correction is performed (temp\_int\_ext (see page 24) selects either internal temperature measurement or use the register led\_temp (see page 24)). The gain of the color correction can be adjusted by color\_slope1 (see page 25). If color\_slope1=0, color correction is disabled.

- 5. The resulting 12 bit signal goes to the PMW generator and then to the current source itself.

- 6. The current source is enabled by LED1 on<sup>5</sup> and its current is adjusted by LED current1 and LED1 max.

<sup>5.</sup> LED1\_on...LED9\_on have only effect if all sequencer are switched off (p1\_en (see page 46)=00 and p2\_en=00 and p3\_en=00). This allow direct control of the LEDs if no program is executed.

LED7, LED8 and LED9 have the option to be powered by VBAT directly (configured by LED7\_on\_cp...LED9\_on\_cp)

#### Interface to sequencers

pwm\_LED1 (see page 22), pwm\_LED2...pwm\_LED9 is the input PWM value of the current sources (8 bit value). This value can be either controlled by the I<sup>2</sup>C interface or by any of the sequencers (see section Sequencers on page 48).

#### Logarithmic/Linear Ramping

All current sources support logarithmic or linear ramping (selected by register bits loglin1 (see page 25), loglin2...loglin9). As light is perceived logarithmically, it is recommended to keep the current sources in logarithmic mode (default setting).

#### **RGB Color Correction**

The RGB Color correction changes the output PWM value depending on the temperature (either the junction temperature if temp\_int\_ext (see page 24)=0, or a I<sup>2</sup>C value stored in led\_temp (see page 24) if temp\_int\_ext=1). This compensates different temperature drifts of LEDs and keep the white point over temperature. The slope of this temperature compensation is adjustable with the register color\_slope1 (see page 25), color\_slope2...color\_slope9 (set to 0 if the color correction is not used).

#### **Faders**

There are three global faders: fader1 (see page 23), fader2 and fader3. Each current source can be configured to be multiplied by any of the three faders (controlled by fader\_src1 (see page 25), fader\_src2...fader\_src9). Therefore a fader can operate on any number of current sources in parallel (e.g. to generate smooth fade-out effects on several LEDs). The faders can operate linear or logarithmic (defined by fader\_loglin1 (see page 23), fader\_loglin2 and fader\_loglin3).

#### **Analog Current Setting**

All current sources can be completely enabled/disable by the register LED1\_on, LED2\_on...LED9\_on. The actual analog current is set by LED\_current1 (see page 17), LED\_current2...LED\_current9. The maximum current driving capability of the current sources is set by registers LED1\_max (see page 20), LED2\_max...LED9\_max<sup>6</sup>.

#### **Current Source Registers**

Analog Current setting registers

Table 9. LED\_Control1 Register

| Addr: 02h |            | LED_Control1 Register |         |   |                 |  |

|-----------|------------|-----------------------|---------|---|-----------------|--|

| Bit       | Bit Name   | Default               | Access  |   | Description     |  |

| 0         | LED1_on    | 0b                    | R/W     | 0 | LED1 is off     |  |

|           | LLD1_0II   | UD                    | R/VV    | 1 | LED1 is enabled |  |

| 1         | LED2 on    | 0b                    | R/W     | 0 | LED2 is off     |  |

| ı         | CEDZ_011   | Ob                    | FX/VV   | 1 | LED2 is enabled |  |

| 2         | 2 LED3 on  | 0b                    | R/W     | 0 | LED3 is off     |  |

| 2         | EED3_011   | Ob                    | 17/77   | 1 | LED3 is enabled |  |

| 3         | LED4 on    | 0b                    | R/W     | 0 | LED4 is off     |  |

| ,         | 3 LED4_0II | OD                    | FX/ V V | 1 | LED4 is enabled |  |

| 4         | LED5_on    | 0b                    | R/W     | 0 | LED5 is off     |  |

| 4         |            |                       |         | 1 | LED5 is enabled |  |

<sup>6.</sup> Always use the minimum setting for LED1\_max, LED2\_max...LED9\_max suitable for the application to reduce quiescent current of the internal current source

Table 9. LED\_Control1 Register

| Addr: 02h |              | LED_Control1 Register |         |             |                 |         |        |         |          |        |             |             |

|-----------|--------------|-----------------------|---------|-------------|-----------------|---------|--------|---------|----------|--------|-------------|-------------|

| Bit       | Bit Name     | Default               | Access  | Description |                 |         |        |         |          |        |             |             |

| 5         | LED6 on      | 0b                    | 0b R/W  | 0           | LED6 is off     |         |        |         |          |        |             |             |

| 5         | LEDO_OH      |                       |         | 1           | LED6 is enabled |         |        |         |          |        |             |             |

| 6         | 6 LED7_on 0b | 0b                    | 0b R/W  | 0b R/W      | Oh              | 0h D/M/ | Ob DAM | 0b D/M  | 0b R/W - | 0      | LED7 is off |             |

| 0         |              |                       |         |             | FX/VV           | OD R/W  | IX/VV  | OD R/VV |          | FX/VV  | FV VV       | J   K/VV    |

| 7         | 7 LED8_on 0b | 0b R/W                | 01- 0   | Ol-         | 01- 044         | O.I.    | 01 500 | 01 5.44 | 01 5.44  | 0h D/M | 0           | LED8 is off |

| /         |              |                       | FX/ V V | 1           | LED8 is enabled |         |        |         |          |        |             |             |

Table 10. LED\_Control2 Register

| Addr: 03h |          |         | LED_Control2 Register |             |                 |  |  |  |

|-----------|----------|---------|-----------------------|-------------|-----------------|--|--|--|

| Bit       | Bit Name | Default | Access                | Description |                 |  |  |  |

| 0         | LED9 on  | 0b      | 0b R/W                |             | LED9 is off     |  |  |  |

|           | EED9_011 | OD      | FX/VV                 | 1           | LED9 is enabled |  |  |  |

Table 11. LED\_Current1 Register

| Addr: 10h |              |         |        | LED_Curre | ent1 Register |                 |               |        |

|-----------|--------------|---------|--------|-----------|---------------|-----------------|---------------|--------|

| Bit       | Bit Name     | Default | Access |           |               | Descript        | ion           |        |

|           |              |         |        |           | Sets the cu   | rrent for curre | ent source on | LED1   |

|           |              |         |        |           | W. (2)        | LED1            | _max          |        |

|           |              |         |        |           | 00            | 01              | 10            | 11     |

| 7:0       | LED_current1 | 00h     | R/W    | 0         |               | Current s       | source off    |        |

|           |              |         |        | 1         | 0.1mA         | 74.9µA          | 49.8µA        | 24.7µA |

|           |              |         |        |           |               |                 |               |        |

|           |              |         |        | 255       | 25.5mA        | 19.1mA          | 12.7mA        | 6.3mA  |

Table 12. LED\_Current2 Register

|     | Addr: 11h    |         | LED_Current2 Register      |     |             |                  |               |        |  |  |

|-----|--------------|---------|----------------------------|-----|-------------|------------------|---------------|--------|--|--|

| Bit | Bit Name     | Default | Default Access Description |     |             |                  |               |        |  |  |

|     |              |         |                            |     | Sets the cu | irrent for curre | ent source on | LED2   |  |  |

|     |              |         |                            |     |             | LED2             | _max          |        |  |  |

|     |              |         | R/W                        |     | 00          | 01               | 10            | 11     |  |  |

| 7:0 | LED_current2 | 00h     |                            | 0   |             | Current s        | source off    |        |  |  |

|     |              |         |                            | 1   | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |  |  |

|     |              |         |                            |     |             |                  |               |        |  |  |

| 26  |              |         |                            | 255 | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |  |  |

Table 13. LED\_Current3 Register

|     | Addr: 12h    | LED_Current3 Register |        |             |             |                  |               |        |  |

|-----|--------------|-----------------------|--------|-------------|-------------|------------------|---------------|--------|--|

| Bit | Bit Name     | Default               | Access | Description |             |                  |               |        |  |

|     |              |                       |        |             | Sets the cu | urrent for curre | ent source on | LED3   |  |

|     |              |                       |        |             |             | LED3             | _max          |        |  |

|     |              |                       |        |             | 00          | 01               | 10            | 11     |  |

| 7:0 | LED_current3 | 00h                   | R/W    | 0           |             | Current s        | source off    |        |  |

|     |              |                       |        | 1           | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |  |

|     |              |                       |        |             |             |                  |               |        |  |

|     |              |                       |        | 255         | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |  |

Table 14. LED\_Current4 Register

|     | Addr: 13h    | LED_Current4 Register |        |             |             |                  |               |        |  |

|-----|--------------|-----------------------|--------|-------------|-------------|------------------|---------------|--------|--|

| Bit | Bit Name     | Default               | Access | Description |             |                  |               |        |  |

|     |              |                       |        |             | Sets the cu | irrent for curre | ent source on | LED4   |  |

|     |              |                       |        |             |             | LED4             | _max          |        |  |

|     |              |                       | 1      |             | 00          | 01               | 10            | 11     |  |

| 7:0 | LED_current4 | 00h                   | R/W    | 0           |             | Current          | source off    |        |  |

|     |              |                       |        | 1           | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |  |

|     |              |                       |        |             |             |                  |               |        |  |

|     |              |                       |        | 255         | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |  |

Table 15. LED\_Current5 Register

|     | Addr: 14h    |         |        |     | LED_Curre   | ent5 Register    |               |        |

|-----|--------------|---------|--------|-----|-------------|------------------|---------------|--------|

| Bit | Bit Name     | Default | Access |     |             | Descript         | ion           |        |

|     |              |         |        |     | Sets the cu | irrent for curre | ent source on | LED5   |

|     |              |         |        |     |             | LED5             | _max          |        |

|     |              |         |        |     | 00          | 01               | 10            | 11     |

| 7:0 | LED_current5 | 00h     | R/W    | 0   |             | Current s        | source off    |        |

|     | <b>♦,</b> (C |         |        | 1   | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |

|     |              |         |        |     |             |                  |               |        |

|     |              |         |        | 255 | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |

Table 16. LED\_Current6 Register

|     | Addr: 15h    |         | LED_Current6 Register |             |                  |               |            |        |  |  |

|-----|--------------|---------|-----------------------|-------------|------------------|---------------|------------|--------|--|--|

| Bit | Bit Name     | Default | Access                | Description |                  |               |            |        |  |  |

|     |              |         |                       | Sets the cu | urrent for curre | ent source on | LED6       |        |  |  |

|     |              |         |                       |             |                  | LED6          | S_max      |        |  |  |

|     |              |         |                       |             | 00               | 01            | 10         | 11     |  |  |

| 7:0 | LED_current6 | 00h     | R/W                   | 0           |                  | Current s     | source off |        |  |  |

|     |              |         |                       | 1           | 0.1mA            | 74.9µA        | 49.8µA     | 24.7µA |  |  |

|     |              |         |                       |             |                  |               |            |        |  |  |

|     |              |         |                       | 255         | 25.5mA           | 19.1mA        | 12.7mA     | 6.3mA  |  |  |

Table 17. LED\_Current7 Register

|     | Addr: 16h    | LED_Current7 Register |        |             |             |                  |               |        |

|-----|--------------|-----------------------|--------|-------------|-------------|------------------|---------------|--------|

| Bit | Bit Name     | Default               | Access | Description |             |                  |               |        |

|     |              |                       |        |             | Sets the cu | irrent for curre | ent source on | LED7   |

|     |              |                       |        |             |             | LED7             | _max          |        |

|     |              |                       | 1      |             | 00          | 01               | 10            | 11     |

| 7:0 | LED_current7 | 00h                   | R/W    | 0           |             | Current          | source off    |        |

|     |              |                       |        | 1           | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |

|     |              |                       |        |             |             |                  |               |        |

|     |              |                       |        | 255         | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |

Table 18. LED\_Current8 Register

| Addr: 17h |              |         |        | LED_Curr | ent8 Register | r                |               |        |

|-----------|--------------|---------|--------|----------|---------------|------------------|---------------|--------|

| Bit       | Bit Name     | Default | Access |          |               | Descript         | tion          |        |

|           |              |         |        |          | Sets the cu   | irrent for curre | ent source on | LED8   |

|           |              |         |        |          |               | LED8             | 3_max         |        |

|           |              |         |        |          | 00            | 01               | 10            | 11     |

| 7:0       | LED_current8 | 00h     | R/W    | 0        |               | Current s        | source off    |        |

|           | <b>♦,</b> (C |         |        | 1        | 0.1mA         | 74.9µA           | 49.8µA        | 24.7µA |

|           |              |         |        |          |               |                  |               |        |

|           |              |         |        | 255      | 25.5mA        | 19.1mA           | 12.7mA        | 6.3mA  |

Table 19. LED\_Current9 Register

|     | Addr: 18h    |         | LED_Current9 Register |             |             |                  |               |        |  |  |

|-----|--------------|---------|-----------------------|-------------|-------------|------------------|---------------|--------|--|--|

| Bit | Bit Name     | Default | Access                | Description |             |                  |               |        |  |  |

|     |              |         |                       |             | Sets the cu | urrent for curre | ent source on | LED9   |  |  |

|     |              |         |                       |             |             | LED9             | _max          |        |  |  |

|     |              |         |                       |             | 00          | 01               | 10            | 11     |  |  |

| 7:0 | LED_current9 | 00h     | R/W                   | 0           |             | Current s        | source off    |        |  |  |

|     |              |         |                       | 1           | 0.1mA       | 74.9µA           | 49.8µA        | 24.7µA |  |  |

|     |              |         |                       |             |             |                  |               |        |  |  |

|     |              |         |                       | 255         | 25.5mA      | 19.1mA           | 12.7mA        | 6.3mA  |  |  |

Table 20. LED MaxCurr1 Register

|     | Addr: 19h    |         |                    | LED_MaxCurr1 Register                                                             |    |

|-----|--------------|---------|--------------------|-----------------------------------------------------------------------------------|----|

| Bit | Bit Name     | Default | Access             | Description                                                                       |    |

|     |              |         |                    | Sets the maximum current for current source on LED1 (see LED_current1 on page 17) |    |

|     |              |         | 1                  | 00                                                                                |    |

| 1:0 | LED1_max     | 00b     | R/W                | 01   ILED1 = 019.1mA                                                              |    |

|     |              |         | 6                  |                                                                                   | 10 |

|     |              |         |                    | 11 ILED1 = 06.3mA                                                                 |    |

|     |              |         |                    | Sets the maximum current for current source on LED2 (see LED_current2 on page 17) |    |

|     |              |         |                    | 00   ILED2 = 025.5mA                                                              |    |

| 3:2 | LED2_max     | 00b     | R/W                | 01   ILED2 = 019.1mA                                                              |    |

|     |              |         |                    | 10 ILED2 = 012.7mA                                                                |    |

|     |              |         |                    | 11 ILED2 = 06.3mA                                                                 |    |

|     |              |         |                    | Sets the maximum current for current source on LED3 (see LED_current3 on page 18) |    |

|     |              |         |                    | 00 ILED3 = 025.5mA                                                                |    |

| 5:4 | LED3_max     | 00b     | R/W                | 01   ILED3 = 019.1mA                                                              |    |

|     | •            |         |                    | 10 ILED3 = 012.7mA                                                                |    |

|     |              |         |                    | 11 ILED3 = 06.3mA                                                                 |    |

|     |              |         |                    | Sets the maximum current for current source on LED4 (see LED_current4 on page 18) |    |

|     |              |         |                    | 00 ILED4 = 025.5mA                                                                |    |

| 7:6 | LED4_max 00b | R/W     | 01 ILED4 = 019.1mA |                                                                                   |    |

|     |              |         |                    | 10 ILED4 = 012.7mA                                                                |    |

| KY  |              |         |                    | 11 ILED4 = 06.3mA                                                                 |    |

Table 21. LED\_MaxCurr2 Register

|     | Addr: 1Ah |         |        |             | LED_MaxCurr2 Register                                                           |  |

|-----|-----------|---------|--------|-------------|---------------------------------------------------------------------------------|--|

| Bit | Bit Name  | Default | Access | Description |                                                                                 |  |

|     |           |         |        | Se          | ts the maximum current for current source on LED5 (see LED_current5 on page 18) |  |

|     |           |         |        | 00          | ILED5 = 025.5mA                                                                 |  |

| 1:0 | LED5_max  | 00b     | R/W    | 01          | ILED5 = 019.1mA                                                                 |  |

|     |           |         |        | 10          | ILED5 = 012.7mA                                                                 |  |

|     |           |         |        | 11          | ILED5 = 06.3mA                                                                  |  |

|     |           |         |        | Se          | ts the maximum current for current source on LED6 (see LED_current6 on page 19) |  |

|     |           |         |        | 00          | ILED6 = 025.5mA                                                                 |  |

| 3:2 | LED6_max  | 00b     | R/W    | 01          | ILED6 = 019.1mA                                                                 |  |

|     |           |         |        | 10          | ILED6 = 012.7mA                                                                 |  |

|     |           |         |        | 11          | ILED6 = 06.3mA                                                                  |  |

|     |           |         |        | Se          | ts the maximum current for current source on LED7 (see LED_current7 on page 19) |  |

|     |           |         | ,      | 00          | ILED7 = 025.5mA                                                                 |  |

| 5:4 | LED7_max  | 00b     | R/W    | 01          | ILED7 = 019.1mA                                                                 |  |

|     |           |         |        | 10          | ILED7 = 012.7mA                                                                 |  |

|     |           |         |        | 11          | ILED7 = 06.3mA                                                                  |  |

|     |           |         |        | Se          | ts the maximum current for current source on LED8 (see LED_current8 on page 19) |  |

|     |           |         |        | 00          | ILED8 = 025.5mA                                                                 |  |

| 7:6 | LED8_max  | 00b     | R/W    | 01          | ILED8 = 019.1mA                                                                 |  |

|     |           |         |        | 10          | ILED8 = 012.7mA                                                                 |  |

|     |           |         | U      | 11          | ILED8 = 06.3mA                                                                  |  |

Table 22. LED\_MaxCurr3 Register

|     | Addr: 1Bh |         | LED_MaxCurr3 Register      |                                                                                   |                 |  |  |  |

|-----|-----------|---------|----------------------------|-----------------------------------------------------------------------------------|-----------------|--|--|--|

| Bit | Bit Name  | Default | Default Access Description |                                                                                   | Description     |  |  |  |

|     |           |         |                            | Sets the maximum current for current source on LED9 (see LED_current9 on page 20) |                 |  |  |  |

|     |           |         |                            | 00                                                                                | ILED9 = 025.5mA |  |  |  |

| 1:0 | LED9_max  | 00b     | R/W                        | 01                                                                                | ILED9 = 019.1mA |  |  |  |

|     |           |         |                            | 10                                                                                | ILED9 = 012.7mA |  |  |  |

|     |           |         |                            | 11                                                                                | ILED9 = 06.3mA  |  |  |  |

# PWM Data Input Registers

Table 23. PWM\_LED1, PWM\_LED2...PWM\_LED9, PWM\_GPO Registers

| Addr: 80h-89h |     |            | PWM_LED1, PWM_LED2PWM_LED9, PWM_GPO Register |        |                                      |  |

|---------------|-----|------------|----------------------------------------------|--------|--------------------------------------|--|

| Addr          | Bit | Name       | Default                                      | Access | Description                          |  |

|               |     |            | 001                                          | R/W    | PWM value for Current source on LED1 |  |

| 80h           | 7:0 | pwm_LED1   |                                              |        | 0 LED1 Off                           |  |

| 8011          | 7.0 | pwiii_LLD1 | 00h                                          |        |                                      |  |

|               |     |            |                                              |        | 255 LED1 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED2 |  |

| 81h           | 7:0 | pwm LED2   | 00h                                          | R/W    | 0 LED2 Off                           |  |

| 0111          | 7.0 | pwiii_LLD2 | 0011                                         | 1000   |                                      |  |

|               |     |            |                                              |        | 255 LED2 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED3 |  |

| 82h           | 7:0 | pwm_LED3   | 00h                                          | R/W    | 0 LED3 Off                           |  |

| 0211          | 7.0 | pwiii_LLD3 | 0011                                         | 17///  |                                      |  |

|               |     |            |                                              | 4      | 255 LED3 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED4 |  |

| 83h           | 7:0 | pwm LED4   | 00h                                          | R/W    | 0 LED4 Off                           |  |

| 0311          | 7:0 | pwiii_LED4 | oon                                          |        |                                      |  |

|               |     |            |                                              |        | 255 LED4 Full Scale                  |  |

|               | 7:0 | pwm_LED5   | 00h                                          | R/W    | PWM value for Current source on LED5 |  |

| 84h           |     |            |                                              |        | 0 LED5 Off                           |  |

|               |     |            |                                              |        | 255 LED5 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED6 |  |

| 056           | 7.0 | num LEDG   | 004                                          | R/W    | 0 LED6 Off                           |  |

| 85h           | 7:0 | pwm_LED6   | 00h                                          | R/VV   |                                      |  |

|               |     |            |                                              |        | 255 LED6 Full Scale                  |  |

|               |     | <b>*</b>   |                                              |        | PWM value for Current source on LED7 |  |

| 006           | 7.0 | pwm JEDZ   | 006                                          | DAA    | 0 LED7 Off                           |  |

| 86h           | 7:0 | pwm_LED7   | 00h                                          | R/W    |                                      |  |

|               |     |            |                                              |        | 255 LED7 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED8 |  |

| 87h           | 7:0 | num LED9   | 006                                          | R/W    | 0 LED8 Off                           |  |

| 0/11          | 7:0 | pwm_LED8   | 00h                                          | R/VV   |                                      |  |

|               |     |            |                                              | +      | 255 LED8 Full Scale                  |  |

|               |     |            |                                              |        | PWM value for Current source on LED9 |  |

| 906           | 7:0 | pwm_LED9   | 00h                                          | R/W    | 0 LED9 Off                           |  |

| 88h           |     |            |                                              |        |                                      |  |

|               |     |            |                                              |        | 255 LED9 Full Scale                  |  |

Table 23. PWM\_LED1, PWM\_LED2...PWM\_LED9, PWM\_GPO Registers (Continued)

| Addr: 80h-89h |                     |         | PWM_LED1, PWM_LED2PWM_LED9, PWM_GPO Register |                    |                                          |             |  |

|---------------|---------------------|---------|----------------------------------------------|--------------------|------------------------------------------|-------------|--|

| Addr          | Bit                 | Name    | Default                                      | Access             | Description                              |             |  |

|               |                     |         |                                              |                    | PWM value for GPO PWM generator (8 bits) |             |  |

| 90h           | 7:0                 | nwm GBO | 006                                          | DAA                | 0                                        | PWM GPO Off |  |

| 0911          | 89h 7:0 pwm_GPO 00h | UUII    | R/W                                          |                    |                                          |             |  |

|               |                     |         | 255                                          | PWM GPO Full Scale |                                          |             |  |

RGB Color correction, Fader and Logarithmic/Linear Registers

Table 24. LED\_Control2 Register

|     | Addr: 03h                   |         | LED_Control2 Register |                                                                                                              |  |  |  |  |

|-----|-----------------------------|---------|-----------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | Bit Name                    | Default | Access                | Description                                                                                                  |  |  |  |  |

|     |                             |         |                       | Temperature compensation operating mode                                                                      |  |  |  |  |

|     | . 1                         | 0       | D 444                 | 0 Normal Mode                                                                                                |  |  |  |  |

| 3   | temp_comp_mode <sup>1</sup> | 0       | R/W                   | Positive Values of correction: Normal operation Negative values of correction: correction value divided by 2 |  |  |  |  |

|     |                             |         |                       | Fader 1 linear / logarithmic control                                                                         |  |  |  |  |

| 4   | fader_loglin1               | 0       | R/W                   | 0 Linear Operation                                                                                           |  |  |  |  |

|     |                             |         | 5                     | 1 Logarithmic Operation                                                                                      |  |  |  |  |

|     |                             |         |                       | Fader 2 linear / logarithmic control                                                                         |  |  |  |  |

| 5   | fader_loglin2               | 0       | R/W                   | 0 Linear Operation                                                                                           |  |  |  |  |

|     |                             |         |                       | 1 Logarithmic Operation                                                                                      |  |  |  |  |

|     |                             |         |                       | Fader 3 linear / logarithmic control                                                                         |  |  |  |  |

| 6   | fader_loglin3               | 0       | R/W                   | 0 Linear Operation                                                                                           |  |  |  |  |

|     |                             |         |                       | 1 Logarithmic Operation                                                                                      |  |  |  |  |

<sup>1.</sup> Its safe to keep temp\_comp\_mode at default '0'

Table 25. Fader1, Fader2 and Fader3 Registers

|      | Addr: 9B-9Dh   |         |         | Fader1, Fader2 and Fader3 Register |     |                     |  |  |  |

|------|----------------|---------|---------|------------------------------------|-----|---------------------|--|--|--|

| Addr | Bit            | Name    | Default | Access                             |     | Description         |  |  |  |

|      |                |         |         |                                    |     | Global Fader1 value |  |  |  |

| OPh  | 7:0            | fader1  | 00h     | R/W                                | 0   | Off                 |  |  |  |

| 9011 | 9Bh 7:0 fader1 | lauei i | OUII    | R/VV                               |     |                     |  |  |  |

|      |                |         |         |                                    | 255 | Full Scale          |  |  |  |

|      |                |         |         |                                    |     | Global Fader2 value |  |  |  |

| 9Ch  | 7:0            | fader2  | 00h     | R/W                                | 0   | Off                 |  |  |  |

| 9011 | 7.0            |         |         |                                    |     |                     |  |  |  |

|      |                |         |         |                                    | 255 | Full Scale          |  |  |  |

Table 25. Fader1, Fader2 and Fader3 Registers (Continued)