CY8C20045, CY8C20055, CY8C20xx6, CY8C20xx6A, CY8C20xx6AS, CY8C20xx6AN, CY8C20xx6L, CY8C20xx6H, CY7C643xx, CY7C604xx, CY8CTST2xx, CY8CTMG2xx, CY8C20xx7, CY8C20xx7S, and CY8C20xx7AN

# **ISSP Programming Specification**

Document #: 001-57631 Rev. \*H

**December 18, 2012**

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### License

© 2009-2012 Cypress Semiconductor Corporation. All rights reserved. This software, and associated documentation or materials (Materials) belong to Cypress Semiconductor Corporation (Cypress) and may be protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Unless otherwise specified in a separate license agreement between you and Cypress, you agree to treat Materials like any other copyrighted item.

You agree to treat Materials as confidential and will not disclose or use Materials without written authorization by Cypress. You agree to comply with any Nondisclosure Agreements between you and Cypress.

If Material includes items that may be subject to third party license, you agree to comply with such licenses.

#### Copyrights

Copyright © 2007-2012 Cypress Semiconductor Corporation. All rights reserved.

PSoC®, CapSense®, and TrueTouch® are registered trademarks and PSoC Designer™ is a trademark of Cypress Semiconductor Corporation (Cypress), along with Cypress® and Cypress Semiconductor™. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Purchase of I<sup>2</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress. Made in the U.S.A.

## **Disclaimer**

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

## Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress Data Sheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Contents

| 1. | Over | view                                                         | 5  |

|----|------|--------------------------------------------------------------|----|

|    | 1.1  | Introduction                                                 | 5  |

|    | 1.2  | Host Programmer - CY8C20xx6A Programming Interface           |    |

|    |      | 1.2.1 Programming Pin Drive Modes                            |    |

|    | Docu | ument Revision History                                       | 7  |

| 2. | Prog | ramming Flow                                                 | 9  |

|    | 2.1  | Target Programming                                           | 9  |

|    |      | 2.1.1 Vectors                                                | 9  |

|    |      | 2.1.2 Clocking                                               | 10 |

|    |      | 2.1.3 Command Format                                         | 10 |

|    |      | 2.1.4 Wait-and-Poll                                          | 10 |

|    |      | 2.1.5 Programming Pin Drive Modes                            | 11 |

|    | 2.2  | Insertion Check                                              | 11 |

|    | 2.3  | Verify Silicon ID                                            | 12 |

|    |      | 2.3.1 Reset Mode                                             | 13 |

|    |      | 2.3.2 Power-on Mode                                          | 13 |

|    |      | 2.3.3 Power-on Mode with External Supply                     | 14 |

|    |      | 2.3.4 Read-ID-Word                                           |    |

|    | 2.4  | Rerun Check (Optional)                                       |    |

|    | 2.5  | Erase                                                        |    |

|    | 2.6  | Program and Verify                                           |    |

|    | 2.7  | Set Security                                                 |    |

|    | 2.8  | Verify Security (Optional)                                   |    |

|    | 2.9  | Device Checksum                                              |    |

|    | 2.10 | Power Down                                                   |    |

|    |      | Verify (Optional)                                            |    |

|    |      | Specifications and Definitions                               |    |

|    |      | 2.12.1 DC Programming Specifications                         |    |

|    |      | 2.12.2 AC Programming Specifications                         |    |

|    |      | 2.12.3 Device Address and Block Definitions                  |    |

|    | D    |                                                              |    |

| Α. | _    | ramming Mnemonics for CY8C20xx6, CY8C20xx7, 643xx, CY7C604xx | 23 |

|    | Д 1  | Bit Streams for Mnemonics                                    | 23 |

## 1. Overview

## 1.1 Introduction

In-circuit programming is convenient for prototyping, manufacturing, and in-system field updates. CY8C20045, CY8C20055, CY8C20xx6A, and CY8C20xx7 devices can be programmed using the in-system serial programming (ISSP) protocol, a proprietary protocol used by Cypress.

This reference manual provides the information developers and programmer vendors need to create their own in-system programming solutions for CY8C20045, CY8C20055, CY8C20xx6A, and CY8C20xx7 devices. The following topics are covered in this document:

- Information on how to interface a host programmer with CY8C20045, CY8C20055, CY8C20xx6A, and CY8C20xx7 devices

- Description of the ISSP protocol

- AC/DC programming specifications

- Programming vectors

- Introduction to the Intel hex file format

The programming procedure involves a programmer and a target device. The programmer communicates serially with the target, supplies the clocking, and sends commands to the target. The target receives data from the programmer and supplies data upon a read request. It only drives the data line when it receives a request from the programmer. The programmer programs the target with the program image contained in the *PROJECT NAME>.hex* file, which is generated by PSoC Designer<sup>TM</sup>.

Keep the following things in mind when you are developing a host programming application:

- The programming vectors provided in this document should not be compared with those generated by the MiniProg1, MiniProg3, or ICE-Cube. MiniProg1, MiniProg3, and ICE-Cube use a different version of the protocol to program the target device. Cypress recommends using the programming vectors provided in this document to develop your host side interface and program CY8C20045, CY8C20055, CY8C20xx6A, and CY8C20xx7 devices.

- Even though the ISSP protocol uses a bidirectional data line for communication between a host and a target device, it is not related to the I<sup>2</sup>C protocol.

## 1.2 Host Programmer - CY8C20xx6A Programming Interface

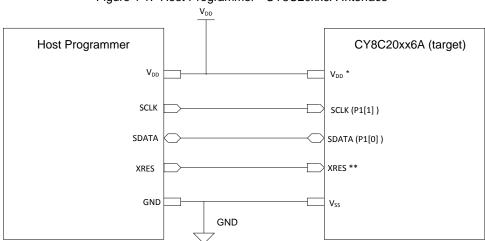

Figure 1-1 shows the connections between the host programmer and the target CY8C20xx6A device. If you are using the MiniProg1 programmer, refer to the Knowledge Base article, *Part Number for MiniProg1 Target Connector, 5-pin ISSP Header in MiniProg3*, for details.

Figure 1-1. Host Programmer - CY8C20xx6A Interface

\* To program in Power Cycle mode, the host programmer must be capable of toggling power to the CY8C20xx6A device.

## 1.2.1 Programming Pin Drive Modes

The electrical pin connections between the programmer and the target device shown in Figure 1-1 are listed in Table 1-1. This includes two signal pins, a reset pin, a power pin, and a ground pin. Leave the other pins floating. The pin naming conventions and drive strength requirements are also listed in Table 1-1.

Table 1-1. Pin Names and Drive Strengths

| Pin Name        | Function                       | Programmer HW Pin Requirements                      | CY8C20xx6A Drive mode behavior                                                                                                       |

|-----------------|--------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P1[0]           | SDATA – Serial data in/out     | Drive TTL Levels, Read TTL, High-Z                  | Strong drive (while sending data to the host), Resistive pull-down mode (reading data from the host, waiting for data from the host) |

| P1[1]           | SCLK – Serial clock            | Drive TTL Levels                                    | High-Z digital input                                                                                                                 |

| XRES            | Reset                          | Drive TTL Levels. Active High                       | Active high reset input with internal resistive pull down                                                                            |

| V <sub>SS</sub> | Power supply ground connection | Low Resistance Ground Connection                    | Ground connection                                                                                                                    |

| V <sub>DD</sub> | Positive power supply voltage  | 0 V, 1.8 V, 3.3 V, 5 V. 20 mA Current<br>Capability | Supply voltage                                                                                                                       |

The CY8C20xx6A SDATA pin drive modes vary during programming. When CY8C20xx6A drives the SDATA line to indicate that it has started up completely or to send data back to the host, it is in a strong drive configuration. When CY8C20xx6A waits for data or receives data from the host, SDATA is in a resistive pull-down configuration. It is important to design the host external pin drive mode circuitry to detect a strong high to resistive low transition, and to be able to drive the SDATA pin both high and low when it is in resistive pull down mode. Because the SDATA line has a internal pull-down resistor (5.6 k $\Omega$ ), external pull-up resistors can cause the host to miss high-to-low transitions on the target device due to resistive voltage divider. Therefore, using external pull-up resistors on the SDATA line is not recommended.

<sup>\*\*</sup> XRES pin in CY8C20xx6A is active high input. It has an internal pull-down resistor to keep it at logic low when left floating. XRES pin is not available in all device packages. Check the device data sheet for information on XRES pin availability. Use Power Cycle mode if XRES is not available.

## **Document Revision History**

**Document Title:** CY8C20xx6, CY8C20xx6A, CY8C20xx6AS, CY8C20xx6AN, CY8C20xx6L, CY8C20xx6H, CY7C643xx, CY7C604xx, CY8CTST2xx, CY8CTMG2xx, CY8C20xx7, CY8C20xx7S, and CY8C20xx7AN ISSP Programming Specifications

**Document Number: 001-57631**

| Revision | Issue Date | Origin of<br>Change | Description of Change                                                                                                               |

|----------|------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| **       | 11/18/2009 | VZD                 | Initial revision                                                                                                                    |

|          |            |                     | 1. Added AN2026c to title                                                                                                           |

|          |            |                     | Updated WAIT-AND-POLL diagram (Figure 11) and changed description.     changed to match Programming Spec.                           |

| *A       |            |                     | 3. Added SYNC-ENABLE to Program and Verify Procedure Flowchart (Figure 5) to match Programming Spec.                                |

|          |            |                     | 4. Updated DC Specs table to match Programming Spec.                                                                                |

|          |            |                     | 5. Added support for TMG2xx and TST2xx families.                                                                                    |

|          |            |                     | 6. Removed values from Figure 13and Figure 14                                                                                       |

|          |            |                     | Added support to CY7C643xx and CY7C604xx devices:                                                                                   |

|          |            |                     | Updated table-4 device address and block definition. Updated table-5 programming vectors.                                           |

| *B       | 11/25/2010 | /25/2010 KPOL       | Added support to CY8C20746A,CY8C20766A: Updated table-4 device address and block definition.                                        |

|          |            |                     | Updated table-5 programming vectors. Updated min timing value of TXRES and TVDDXRES in AC Programming Specifications.               |

|          |            |                     | Updated WAIT-AND-POLL Sequence Timing.                                                                                              |

|          |            |                     | Added note providing reference to the knowledge base article in Appendix A.                                                         |

| *C       | 12/15/2010 | KPOL                | Post to external web                                                                                                                |

| *D       | 03/24/2011 | KPOL                | Updated read-id word vectors; read-byte vector picture and description                                                              |

| *E       | 08/31/2011 | DALE                | Added programming vectors for TrueTouch parts                                                                                       |

| *F       | 11/23/2011 | KPOL                | Converted to TRM category. Removed reference to CY8C20xx6, CY7C543xx, and CY7C604xx parts. Content updates throughout the document. |

|          |            |                     | Replaced Appendix A with content of Appendix 2 in Spec #001-15870                                                                   |

|          |            |                     | Updated title                                                                                                                       |

|          | 03/20/2012 | 3/20/2012 VMAD      | In Section 2.1.4, replaced "must apply a bit stream of 40 zero bits" with "must apply a bit stream of 30 zero bits"                 |

| *G       |            |                     | Replaced Figure 2-4 with Figure 1 of Spec #001-15870                                                                                |

|          |            |                     | Matched data in Table 2-1 with table in 8.3.2 of Spec #001-15870                                                                    |

|          |            |                     | Matched data in Table 2-2 with table in 8.3.3 of Spec #001-15870                                                                    |

|          |            |                     | Replaced Table 2-3 with Table 7 of Spec #001-15870                                                                                  |

| *H       | 12/18/2012 | ZINE                | Added references to CY8C20045 and CY8C20055                                                                                         |

# 2. Programming Flow

## 2.1 Target Programming

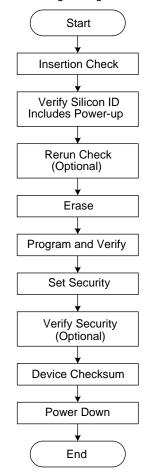

For successful target programming, follow the programming flow in Figure 2-1. Each procedure is explained in detail in the following sections. Failure to complete these steps can result in incorrectly programmed flash.

Figure 2-1. Target Programming Flow

## 2.1.1 Vectors

Vectors are the binary representation of the commands necessary to perform various operations involved in the programming flow. Each procedure in the programming flow has many individual vectors associated with it; see Bit Streams for Mnemonics. Each vector is 22 bits long and any number of zeros can be sent between sequential vectors. The target ignores the zero padding and any subsequent '0' on the SDATA line. This continues until the target receives a '1', which is the first bit in the next vector in the vector-set.

## 2.1.2 Clocking

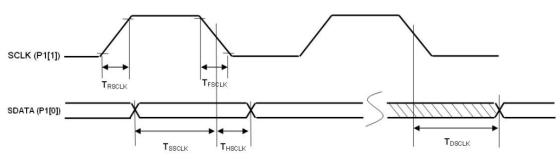

The host programmer always writes and reads on the rising edge of SCLK, while the target writes and reads on the falling edge. Figure 2-2 shows the timing waveforms of the SCLK lines. Table 2-2 provides the timing specifications mentioned in Figure 2-2. During the programming flow, the programmer supplies a clock on the SCLK to transfer data. This data transfer mode is used while the programmer

communicates with the target, either by sending or receiving data. During this time, the programmer can drive the SCLK signal at any frequency that enables reliable data transfer with a maximum transmit frequency of 8 MHz (see F<sub>SCLK</sub> in Table 2-2). The frequency of SCLK does not need to be accurate or consistent, as long as it is less than the 8 MHz limit. Clocks are not allowed during the Wait-and-Poll steps described in the procedure flowcharts.

Figure 2-2. SCLK Timing Diagram

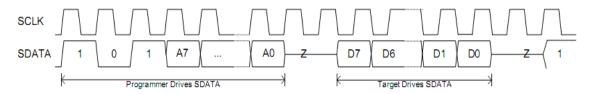

#### 2.1.3 Command Format

During programming, only the programmer drives the SCLK line. The programmer and the target can drive the SDATA line, although the target drives SDATA only upon a read request from the programmer. The programmer always writes and reads SDATA on the rising edge of SCLK, while the target writes and reads on the falling edge. After the programmer requests a read from the target, it releases the SDATA line to a high-Z state. It resumes driving the SDATA line only after the byte is sent by the target. The programmer supplies clocks even when it has released (high-Z) the SDATA line.

During the Wait-and-Poll procedure, the programmer releases (high-Z) the SDATA line and waits for a high-to-low transition on SDATA. Clocks are not allowed during the Wait-and-Poll phase. Figure 2-3 shows the Read Byte Vector Waveform.

**Note** The programmer must change SDATA on the positive edge of SCLK to allow enough time for the target to clock in data on the negative edge of SCLK. The programmer must show resistive drive to ground and strong drive to VDD during reads.

The programmer clocks two high-Zs between the address and data bits. When the target drives the SDATA line, the device changes SDATA on the negative edge of SCLK. The data must be read on SDATA greater than T<sub>DSCLK</sub> from the falling edge (see AC Programming Specifications).

#### 2.1.4 Wait-and-Poll

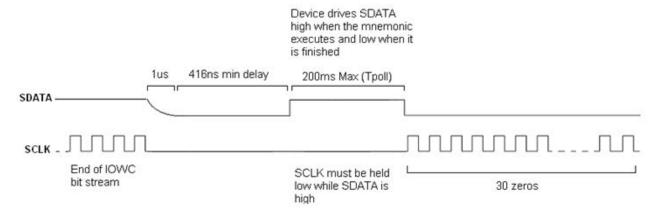

After a mnemonic bit stream is sent, the SDATA line takes 1  $\mu s$  to drift low (SDATA line drifts low to  $V_{ILP}$  by the device's internal pull-down resistor). Clocking is needed before SDATA transitions from low to high. The target device pulls SDATA high while executing the mnemonic it received from the host programmer. A minimum delay of 416 ns is needed for the execution to begin. The device outputs logic high on the SDATA pin while the mnemonic is executing and switches to a logic low when the mnemonic finishes. The programmer must wait and poll the SDATA pin for the high to low transition. The maximum SDATA high time is 200 ms; see  $T_{POLL}$  from Table 2-2.

When the transition to low is observed on the SDATA line, the programmer must apply a bit stream of 30 zero bits to the SDATA pin of the device and then continue to the next mnemonic. This is shown in Figure 2-4.

**Note** The device drives SDATA high when the mnemonic executes and low when it is finished.

Figure 2-3. Read Byte (D7...D0) from Target CY8C20xx6A (at address A7...A0)

Figure 2-4. Wait-and-Poll Timing Diagram

## 2.1.5 Programming Pin Drive Modes

The pin drive modes vary during programming operation. When CY8C20xx6A drives the SDATA line to indicate that it has started up completely or to send data back to the host, SDATA is in a strong drive configuration. When it waits for or receives data, SDATA is in a pull-down configuration. Design the external pin drive mode circuitry so that a strong high to resistive low transition can be detected and the pin is driven both high and low when it is in pull-down mode.

## 2.2 Insertion Check

The programmer should test the physical orientation of the device before applying  $V_{DD}$ . The insertion check ensures that  $V_{DD}$  and GND of the device are correctly oriented in the socket or on the board. The programmer should execute a pin continuity test to verify electrical connection to all the required port pins listed in Table 1-1. The port pins have an industry standard reverse bias diode that can be used for the continuity test.

## 2.3 Verify Silicon ID

The Verify Silicon ID procedure places the chip in programming mode and reads the silicon ID of that chip. If the silicon ID does not match the expected value, the programmer must abort the programming process and send an error message to the device programmer's operator. The Verify Silicon ID procedure must be the first procedure in the flow after the insertion check and cannot be bypassed.

The programming mode is entered by the reset mode or power-on mode. If there is no XRES pin on the device, use the power-on mode. Note that because the power-on mode involves cycling power to the target, in-circuit field programming may require PCB layout considerations. If the XRES method is used, make sure that any external circuitry connected to XRES on the target board does not interfere with timing.

Figure 2-5. Verify Silicon ID Procedure Verify Silicon ID Reset mode Power on mode Power on or Reset mode? Assert V<sub>DD</sub> Assert V<sub>DD</sub> Wait for NO Wait for at least Is XRES Applied  $\mathsf{T}_{\mathsf{VDDWAIT}}$ T<sub>VDDXRES</sub> (2.47ms) with  $V_{DD}$ ? YES WAIT-AND-POLL Assert XRES for at Assert XRES for at least least 263µs T<sub>VDDXRES</sub> (2.47ms) Wait 0.5µs following Wait 0.5µs following the de-assertion of the de-assertion of **XRES XRES** ID-SETUP-1 WAIT-AND-POLL ID-SETUP-2 WAIT-AND-POLL SYNC-ENABLE **READ-ID-WORD**

SYNC-DISABLE

Is Silicon ID Correct?

YES

End Verify

Silicon ID

NO

Programming

Failed

#### 2.3.1 Reset Mode

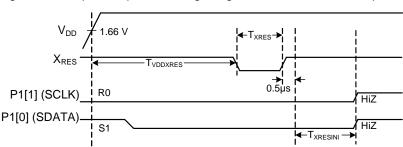

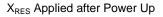

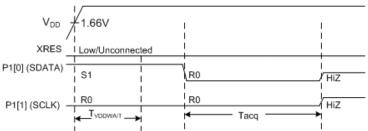

Figure 2-6 shows the timing to enter programming mode with reset. To initialize the part using the XRES line, wait until  $V_{DD}$  is stable, then wait for  $T_{VDDXRES}$  time and assert the XRES line for the time specified by  $T_{XRES}$  (see Table 2-2). The XRES line may also be brought up with the power supply line, in which case, XRES must be held high for at least  $T_{VDDXRES}$ . After XRES is driven low, there is a window of time specified by  $T_{XRESACQ}$ , (see Table 2-2), in which the first nine bits of the ID-SETUP-1 vector-set must be transmitted.

While the target executes the ID-SETUP-1 mnemonic, it drives the SDATA line high. The programmer must wait and poll the SDATA line for a high-to-low transition, which is the signal from the target that the ID-SETUP-1 mnemonic is complete.

After the ID-SETUP-1 mnemonic, send the ID-SETUP-2 mnemonic, and then wait and poll. Next, send the SYNC-ENABLE, READ-ID-WORD, and SYNC-DISABLE mnemonics. See Bit Streams for Mnemonics for mnemonic bit streams.

Figure 2-6. Acquire Sequence Timing using XRES External Reset Acquire

X<sub>RES</sub> Applied at Power Up

### **Notes**

- R0 = Resistive logic '0' output

- HIZ = High-impedance with logic input disabled

- T<sub>VDDXRES</sub> and T<sub>XRES</sub> are the minimum amount of time required. Additional delay may be used without penalty

- There is a minimum required delay of 0.5 µs between the deassertion of the XRES and the entry of the first vector

- S1 = Strong logic '1' output from the target

#### 2.3.2 Power-on Mode

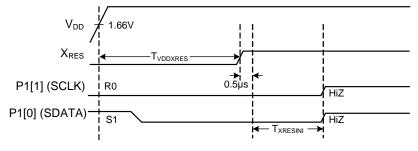

To initiate communication with the target using power-on mode, apply  $V_{DD}$  to the target, as shown in Figure 2-7. The target drives the SDATA line high. The programmer then waits and polls for a high-to-low transition on the SDATA line, which is the signal from the target that  $V_{DD}$  has stabilized. Note that until  $V_{DD}$  stabilizes, the SDATA signal is noisy and a false edge can be detected. As a result, the programmer must wait for the time specified by  $T_{VDDWAIT}$  (Table 2-2) before beginning to wait and poll. The programmer must also not drive the SCLK signal until the  $T_{VDDWAIT}$  time period has passed.

Figure 2-7. Acquire Sequence Timing using VDD Power-on Mode Acquire

#### Notes

- R0 = Resistive logic '0' output

- HIZ = High-impedance with logic Input disabled

- S1 = Strong logic '1' output from the target

- The programmer must wait for the time specified by T<sub>VDDWAIT</sub> before beginning to wait and poll for a S1 to R0 transition

After the SDATA transition is detected, the programmer must transmit the ID-SETUP-1 vectors in  $T_{ACQ}$  seconds (see Table 2-2) and wait and poll for a high-to-low transition on SDATA.

After the ID-SETUP-1 mnemonic, send the ID-SETUP-2 mnemonic and wait and poll. Next, send the SYNC-ENABLE, READ-ID-WORD, and SYNC-DISABLE mnemonics. See Bit Streams for Mnemonics for mnemonic bit streams.

During the power cycle phase of the Initialize Target procedure,  $V_{DD}$  must be the only pin asserted. XRES must be low. The internal pull-down resistor of the CY8C20xx6A on XRES achieves this if the pin is left floating externally.

# 2.3.3 Power-on Mode with External Supply

Acquiring the device through the power-on mode is possible even if the device uses an external power supply. Be careful with the timing and voltage levels of the device and power supply. This is because the programmer does not have control over the power supply in this case.

The programmer must be able to detect the supply voltage to determine when the supply has reached the minimum programming level and nominal supply voltage (for example, 1.8 V, 3.3 V, or 5 V). As shown in Figure 2-7, the programming sequence timing is initiated when the supply voltage reaches 1.66 V (±3%). At this point, the programmer must wait for some time before starting the Wait-and-Poll procedure. As shown in Table 2-1, the high and low signal thresholds (VILP, VIHP) are dictated by the power supply level of the target. Note that it is possible to use 3.3 V signal levels even if the target is powered by a 5 V supply. However, it is not possible to use 3.3 V signal levels if the target is powered by a 1.8 V supply.

A particular area of concern is the power supply ramp rate of the target. For an extremely slow ramp rate (< 0.5 V/ms), it is possible that the supply voltage may not reach the nominal voltage before the programming mode acquisition window closes. In this case, the programmer should specify a minimum supply ramp rate or develop an intelligent way to track the supply voltage and dynamically change the signal levels to match the supply voltage.

#### 2.3.4 Read-ID-Word

The silicon ID value is read back using the READ-ID-WORD vector-set. The first two bytes read back from the device for a READ-ID-WORD vector contain the silicon ID. The vectors in Bit Streams for Mnemonics under READ-ID-WORD show the device-specific values read from the target. For example, a LLLLLLL, HLLHHLHL denotes a 0x009A hex read back from a CY8C20066. The programmer must compare the value in the READ-ID-VECTOR and the value returned by the target. If these values do not match, the programmer must terminate the programming flow.

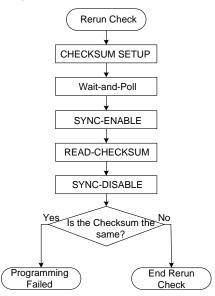

## 2.4 Rerun Check (Optional)

The Rerun Check procedure compares the device flash checksum with the hex file to see if the chip is previously programmed. When this feature is enabled, the chip inside a socket fails when it is programmed a second time. The rerun check is an optional feature for production programmers connected to a handler.

The rerun check is accomplished by the sequence shown in Figure 2-8. The CHECKSUM-SETUP, SYNC-ENABLE, READ-CHECKSUM, and SYNC-DISABLE bit streams are shown in Bit Streams for Mnemonics. See Wait-and-Poll for detailed timing information.

Figure 2-8. Rerun Check Procedure

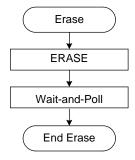

## 2.5 Erase

The Erase procedure erases the entire flash memory and security data (all set to zero). Erase is accomplished by sending the ERASE vector followed by the Wait-and-Poll procedure (see Figure 2-9).

Figure 2-9. Erase Procedure

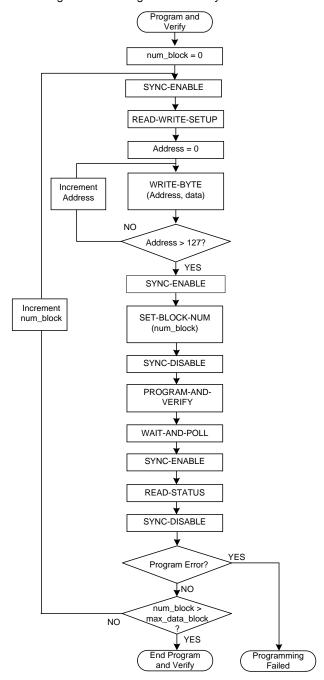

## 2.6 Program and Verify

The Program and Verify procedure programs the flash with the contents of the user's programming file. The READ-STA-TUS vector is used to determine the pass/fail success of the PROGRAM-AND-VERIFY vector. A programming failure results in a 0x04 value and a pass results in a 0x00 value. Figure 2-10 shows the sequence for the Program and Verify procedure.

Figure 2-10. Program and Verify Procedure

## 2.7 Set Security

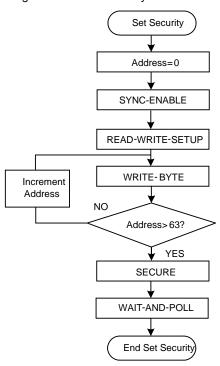

The Set Security procedure is performed after the device is successfully programmed. The SECURE mnemonic protects certain flash blocks from being read or changed. The security data for each block is located at the end of the hex file; see Bit Streams for Mnemonics for format details. The Set Security procedure is shown in Figure 2-11.

Figure 2-11. Set Security Procedure

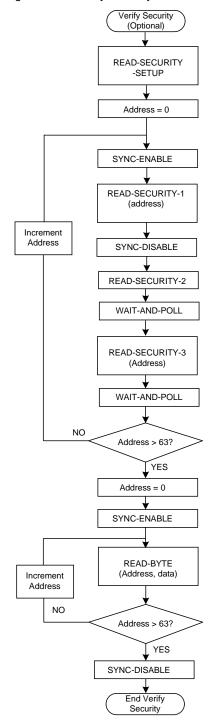

## 2.8 Verify Security (Optional)

In the optional Verify Security procedure, the programmer reads the security data from the chip and stores it in the memory. This data is compared with the programming file or the security data used in the Set Security step. The Verify Security procedure is shown in Figure 2-12.

Figure 2-12. Verify Security Procedure

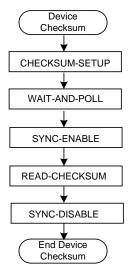

## 2.9 Device Checksum

In the Device Checksum procedure, the checksum is retrieved from the device and compared to the device checksum set in the target file. Note that the device checksum is not the same as the 'record checksum'. The Device Checksum procedure is shown in Figure 2-13.

Figure 2-13. Device Checksum Procedure

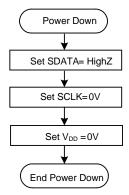

## 2.10 Power Down

The last step in the programming data flow is to power down the device. Power down is accomplished by the sequence shown in Figure 2-14.

Figure 2-14. Power Down Procedure

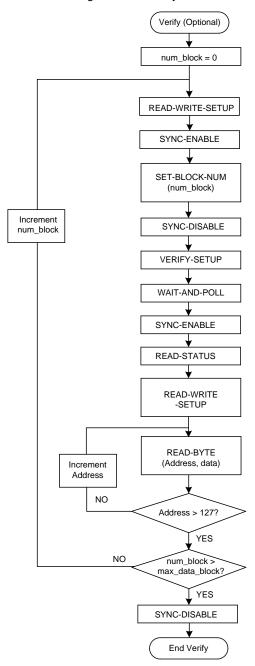

## 2.11 Verify (Optional)

The Verify procedure reads data from the device's flash so that it can be compared to the programming file. The READ-STATUS vector is used to determine whether the block is protected. The READ-STATUS vector returns a 0x01 for a secured block and the actual data read from that block is

invalid. In the case of a secured block, the programmer should display 'XX' for the data in the block.

Note that the Program and Verify procedure already performs a verify check between the flash and programming file. Therefore, it is not necessary to perform the optional Verify procedure. The max\_data\_block value for each device is listed in Table 2-3. The Verify procedure is shown in Figure 2-15.

Figure 2-15. Verify Procedure

#### **Specifications and Definitions** 2.12

#### 2.12.1 **DC Programming Specifications**

Note These specifications are from the CY8C20xx6A datasheet. To view the complete data sheet visit the Cypress web site.

Table 2-1. DC Programming Specifications

| DC Programming Specifications                                                                                 | Minimum                  | Typical   | <b>M</b> aximum <sup>a</sup> | <b>M</b> aximum <sup>b</sup> |

|---------------------------------------------------------------------------------------------------------------|--------------------------|-----------|------------------------------|------------------------------|

| V <sub>DDP</sub> (V <sub>DD</sub> for programming and erase)                                                  | 1.71 V                   | 3.3 V     | 5.5 V                        | 5.25 V                       |

| I <sub>DDP</sub> (Supply current during programming or verify)                                                | _                        | 5.0 mA    | 25 mA                        | 25 mA                        |

| $V_{ILP}$ (Input low voltage during programming or verify) $V_{DDP} \ge 2.6 \text{ V}$                        | -0.3 V                   | 0 V       | 0.8 V                        | 0.8 V                        |

| V <sub>IHP</sub> (Input high voltage during programming or verify)                                            | 1.71 V                   | $V_{DDP}$ | V <sub>DDP</sub> + 0.3 V     | V <sub>DDP</sub> + 0.3 V     |

| $I_{\rm ILP}$ (Input current when applying $V_{\rm ILP}$ to P1[0] or P1[1] during programming or verify)      | _                        | 1         | 0.2 mA                       | 0.2 mA                       |

| $I_{\mathrm{IHP}}$ (Input current when applying $V_{\mathrm{IHP}}$ to Port Pins during programming or verify) | _                        | 1         | 1.5 mA                       | 1.5 mA                       |

| V <sub>OLP</sub> (Output low voltage during programming or verify, I <sub>OL</sub> = 0.1 mA)                  | _                        | -         | V <sub>SS</sub> + 0.75 V     | V <sub>SS</sub> + 0.75 V     |

| V <sub>OHP</sub> (Output high voltage during programming or verify I <sub>OH</sub> =5 mA)                     | V <sub>DDP</sub> – 0.9 V | -         | $V_{DDP}$                    | $V_{DDP}$                    |

a. Maximum for Silicon Rev B3 Devices

#### **AC Programming Specifications** 2.12.2

Table 2-2. AC Programming Specifications

| AC Programming Specifications                                                                                     | Minimum  | Maximum               |

|-------------------------------------------------------------------------------------------------------------------|----------|-----------------------|

| T <sub>XRES</sub> (XRES pulse length <sup>[a]</sup> )                                                             | 300 µs   | _                     |

| T <sub>VDDWAIT</sub> (V <sub>DD</sub> stable to Wait-and-Poll hold off <sup>[b]</sup> )                           | 0.1 ms   | 1 ms                  |

| T <sub>VDDXRES</sub> (V <sub>DD</sub> stable to XRES assertion delay)                                             | 14.27 ms | _                     |

| T <sub>POLL</sub> (SDATA high pulse time <sup>[c]</sup> )                                                         | 10 µs    | 200 ms                |

| T <sub>ACQ</sub> ("Key window" time after a V <sub>DD</sub> ramp acquire event, based on 256 ILO clocks. [d],[e]) | 3.2 ms   | 19.6 ms               |

| T <sub>XRESACQ</sub> ("Key window" time after an XRES event, based on 8 ILO clocks. <sup>[e])</sup>               | 98 µs    | 615 µs                |

| T <sub>RSCLK</sub> (Rise time of SCLK)                                                                            | 1 ns     | 20 ns                 |

| T <sub>FSCLK</sub> (Fall time of SCLK)                                                                            | 1 ns     | 20 ns                 |

| T <sub>SSCLK</sub> (Data setup time to falling edge of SCLK)                                                      | 40 ns    | _                     |

| T <sub>HSCLK</sub> (Data hold time from falling edge of SCLK)                                                     | 40 ns    | _                     |

| F <sub>SCLK</sub> (Frequency of SCLK)                                                                             | _        | 8 MHz <sup>[f]</sup>  |

| T <sub>DSCLK</sub> (Data-out delay from falling edge of SCLK (3.6 V < V <sub>DD</sub> )                           | _        | 60 ns <sup>[f]</sup>  |

| $T_{DSCLK3}$ (Data-out delay from falling edge of SCLK (3.0 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V)                | _        | 85 ns <sup>[f]</sup>  |

| $T_{DSCLK2}$ (Data-out delay from falling edge of SCLK (1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.0 V)               | _        | 130 ns <sup>[f]</sup> |

Maximum for Silicon Rev E1 Devices

a. See Figure 2-6. Times longer than T<sub>XRES</sub> may be used without consequence.

b. Until V<sub>DD</sub> stabilizes, SDATA is noisy and the falling edge should not be searched for. For this reason, a delay of T<sub>VDDWAIT</sub> is necessary after V<sub>DD</sub> is applied

c. T<sub>POLL</sub> applies to the Wait-and-Poll procedure. SDATA remains high for the T<sub>POLL</sub> time.

d. The ID-SETUP-1 bit stream data must not be delayed more than T<sub>ACQ</sub> from the end of the Wait-and-Poll (measured from the falling edge of SDATA).

e. The "key window" is the length of time during which a specific bit sequence or "key" must be sent to the target device, on SDATA.

## 2.12.3 Device Address and Block Definitions

Table 2-3. Device Address and Block Definitions

| Device                | Address numbers for bytes within a block | Block numbers for program data | max_data_block |

|-----------------------|------------------------------------------|--------------------------------|----------------|

| CY7C60400             | 0-127                                    | 0-255                          | 255            |

| CY7C60413             | 0-127                                    | 0-63                           | 63             |

| CY7C60445             | 0-127                                    | 0-127                          | 127            |

| CY7C60455             | 0-127                                    | 0-127                          | 127            |

| CY7C60456             | 0-127                                    | 0-255                          | 255            |

| CY7C64300             | 0-127                                    | 0-255                          | 255            |

| CY7C64313             | 0-127                                    | 0-63                           | 63             |

| CY7C64315             | 0-127                                    | 0-127                          | 127            |

| CY7C64316             | 0-127                                    | 0-255                          | 255            |

| CY7C64343             | 0-127                                    | 0-63                           | 63             |

| CY7C64345             | 0-127                                    | 0-127                          | 127            |

| CY7C64355             | 0-127                                    | 0-127                          | 127            |

| CY7C64356             | 0-127                                    | 0-255                          | 255            |

| CY8C20045-24LKXI      | 0-127                                    | 0-63                           | 63             |

| CY8C20055-24LKXI      | 0-127                                    | 0-63                           | 63             |

| CY8C20055-24SXI       | 0-127                                    | 0-63                           | 63             |

| CY8C20066             | 0-127                                    | 0-255                          | 255            |

| *** CY8C20236-24LKXI  | 0-127                                    | 0-63                           | 63             |

| *** CY8C20246-24LKXI  | 0-127                                    | 0-127                          | 127            |

| *** CY8C20266-24LKXI  | 0-127                                    | 0-255                          | 255            |

| *** CY8C20336-24LQXI  | 0-127                                    | 0-63                           | 63             |

| CY8C20336H-24LQXI     | 0-127                                    | 0-63                           | 63             |

| *** CY8C20346-24LQXI  | 0-127                                    | 0-127                          | 127            |

| CY8C20346H-24LQXI     | 0-127                                    | 0-127                          | 127            |

| *** CY8C20366-24LQXI  | 0-127                                    | 0-255                          | 255            |

| *** CY8C20396-24LQXI  | 0-127                                    | 0-255                          | 255            |

| *** CY8C20436-24LQXI  | 0-127                                    | 0-63                           | 63             |

| *** CY8C20446-24LQXI  | 0-127                                    | 0-127                          | 127            |

| CY8C20446H-24LQXI     | 0-127                                    | 0-127                          | 127            |

| *** CY8C20466-24LQXI  | 0-127                                    | 0-255                          | 255            |

| *** CY8C20496-24LQXI  | 0-127                                    | 0-127                          | 127            |

| *** CY8C20536 -24PVXI | 0-127                                    | 0-63                           | 63             |

| *** CY8C20546 -24PVXI | 0-127                                    | 0-127                          | 127            |

| *** CY8C20566 -24PVXI | 0-127                                    | 0-255                          | 255            |

| *** CY8C20636-24LQXI  | 0-127                                    | 0-63                           | 63             |

| *** CY8C20646-24LQXI  | 0-127                                    | 0-127                          | 127            |

| *** CY8C20666-24LQXI  | 0-127                                    | 0-255                          | 255            |

| CY8CTST200-16LGXI     | 0-127                                    | 0-255                          | 255            |

| CY8CTST200-24LQXI     | 0-127                                    | 0-255                          | 255            |

| CY8CTST200-32LQXI     | 0-127                                    | 0-255                          | 255            |

Table 2-3. Device Address and Block Definitions

| CY8CTST200-48LTXI                          | 0-127 | 0-255 | 255 |

|--------------------------------------------|-------|-------|-----|

| CY8CTST200-48PVXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-00LGXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-16LGXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-24LQXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-32LQXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-48LTXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG200-48PVXI                          | 0-127 | 0-255 | 255 |

| CY8CTMG201-32LQXI                          | 0-127 | 0-127 | 127 |

| CY8CTMG201-48LTXI                          | 0-127 | 0-127 | 127 |

| CY8CTMG201-48PVXI                          | 0-127 | 0-127 | 127 |

| CY8C20066A                                 | 0-127 | 0-255 | 255 |

| *** CY8C20236A-24LKXI                      | 0-127 | 0-63  | 63  |

| *** CY8C20246A-24LKXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20246AS-24LKXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20266A-24LKXI                      | 0-127 | 0-255 | 255 |

| *** CY8C20336A-24LQXI                      | 0-127 | 0-63  | 63  |

| *** CY8C20336AN-24LQXI                     | 0-127 | 0-63  | 63  |

| *** CY8C20346A-24LQXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20346AS-24LQXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20366A-24LQXI                      | 0-127 | 0-255 | 255 |

| *** CY8C20396A-24LQXI                      | 0-127 | 0-255 | 255 |

| *** CY8C20436A-24LQXI                      | 0-127 | 0-63  | 63  |

| *** CY8C20436AN-24LQXI                     | 0-127 | 0-63  | 63  |

| *** CY8C20446A-24LQXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20446AS-24LQXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20446L-24LQXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20466A-24LQXI                      | 0-127 | 0-255 | 255 |

| *** CY8C20466AS-24LQXI                     | 0-127 | 0-255 | 255 |

| *** CY8C20466L-24LQXI                      | 0-127 | 0-255 | 255 |

| *** CY8C20496A-24LQXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20496L-24LQXI                      | 0-127 | 0-127 | 127 |

| *** CY8C20536A -24PVXI                     | 0-127 | 0-63  | 63  |

| *** CY8C20546A -24PVXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20546L -24PVXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20566A -24PVXI                     | 0-127 | 0-255 | 255 |

| *** CY8C20566L -24PVXI                     | 0-127 | 0-255 | 255 |

| *** CY8C20636A-24LTXI<br>CY8C20636A-24LQXI | 0-127 | 0-63  | 63  |

| *** CY8C20636AN-24LTXI                     | 0-127 | 0-63  | 63  |

| *** CY8C20646A-24LTXI<br>CY8C20646A-24LQXI | 0-127 | 0-127 | 127 |

| *** CY8C20646AS-24LTXI                     | 0-127 | 0-127 | 127 |

| *** CY8C20646L-24LTXI<br>CY8C20646L-24LQXI | 0-127 | 0-127 | 127 |

Table 2-3. Device Address and Block Definitions

| *** CY8C20666A-24LTXI<br>CY8C20666A-24LQXI | 0-127 | 0-255 | 255 |

|--------------------------------------------|-------|-------|-----|

| *** CY8C20666AS-24LTXI                     | 0-127 | 0-255 | 255 |

| *** CY8C20666L-24LTXI                      | 0-127 | 0-255 | 255 |

| CY8C20666L-24LQXI                          |       |       |     |

| *** CY8C20746A 24FDXC                      | 0-127 | 0-127 | 127 |

| *** CY8C20766A 24FDXC                      | 0-127 | 0-255 | 255 |

| CY8CTST200A-16LGXI                         | 0-127 | 0-255 | 255 |

| CY8CTST200A-24LQXI                         | 0-127 | 0-255 | 255 |

| CY8CTST200A-32LQXI                         | 0-127 | 0-255 | 255 |

| CY8CTST200A-48LTXI                         | 0-127 | 0-255 | 255 |

| CY8CTST200A-48PVXI                         | 0-127 | 0-255 | 255 |

| CY8CTST241-LQI-01                          | 0-127 | 0-255 | 255 |

| CY8CTST241-LTI-01                          | 0-127 | 0-255 | 255 |

| CP8CTST241-FNC-01                          | 0-127 | 0-255 | 255 |

| CY8CTMG200A-00LGXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG200A-16LGXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG200A-24LQXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG200A-32LQXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG200A-48LTXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG200AH-48LTXI                        | 0-127 | 0-255 | 255 |

| CY8CTMG200A-48PVXI                         | 0-127 | 0-255 | 255 |

| CY8CTMG201A-32LQXI                         | 0-127 | 0-127 | 127 |

| CY8CTMG201A-48LTXI                         | 0-127 | 0-127 | 127 |

| CY8CTMG201A-48PVXI                         | 0-127 | 0-127 | 127 |

| CY8CTMG240-LQI-01                          | 0-127 | 0-255 | 255 |

| CY8CTMG240-LTI-01                          | 0-127 | 0-255 | 255 |

| CP8CTMG240-FNC-01                          | 0-127 | 0-255 | 255 |

| CY8C20237-24SXI                            | 0-127 | 0-63  | 63  |

| CY8C20247-24SXI                            | 0-127 | 0-127 | 127 |

| CY8C20237-24LKXI                           | 0-127 | 0-63  | 63  |

| CY8C20247-24LKXI                           | 0-127 | 0-127 | 127 |

| CY8C20247S-24LKXI                          | 0-127 | 0-127 | 127 |

| CY8C20337-24LQXI                           | 0-127 | 0-63  | 63  |

| CY8C20337AN-24LQXI                         | 0-127 | 0-63  | 63  |

| CY8C20347-24LQXI                           | 0-127 | 0-127 | 127 |

| CY8C20347S-24LQXI                          | 0-127 | 0-127 | 127 |

| CY8C20437-24LQXI                           | 0-127 | 0-63  | 63  |

| CY8C20437AN-24LQXI                         | 0-127 | 0-63  | 63  |

| CY8C20447-24LQXI                           | 0-127 | 0-127 | 127 |

| CY8C20447S-24LQXI                          | 0-127 | 0-127 | 127 |

| CY8C20467-24LQXI                           | 0-127 | 0-255 | 255 |

| CY8C20467S-24LQXI                          | 0-127 | 0-255 | 255 |

| CY8C20637-24LQXI                           | 0-127 | 0-63  | 63  |

| CY8C20637AN-24LQXI                         | 0-127 | 0-63  | 63  |

Table 2-3. Device Address and Block Definitions

| CY8C20647-24LQXI  | 0-127 | 0-127 | 127 |

|-------------------|-------|-------|-----|

| CY8C20647S-24LQXI | 0-127 | 0-127 | 127 |

| CY8C20667-24LQXI  | 0-127 | 0-255 | 255 |

| CY8C20667S-24LQXI | 0-127 | 0-255 | 255 |

| CY8C20747-24FDXC  | 0-127 | 0-127 | 127 |

| CY8C20767-24FDXC  | 0-127 | 0-255 | 255 |

# A. Programming Mnemonics for CY8C20045, CY8C20055, CY8C20xx6, CY8C20xx7, CY7C643xx, and CY7C604xx

## A.1 Bit Streams for Mnemonics

(**Note** Use caution when copying these bit streams from Adobe Reader. Issues have been seen where bits are dropped during the Copy and Paste process. The bit streams below have been organized into 66-bit chunks to help prevent this problem.)

```

ID-SETUP-1

ID-SETUP-2

1101111111100010010110

SET-BLOCK-NUM

10011111010dddddddd111

dddddddd is block number.

```

CHECKSUM-SETUP

#### READ-CHECKSUM

10111111001ZZDDDDDDDD1

101111111000zzddddddd1

DDDDDDDD is Device Checksum upper byte (MSB) dddddddd is Device Checksum lower byte (LSB)

#### PROGRAM-AND-VERIFY

## ERASE

#### SECURE

#### READ-SECURITY-SETUP

#### READ-SECURITY-1

aaaaaaa = address (7 bits)

#### READ-SECURITY-2

#### READ-SECURITY-3

aaaaaaa = address (7 bits)

READ-WRITE-SETUP

WRITE-BYTE

1001aaaaaaadddddddd111

aaaaaaa = address (7 bits), dddddddd = data in

READ-ID-WORD (CY8C20066 & CY8C20066A)

10111111000ZZLLLLLLL1101111111001ZZHLLHHLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20236 & CY8C20236A)

10111111000ZZLLLLLLL1101111111001ZZHLHHLLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20246 & CY8C20246A)

READ-ID-WORD (CY8C20266 & CY8C20266A)

10111111000ZZLLLLLLL1101111111001ZZHLLHLHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20336 & CY8C20336A)

READ-ID-WORD (CY8C20336H-24LQXI)

10111111000ZZLLLLHHLL1101111111001ZZHLHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20346 & CY8C20346A)

READ-ID-WORD (CY8C20346H-24LQXI)

101111111000ZZLLLLHHLL1101111111001ZZHLHLHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20366 & CY8C20366A)

10111111000ZZLLLLLLL1101111111001ZZHLLHLHHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20396 & CY8C20396A)

10111111000ZZLLLLLLL1101111111001ZZHLHLHHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20436 & CY8C20436A)

10111111000ZZLLLLLLL1101111111001ZZHLHHLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20446 CY8C20446A)

10111111000ZZLLLLLLL1101111111001ZZHLHLHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20446H-24LQXI)

10111111000ZZLLLLHHLL1101111111001ZZHLHLHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20466 & CY8C20466A)

10111111000ZZLLLLLLL1101111111001ZZHLLHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20496 & CY8C20496A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20536 & CY8C20536A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHLLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20546 & CY8C20546A)

10111111000ZZLLLLLLL1101111111001ZZHLHLHHHL111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20566 & CY8C20566A)

10111111000ZZLLLLLLL1101111111001ZZHLLHHLLH111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20636 & CY8C20636A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20646 & CY8C20646A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20666 & CY8C20666A)

10111111000ZZLLLLLLL1101111111001ZZHLLHHHLL1111111110011ZZLHLHLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20746A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHHHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20766A)

10111111000ZZLLLLLLL1101111111001ZZHLHHHHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C60400)

10111111000ZZLLLLLLL1101111111001ZZHLHLHLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C60413)

10111111000ZZLLLLLLL1101111111001ZZHLHHLHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C60445)

10111111000ZZLLLLLLL1101111111001ZZHLHLLHHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C60455)

10111111000ZZLLLLLLL1101111111001ZZHLHLHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C60456)

101111111000ZZLLLLLLL1101111111001ZZHLHLHLLH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C64300)

101111111000ZZLLLLLLL1101111111001ZZHLHLLHHL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (cy7c64315)

10111111000ZZLLLLLLL1101111111001ZZHLHLLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (cy7c64316)

101111111000ZZLLLLLLL1101111111001ZZHLHLLLLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY7C64343)

101111111000ZZLLLLLLL1101111111001ZZHLHHLHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (cy7c64345)

10111111000ZZLLLLLLL1101111111001ZZHLHLLLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (cy7c64355)

10111111000ZZLLLLLLL1101111111001ZZHLHLLLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (cy7c64356)

READ-ID-WORD (CY8CTMG200-00LTXI & CY8CTMG200A-00LTXI)

10111111000ZZLLLLLHHH1101111111001ZZHLLHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200-16LGXI & CY8CTMG200A-16LGXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200-24LQXI & CY8CTMG200A-24LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200-32LQXI & CY8CTMG200A-32LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLHHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200-48LTXI & CY8CTMG200A-48LTXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLHHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200AH-48LTXI)

10111111000ZZLLLLHHHH1101111111001ZZLHHLHHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG240-LQI-01)

READ-ID-WORD (CY8CTMG240-LTI-01)

10111111000ZZLLLLLHHH1101111111001ZZHHLHLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CP8CTMG240-FNC-01)

10111111000ZZLLLLLHHH1101111111001ZZHLHHHHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG200-48PVXI & CY8CTMG200A-48PVXI)

10111111000ZZLLLLLHHH1101111111001ZZLLLHHHLL1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLH1

READ-ID-WORD (CY8CTST200-16LGXI & CY8CTST200A-16LGXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLHHLL1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST200-24LQXI & CY8CTST200A-24LQXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLHHLH1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST200-32LQXI & CY8CTST200A-32LQXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLHHHL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST200-48LTXI & CY8CTST200A-48LTXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLHHHH1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST200-48PVXI & CY8CTST200A-48PVXI)

10111111000ZZLLLLLHHL1101111111001ZZLLLHHHLL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLH1

READ-ID-WORD (CY8CTST241-LQI-01)

10111111000ZZLLLLLHHL1101111111001ZZHHLHLHHL111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST241-LTI-01)

10111111000ZZLLLLLHHL1101111111001ZZHHLHLHHH111111110011ZZLHLHLLHL

111111110000ZZLLHLLLH1

READ-ID-WORD (CP8CTST241-FNC-01)

10111111000ZZLLLLLHHL1101111111001ZZHLHHHHHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG201-16LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLLLH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLH1

READ-ID-WORD (CY8CTMG201-24LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLLLHL1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG201-32LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLLLHH111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG201-48LTXI & CY8CTMG201A-48LTXI)

101111111000ZZLLLLLHHH1101111111001ZZLHHLLHL1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLH1

READ-ID-WORD (CY8CTMG201-48PVXI & CY8CTMG201A-48PVXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLLHLH111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLH1

READ-ID-WORD (CP8CTST242-FNC-01)

101111111000ZZLLLLLHHL1101111111001ZZHLHHHHHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20246AS-24LKXI)

10111111000ZZLLLLHLHH1101111111001ZZHLHLHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20336AN-24LQXI)

10111111000ZZLLLLLLL1101111111001ZZHHLHHLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20346AS-24LQXI)

101111111000ZZLLLLHLHH1101111111001ZZHLHLHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20436AN-24LQXI)

10111111000ZZLLLLLLL1101111111001ZZHHLHHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20446AS-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZHLHLHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20446L-24LQXI)

10111111000ZZLLLLLLHH1101111111001ZZHLHLHHLH111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20466AS-24LQXI)

101111111000ZZLLLLHLHH1101111111001ZZHLLHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20466L-24LQXI)

101111111000ZZLLLLLLHH1101111111001ZZHLLHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20496L-24LQXI)

10111111000ZZLLLLLLHH1101111111001ZZHLHHHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20546L-24PVXI)

101111111000ZZLLLLLLHH1101111111001ZZHLHLHHHL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20566L-24PVXI)

10111111000ZZLLLLLLHH1101111111001ZZHLLHHLLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20636AN-24LTXI)

10111111000ZZLLLLLLL1101111111001ZZHHLHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20646AS-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZHLHHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20646AS-24LTXI)

10111111000ZZLLLLHLHH1101111111001ZZHLHHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

\*\*\* READ-ID-WORD (CY8C20646L-24LTXI & CY8C20646L-24LQXI)

READ-ID-WORD (CY8C20666AS-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZHLLHHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20666AS-24LTXI)

10111111000ZZLLLLHLHH1101111111001ZZHLLHHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

\*\*\* READ-ID-WORD (CY8C20666L-24LTXI CY8C20666L-24LOXI)

10111111000ZZLLLLLLHH1101111111001ZZHLLHHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG201-16LGXI)

101111111000ZZLLLLLHHH1101111111001ZZLHHLLLLH1111111110011ZZLHLHLLHL

1111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTMG201-24LQXI)

10111111000ZZLLLLLHHH1101111111001ZZLHHLLLHL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST201-16LGXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLLLLH111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST201-24LQXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLLLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST201-32LQXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLLLHH111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST201-48LTXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST201-48PVXI)

10111111000ZZLLLLLHHL1101111111001ZZLHHLLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST242-LQI-01)

10111111000ZZLLLLLHHL1101111111001ZZHLLHHLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8CTST242-LTI-01)

101111111000ZZLLLLLHHL1101111111001ZZHLLHHHLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20237-24LKXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLLLHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20237-24SXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20247-24LKXI)

10111111000ZZLLLLLLLH1101111111001ZZLHLLLLHH111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20247S-24LKXI)

101111111000ZZLLLLHLHH1101111111001ZZLHLLLLHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20247-24SXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLLLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20337-24LQXI)

10111111000ZZLLLLLLLH110111111001ZZLHLLLHLL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20337AN-24LQXI)

10111111000ZZLLLLLLH1101111111001ZZLHLHLLL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20347-24LOXI)

10111111000ZZLLLLLLLH1101111111001ZZLHLLLHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20347S-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZLHLLLHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20437-24LQXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLLHHL111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20437AN-24LQXI)

10111111000ZZLLLLLLLH1101111111001ZZLHLHLLLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20447-24LQXI)

101111111000ZZLLLLLLH1101111111001ZZLHLLLHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20447S-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZLHLLLHHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20467-24LQXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLHLL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20467S-24LOXI)

READ-ID-WORD (CY8C20637-24LQXI)

10111111000ZZLLLLLLLH1101111111001ZZLHLLHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20637AN-24LQXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLHHHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20647-24LQXI)

10111111000ZZLLLLLLLH1101111111001ZZLHLLHLH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20647S-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZLHLLHLHL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20667-24LOXI)

10111111000ZZLLLLLLH1101111111001ZZLHLLHLHH1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20667S-24LQXI)

10111111000ZZLLLLHLHH1101111111001ZZLHLLHLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20747-24FDXC)

10111111000ZZLLLLLLH1101111111001ZZLHLLHHLL1111111110011ZZLHLHLLHL

111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20767-24FDXC)

10111111000ZZLLLLLLH1101111111001ZZLHLLHHLH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20045-24LKXI)

10111111000ZZLLLLLLH1101111111001ZZHLHLLHH1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20055-24LKXI)

10111111000ZZLLLLLLLH110111111001ZZLHHHLLLL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

READ-ID-WORD (CY8C20055-24SXI)

10111111000ZZLLLLLLH1101111111001ZZHHLLHHHL1111111110011ZZLHLHLLHL 111111110000ZZLLHLLLLH1

VERIFY-SETUP

READ-STATUS

10111111000ZZDDDDDDDD1

DDDDDDDD = data out

READ-BYTE

1011aaaaaaaZZDDDDDDDD1

aaaaaaa = address (7 bits), DDDDDDDD = data out

SYNC-ENABLE

SYNC-DISABLE

Notes: 1=logic high=Vihp

0=logic low=Vilp Z=High Z (floating)

D=data read from device (Most Significant Bit of the binary data comes out first)

d=data applied to the device (MSB of the binary data goes in first)

a=address applied to the device (MSB of the binary data goes in first)

H=High data read from the device (Vout=Vohv)

L=Low data read from the device (Vout=Volv)

If the programmer has delays between executing the different Mnemonics, SDATA should be

HighZ (floating).

### **Other Mnemonics**

WAIT-AND-POLL:

After the mnemonic bit stream is sent, the SDATA pin typically takes 1 uS to drift low. (The SDATA pin drifts low to Vilp by the device's internal pull down resistor.) A minimum delay of 416 ns (or ten 12-MHz CPU clock cycles) is needed before the SDATA pin is pulled high. Clocking is needed in order for SDATA to transition from low to high. At least one SCLK should be sent, but more may be sent before SDATA to transition from low to high. This is accomplished through IOWC at the end of the mnemonics. The target device pulls SDATA high when the mnemonic begins executing. No SCLKs are required while SDATA is high.

The device outputs a logic high on the SDATA pin while the mnemonic is executing and then switches to a logic low when the mnemonic finishes. The programmer should Wait & Poll the SDATA pin for the high-to-low transition. The maximum SDATA high time is 200 ms.

Once the transition to low is observed, the programmer should apply a bit stream of 0000000000 000000000 0000000000 (30 zero bits) to the SDATA pin of the device and then continue to the next mnemonic.